# **User Guide**

# **R600-Family Instruction Set Architecture**

January 2009

Revision 0.37

© 2009 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, ATI, the ATI logo, Radeon, FireStream, FireGL, Catalyst, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Microsoft, Windows, and Windows Vista are registered trademarks of Microsoft Corporation in the U.S. and/or other jurisdictions. Other names are for informational purposes only and may be trademarks of their respective owners.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

Advanced Micro Devices, Inc. One AMD Place P.O. Box 3453 Sunnyvale, CA 94088-3453 www.amd.com

# Contents

### Contents

#### Preface

| Chapter 1 | In                             | troduction                                              |      |  |  |

|-----------|--------------------------------|---------------------------------------------------------|------|--|--|

| Chapter 2 | Program Organization and State |                                                         |      |  |  |

|           | 2.1                            | Program Types                                           | 2-1  |  |  |

|           |                                | 2.1.1 Data Flows                                        | 2-2  |  |  |

|           |                                | 2.1.2 Geometry Program Absent                           | 2-2  |  |  |

|           |                                | 2.1.3 Geometry Shader Present                           | 2-3  |  |  |

|           | 2.2                            | Instruction Terminology                                 |      |  |  |

|           | 2.3                            | Control Flow and Clauses                                |      |  |  |

|           | 2.4                            | Instruction Types and Grouping                          |      |  |  |

|           | 2.5                            | Program State                                           |      |  |  |

| Chapter 3 | C                              | ontrol Flow (CF) Programs                               |      |  |  |

|           | 3.1                            | CF Microcode Encoding                                   |      |  |  |

|           | 3.2                            | Summary of Fields in CF Microcode Formats               |      |  |  |

|           | 3.3                            | Clause-Initiation Instructions                          |      |  |  |

|           |                                | 3.3.1 ALU Clause Initiation                             | 3-6  |  |  |

|           |                                | 3.3.2 Vertex-Fetch Clause Initiation and Execution      | 3-6  |  |  |

|           |                                | 3.3.3 Texture-Fetch Clause Initiation and Execution     | 3-6  |  |  |

|           | 3.4                            | Import and Export Instructions                          |      |  |  |

|           |                                | 3.4.1 Normal Exports (Pixel, Position, Parameter Cache) |      |  |  |

|           |                                | 3.4.2 Memory Reads and Writes                           | 3-8  |  |  |

|           | 3.5                            | Synchronization with Other Blocks                       |      |  |  |

|           | 3.6                            | Conditional Execution                                   | 3-10 |  |  |

|           |                                | 3.6.1 Valid and Active Masks                            |      |  |  |

|           |                                | 3.6.2 WHOLE_QUAD_MODE and VALID_PIXEL_MODE              |      |  |  |

|           |                                | 3.6.3 The Condition (COND) Field                        |      |  |  |

|           |                                | 3.6.4 Computation of Condition Tests                    |      |  |  |

|           |                                | 3.6.5 Stack Allocation                                  | 3-14 |  |  |

|           | 3.7                            | Branch and Loop Instructions                            |      |  |  |

|           |                                | 3.7.1 ADDR Field                                        |      |  |  |

|           |                                | 3.7.2 Stack Operations and Jumps                        | 3-17 |  |  |

|           |      | 3.7.3 DirectX9 Lo           | oops                                          | 3-18 |

|-----------|------|-----------------------------|-----------------------------------------------|------|

|           |      | 3.7.4 DirectX10 L           | Loops                                         | 3-19 |

|           |      | 3.7.5 Repeat Loo            | ops                                           | 3-19 |

|           |      | 3.7.6 Subroutines           | S                                             | 3-19 |

|           |      | 3.7.7 ALU Branc             | h-Loop Instructions                           | 3-20 |

| Chapter 4 | Α    | U Clauses                   |                                               |      |

|           | 4.1  | ALU Microcode Form          | mats                                          | 4-1  |

|           | 4.2  | Overview of ALU Feat        | atures                                        | 4-1  |

|           | 4.3  | ALU Instruction Slot        | ts and Instruction Groups                     |      |

|           | 4.4  | Assignment to ALU.          | [X,Y,Z,W] and ALU.Trans Units                 |      |

|           | 4.5  | OP2 and OP3 Microo          | code Formats                                  | 4-5  |

|           | 4.6  | GPRs and Constants          | S                                             |      |

|           |      | 4.6.1 Relative Ad           | ddressing                                     | 4-6  |

|           |      | 4.6.2 Previous Ve           | ector (PV) and Previous Scalar (PS) Registers | 4-7  |

|           |      | 4.6.3 Out-of-Bou            | nds Addresses                                 | 4-7  |

|           |      | 4.6.4 ALU Consta            | ants                                          | 4-8  |

|           | 4.7  | Scalar Operands             |                                               |      |

|           |      | 4.7.1 Source Add            | dresses                                       | 4-9  |

|           |      | 4.7.2 Input Modif           | fiers                                         | 4-10 |

|           |      | 4.7.3 Data Flow .           |                                               | 4-10 |

|           |      | 4.7.4 GPR Read              | Port Restrictions                             | 4-11 |

|           |      | 4.7.5 Constant R            | Register Read Port Restrictions               | 4-11 |

|           |      | 4.7.6 Literal Con           | stant Restrictions                            | 4-12 |

|           |      | 4.7.7 Cycle Restr           | rictions for ALU.[X,Y,Z,W] Units              | 4-12 |

|           |      | 4.7.8 Cycle Restr           | rictions for ALU.Trans                        | 4-14 |

|           |      | 4.7.9 Read-Port             | Mapping Algorithm                             | 4-16 |

|           | 4.8  | ALU Instructions            |                                               | 4-19 |

|           |      |                             | s for All ALU Units                           |      |

|           |      | 4.8.2 KILL and P            | PRED_SET* Instruction Restrictions            | 4-22 |

|           |      |                             | s for ALU.[X,Y,Z,W] Units Only                |      |

|           |      |                             | s for ALU.Trans Units Only                    |      |

|           | 4.9  |                             |                                               |      |

|           |      |                             | difiers                                       |      |

|           |      |                             | n Registers                                   |      |

|           |      |                             | Dutput                                        |      |

|           |      |                             | iction                                        |      |

|           |      |                             | ructions                                      |      |

|           | 4.10 | Predication and Brai        | nch Counters                                  | 4-27 |

|           | 4.11 | -                           | Dependencies                                  |      |

|           | 4.12 | <b>Double-Precision Flo</b> | oating-Point Operations                       | 4-29 |

| Chapter 5  | V    | /ertex-Fetch Clauses                 |      |

|------------|------|--------------------------------------|------|

|            | 5.1  | Clause Construction                  |      |

|            | 5.2  | Vertex-Fetch Microcode Formats       |      |

| Chapter 6  | т    | exture-Fetch Clauses                 |      |

|            | 6.1  | Texture-Fetch Microcode Formats      | 6-1  |

|            | 6.2  | Constant-Fetch Operations            |      |

|            | 6.3  | FETCH_WHOLE_QUAD and WHOLE_QUAD_MODE |      |

| Chapter 7  | h    | nstruction Set                       |      |

|            | 7.1  | Control Flow (CF) Instructions       |      |

|            | 7.2  | ALU Instructions                     | 7-41 |

|            | 7.3  | Vertex-Fetch Instructions            |      |

|            | 7.4  | Texture-Fetch Instructions           |      |

| Chapter 8  | N    | Aicrocode Formats                    |      |

|            | 8.1  | Control Flow (CF) Instructions       |      |

|            | 8.2  | ALU Instructions                     |      |

|            | 8.3  | Vertex-Fetch Instructions            |      |

|            | 8.4  | Texture-Fetch Instructions           |      |

| Appendix / | A lı | nstruction Table                     |      |

## **Glossary of Terms**

Index

## Figures

| 1.1 | R600-Family Block Diagram                   | 1-1 |

|-----|---------------------------------------------|-----|

| 1.2 | Programmer's View of R600 Dataflow          | 1-3 |

| 4.1 | ALU Microcode Format Pair                   | 4-1 |

| 4.2 | Organization of ALU Vector Elements in GPRs | 4-1 |

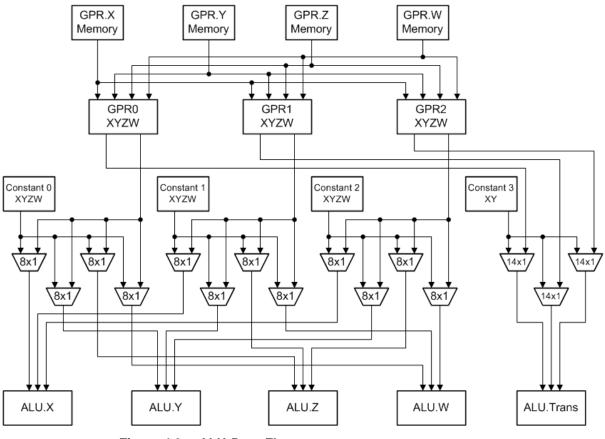

| 4.3 | ALU Data Flow                               |     |

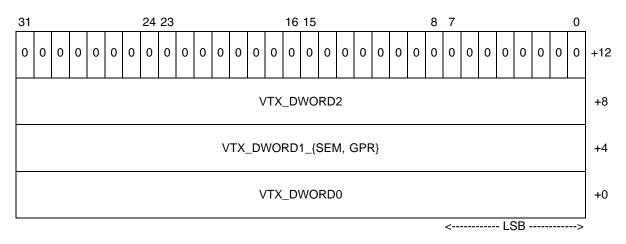

| 5.1 | Vertex-Fetch Microcode-Format 4-Tuple       | 5-2 |

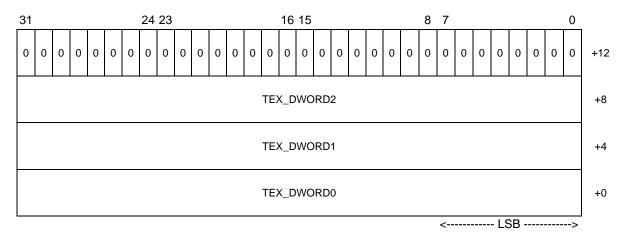

| 6.1 | Texture-Fetch Microcode-Format 4-Tuple      | 6-2 |

## Tables

| 2.1  | Order of Program Execution (Geometry Program Absent)             | 2-2   |

|------|------------------------------------------------------------------|-------|

| 2.2  | Order of Program Execution (Geometry Program Present)            | 2-3   |

| 2.3  | Basic Instruction-Related Terms                                  | 2-4   |

| 2.4  | Flow of a Typical Program                                        | 2-6   |

| 2.5  | Control-Flow State                                               | 2-9   |

| 2.6  | ALU State                                                        | 2-10  |

| 2.7  | Vertex-Fetch State                                               | 2-11  |

| 2.8  | Texture-Fetch and Constant-Fetch State                           | 2-11  |

| 3.1  | CF Microcode Field Summary                                       | 3-4   |

| 3.2  | Types of Clause-Initiation Instructions                          | 3-5   |

| 3.3  | Possible ARRAY_BASE Values                                       | 3-8   |

| 3.4  | Condition Tests                                                  | 3-13  |

| 3.5  | Stack Subentries                                                 | 3-14  |

| 3.6  | Stack Space Required for Flow-Control Instructions               | 3-15  |

| 3.7  | Branch-Loop Instructions                                         | 3-15  |

| 4.1  | Instruction Slots in an Instruction Group                        | 4-3   |

| 4.2  | Index for Relative Addressing                                    | 4-6   |

| 4.3  | Example Function's Loading Cycle                                 | 4-17  |

| 4.4  | ALU Instructions (ALU.[X,Y,Z,W] and ALU.Trans Units)             | 4-19  |

| 4.5  | ALU Instructions (ALU.[X,Y,Z,W] Units Only)                      | 4-22  |

| 4.6  | ALU Instructions (ALU.Trans Units Only)                          | 4-24  |

| 7.1  | Result of ADD_64 Instruction                                     | 7-42  |

| 7.2  | Result of FLT32_TO_FLT64 Instruction                             |       |

| 7.3  | Result of FLT64_TO_FLT32 Instruction                             | 7-64  |

| 7.4  | Result of FRACT_64 Instruction                                   | 7-67  |

| 7.5  | Result of FREXP_64 Instruction                                   | 7-69  |

| 7.6  | Result of LDEXP_64 Instruction                                   | 7-76  |

| 7.7  | Result of MUL_64 Instruction                                     | 7-96  |

| 7.8  | Result of MULADD_64 Instruction (IEEE Single-Precision Multiply) | 7-104 |

| 7.9  | Result of MULADD_64 Instruction (IEEE Add)                       | 7-105 |

| 7.10 | Result of PRED_SETE_64 Instruction                               | 7-126 |

| 7.11 | Result of PRED_SETGE_64 Instruction                              | 7-132 |

| 7.12 | Result of PRED_SETGT_64 Instruction                              | 7-139 |

| 8.1  | Summary of Microcode Formats                                     | 8-1   |

| A.1  | Summary of Instruction                                           | A-1   |

# Preface

## About This Document

This document describes the instruction set architecture (ISA) native to the R600 family of processors. It defines the instructions and formats accessible to programmers and compilers.

The document serves two purposes.

- It specifies the microcode (including the format of each type of microcode instruction) and the relevant program state (including how the program state interacts with the microcode). Some microcode fields are mutually dependent; not all possible settings for all fields are legal. This document specifies the valid combinations.

- It provides the programming guidelines for compiler writers to maximize processor performance.

For an understanding of the software environment in which the R600 family of processors operate, see the *ATI CTM Guide, Technical Reference Manual*, which describes the interface by which a host controls an R600-family processor. In this document, the term "R600" refers the entire family of R600 processors.

## Audience

This document is intended for programmers writing application and system software, including operating systems, compilers, loaders, linkers, device drivers, and system utilities. It assumes that programmers are writing compute-intensive parallel applications (streaming applications) and assumes an understanding of requisite programming practices.

## Organization

This document begins with an overview of the R600 family of processors' hardware and programming environment (Chapter 1). Chapter 2 describes the organization of an R600-family program and the program state that is maintained. Chapter 3 describes the control flow (CF) programs. Chapter 4 the ALU clauses. Chapter 5 describes the vertex-fetch clauses. Chapter 6 describes the texture-fetch clauses. Chapter 7 describes instruction details, first by broad categories, and following this, in alphabetic order by mnemonic. Finally, Chapter 8 provides a detailed specification of each microcode format.

# Registers

The following list shows the names are used to refer either to a register or to the contents of that register.

| GPRs       | General-purpose registers. There are 128 GPRs, each one 128 bits wide, organized as four 32-bit values. |

|------------|---------------------------------------------------------------------------------------------------------|

| CRs        | Constant registers. There are 512 CRs, each one 128 bits wide, organized as four 32-bit values.         |

| AR         | Address register.                                                                                       |

| loop index | A register initialized by software and incremented by hardware on each iteration of a loop.             |

# **Endian Order**

The R600-family architecture addresses memory and registers using little-endian byte-ordering and bit-ordering. Multi-byte values are stored with their least-significant (low-order) byte (LSB) at the lowest byte address, and they are illustrated with their LSB at the right side. Byte values are stored with their least-significant (low-order) bit (lsb) at the lowest bit address, and they are illustrated with their least-significant (low-order) bit (lsb) at the lowest bit address, and they are illustrated with their least-significant (low-order) bit (lsb) at the lowest bit address, and they are illustrated with their least-significant (low-order) bit (lsb) at the lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address, and they are illustrated with their lowest bit address.

# Conventions

The following conventions are used in this document.

| mono-spaced font          | A filename, file path, or code.                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------|

| *                         | Any number of alphanumeric characters in the name of a code format, parameter, or instruction.                   |

| < >                       | Angle brackets denote streams.                                                                                   |

| [1,2)                     | A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2). |

| [1,2]                     | A range that includes both the left-most and right-most values (in this case, 1 and 2).                          |

| {x   y}                   | One of the multiple options listed. In this case, x or y.                                                        |

| 0.0                       | A single-precision (32-bit) floating-point value.                                                                |

| 1011b                     | A binary value, in this example a 4-bit value.                                                                   |

| 7:4                       | A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.                                      |

| italicized word or phrase | The first use of a term or concept basic to the understanding of stream computing.                               |

# **Related Documents**

- CTM HAL Programming Guide. Published by AMD.

- Intermediate Language (IL) Reference Manual. Published by AMD.

- OpenGL Programming Guide, at http://www.glprogramming.com/red/

- Microsoft DirectX Reference Website, at http://msdn.microsoft.com/archive/default.asp?url=/archive/en-us/ directx9\_c\_Summer\_04/directx/graphics/reference/reference.asp

- GPGPU: http://www.gpgpu.org

## **Contact Information**

To submit questions or comments concerning this document, contact our technical documentation staff at: streamcomputing@amd.com.

For questions concerning ATI Stream products, please email: streamcomputing@amd.com.

For questions about developing with ATI Stream, please email: streamdeveloper@amd.com.

You can learn more about ATI Stream at: http://www.amd.com/stream.

We also have a growing community of ATI Stream users. Come visit us at the ATI Stream Developer Forum (http://www.amd.com/streamdevforum) to find out what applications other users are trying on their ATI Stream products.

# Chapter 1 Introduction

The R600-family of processors implements a parallel microarchitecture that provides an excellent platform not only for computer graphics applications but also for general-purpose streaming applications. Any data-intensive application that can be mapped to a 2D matrix is a candidate for running on an R600-family processor.

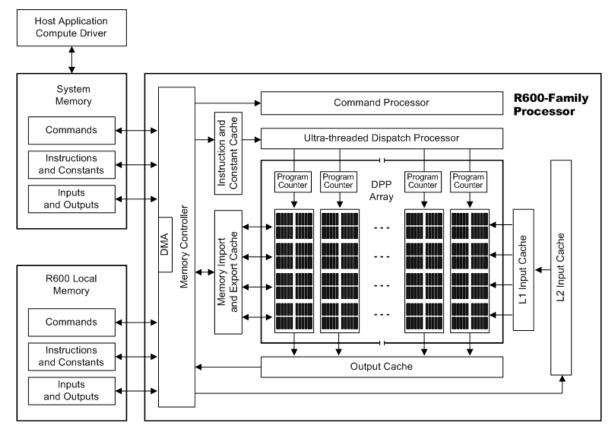

Figure 1.1 shows a block diagram of the R600-family processors.

Figure 1.1 R600-Family Block Diagram

It includes a data-parallel processor (DPP) array, a command processor, a memory controller, and other logic (not shown). The R600 command processor reads commands that the host has written to memory-mapped R600 registers in the system-memory address space. The command processor sends hardware-generated interrupts to the host when the command is completed. The R600 memory controller has direct access to all of R600 local memory and the host-

specified areas of system memory. To satisfy read and write requests, the memory controller performs the functions of a direct-memory access (DMA) controller, including computing memory-address offsets based on the format of the requested data in memory.

A host application cannot write to R600 local memory directly, but it can command the R600 to copy programs and data between system memory and R600 memory. A complete application for the R600 includes two parts:

- a program running on the host processor, and

- programs, called kernels, running on the R600 processor.

The R600 programs are controlled by host commands, which

- set R600-internal base-address and other configuration registers,

- specify the data domain on which the R600 is to operate,

- invalidate and flush caches on the R600, and

- cause the R600 to begin execution of a program.

The R600 driver program runs on the host.

The DPP array is the heart of the R600 processor. The array is organized as a set of SIMD pipelines, each independent from the others, that operate in parallel on streams of floating-point or integer data. The SIMD pipelines can process data or, through the memory controller, transfer data to, or from, memory. Computation in a SIMD pipeline can be made conditional. Outputs written to memory can also be made conditional. R600 software stores data to memory by first allocating space in a memory buffer, then exporting data from GPRs to that buffer. The R600 export facility is also used to import (read) data from memory.

Host commands request a SIMD pipeline to execute a kernel by passing it:

- an identifier pair (x, y),

- a conditional value, and

- the location in memory of the kernel code.

When it receives a request, the SIMD pipeline loads instructions and data from memory, begins execution, and continues until the end of the kernel. As kernels are running, the R600 hardware automatically fetches instructions and data from memory into on-chip caches; R600 software plays no role in this. R600 software also can load data from off-chip memory into on-chip GPRs and caches.

Conceptually, each SIMD pipeline maintains a separate interface to memory, consisting of index pairs and a field identifying the type of request (program instruction, floating-point constant, integer constant, boolean constant, input read, or output write). The index pairs for inputs, outputs, and constants are specified by the requesting R600 instructions from the hardware-maintained program state in the pipelines.

R600 programs do not support exceptions, interrupts, errors, or any other events that can interrupt its pipeline operation. In particular, it does not support IEEE floating-point exceptions. The interrupts shown in Figure 1.1 from the command processor to the host represent hardware-generated interrupts for signalling command-completion and related management functions.

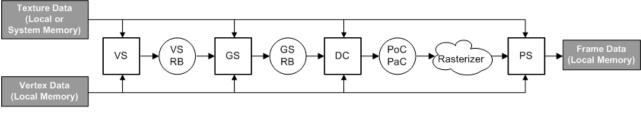

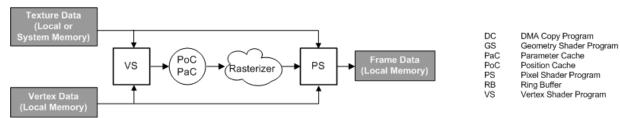

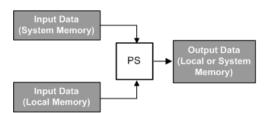

Figure 1.2 shows a programmer's view of the dataflow for three versions of an R600 application. The top version (a) is a graphics application that includes a geometry shader program and a DMA copy program. The middle version (b) is a graphics application without a geometry shader and DMA copy program. The bottom version (c) is a general-purpose application. The square blocks represent programs running on the DPP array. The circles and clouds represent non-programmable hardware functions. For graphics applications, each block in the chain processes a particular kind of data and passes its result on to the next block. For general-purpose applications, only one processing block performs all computation.

(a) Pipeline for Graphics Application With Geometry Shader (GS)

(b) Pipeline for Graphics Application Without Geometry Shader (GS)

(c) Pipeline for General-Purpose Computing Program

#### Figure 1.2 Programmer's View of R600 Dataflow

The dataflow sequence starts by reading 2D vertices, 2D textures, or other 2D data from local R600 memory or system memory; it ends by writing 2D pixels or

other 2D data results to local R600 memory. The R600 processor hides memory latency by keeping track of potentially hundreds of threads in different stages of execution, and by overlapping compute operations with memory-access operations.

# Chapter 2 Program Organization and State

R600 programs consist of control-flow (CF), ALU, texture-fetch, and vertex-fetch instructions, which are described in this manual. ALU instructions can have up to three source operands and one destination operand. The instructions operate on 32-bit IEEE floating-point values and signed or unsigned integers. The execution of some instructions cause predicate bits to be written that affect subsequent instructions. Graphics programs typically use vertex-fetch and texture-fetch instructions for data loads, whereas general-computing applications typically use texture-fetch instructions for data loads.

## 2.1 Program Types

The following program types are commonly run on the R600 (see Figure 1.2, on page 1-3,):

- Vertex Shader (VS)—Reads vertices, processes them. Depending on whether a geometry shader (GS) is active, it outputs the results to either a VS ring buffer, or the parameter cache and position buffer. It does not introduce new primitives. When a GS is active, a vertex shader is a type of *Export Shader (ES)*. A vertex shader can invoke a *Fetch Subroutine (FS)*, which is a special global program for fetching vertex data that is treated, for execution purposes, as part of the vertex program. The FS provides driver independence between the process of fetching data required by a VS, and the VS itself.

- Geometry Shader (GS)—Reads primitives from the VS ring buffer, and, for each input primitive, writes one or more primitives as output to the GS ring buffer. This program type is optional; when active, it requires a DMA copy (DC) program to be active. The GS simultaneously reads up to six vertices from an off-chip memory buffer created by the VS; it outputs a variable number of primitives to a second memory buffer.

- *DMA Copy (DC)*—Transfers data from the GS ring buffer into the parameter cache and position buffer. It is required for systems running a geometry shader.

- Pixel Shader (PS) or Fragment Shader—This type of program:

- reads data from the position buffer, parameter cache, and vertex geometry translator (VGT),

- processes individual pixel quads (four pixel-data elements arranged in a 2-by-2 array), and

writes output to up to eight local-memory buffers, called multiple render targets (MRTs), which can include one or more frame buffers.

All program types accept the same instruction types, and all of the program types can run on any of the available DPP-array pipelines that support these programs; however, each kernel type has certain restrictions, which are described with that type.

## 2.1.1 Data Flows

The host can initialize the R600 to run in one of two configurations—with or without a geometry shader program and a DMA copy program. Figure 1.2, on page 1-3, illustrates the processing order. Each type of flow is described in the following subsections.

## 2.1.2 Geometry Program Absent

Table 2.1 shows the order in which programs run when a geometry program is absent.

| Table 2.1 | Order of Program  | Execution | (Geometry | Program A     | bsent) |

|-----------|-------------------|-----------|-----------|---------------|--------|

|           | oraci or i rogram | Excoution |           | i i ografii A | Sound  |

| Mnemonic | Program Type  | Operates On | Inputs Come From                                                        | Outputs Go To                        |

|----------|---------------|-------------|-------------------------------------------------------------------------|--------------------------------------|

| VS       | Vertex Shader | Vertices    | Vertex memory.                                                          | Parameter cache and position buffer. |

| PS       | Pixel Shader  | Pixels      | Positions cache, parameter cache, and vertex geometry translator (VGT). | Local or system<br>memory.           |

This processing configuration consists of the following steps.

- 1. The VS program sends a pointer to a buffer in local memory containing up to 64 vertex indices.

- 2. The R600 hardware groups the vectors for these vertices in its input buffers (remote memory).

- 3. When all vertices are ready to be processed, the R600 allocates GPRs and thread space for the processing of each of the 64 vertices, based on compiler-provided sizes.

- 4. The VS program calls the fetch subroutine (FS) program, which fetches vertex data into GPRs and returns control to the VS program.

- 5. The transform, lighting, and other parts of the VS program run.

- 6. The VS program allocates space in the position buffer and exports the vertex positions (XYZW).

- 7. The VS program allocates parameter-cache and position-buffer space and exports parameters and positions for each vertex.

- 8. The VS program exits, and the R600 deallocates its GPR space.

- 9. When the VS program completes, the pixel shader (PS) program begins.

- 10. The R600 hardware assembles primitives from data in the position buffer and the vertex geometry translator (VGT), performs scan conversion and final pixel interpolation, and loads these values into GPRs.

- 11. The PS program then runs for each pixel.

- 12. The program exports data to a frame buffer, and the R600 deallocates its GPR space.

### 2.1.3 Geometry Shader Present

Table 2.2 shows the order in which programs run when a geometry program is present.

Table 2.2

Order of Program Execution (Geometry Program Present)

| Mnemonic | Program Type    | Operates On | Inputs Come From                                                              | Outputs Go To                            |

|----------|-----------------|-------------|-------------------------------------------------------------------------------|------------------------------------------|

| VS       | Vertex Shader   | Vertices    | Vertex memory.                                                                | VS ring buffer.                          |

| GS       | Geometry Shader | Primitives  | VS ring buffer.                                                               | GS ring buffer.                          |

| DC       | DMA Copy        | Any Data    | GS ring buffer.                                                               | Parameter cache or posi-<br>tion buffer. |

| PS       | Pixel Shader    | Pixels      | Positions cache, parameter<br>cache, and vertex geometry<br>translator (VGT). | Local or system memory.                  |

This processing configuration consists of the following steps.

- 1. The R600 hardware loads input indices or primitive and vertex IDs from the vertex geometry translator (VGT) into GPRs.

- 2. The VS program fetches the vertex or vertices needed

- 3. The transform, lighting, and other parts of the VS program run.

- 4. The VS program ends by writing vertices out to the VS ring buffer.

- 5. The GS program reads multiple vertices from the VS ring buffer, executes its geometry functions, and outputs one or more vertices per input vertex to the GS ring buffer. The VS program can only write a single vertex per single input; the GS program can write a large number of vertices per single input. Every time a GS program outputs a vertex, it indicates to the vertex VGT that a new vertex has been output (using EMIT\_\* instructions<sup>1</sup>). The VGT counts the total number of vertices created by each GS program. The GS program divides primitive strips by issuing CUT\_VERTEX instructions.

- 6. The GS program ends when all vertices have been output. No position or parameters is exported.

- 7. The DC program reads the vertex data from the GS ring buffer and transfers this data to the parameter cache and position buffer using one of the MEM\* memory export instructions.

<sup>1.</sup> An asterisk (\*) after a mnemonic string indicates that there are additional characters in the string that define variants.

- 8. The DC program exits, and the R600 deallocates the GPR space.

- 9. The PS program runs.

- 10. The R600 assembles primitives from data in the position buffer, parameter cache, and VGT.

- 11. The hardware performs scan conversion and final pixel interpolation, and hardware loads these values into GPRs.

- 12. The PS program runs.

- 13. When the PS program reaches the end of the data, it exports the data to a frame buffer or other render target (up to eight) using EXPORT instructions.

- 14. The program exits upon execution of an EXPORT\_DONE instruction, and the processor deallocates GPR space.

# 2.2 Instruction Terminology

Table 2.3 summarizes some of the instruction-related terms used in this document. The instructions themselves are described in the remaining chapters. Details on each instruction are given in Chapter 7. The register types are described in "Registers," on page xii.

| Term                     | Size (bits) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microcode format         | 32          | One of several encoding formats for all instructions. They are described in Section 3.1, "CF Microcode Encoding," page 3-2, Section 4.1, "ALU Micro-<br>code Formats," page 4-1, Section 6.1, "Texture-Fetch Microcode Formats," page 6-1, Section 5.2, "Vertex-Fetch Microcode Formats," page 5-2, and Chapter 8, "Microcode Formats."                                                                                                                                                                                                                                                                                                                                                                                           |

| Instruction              | 64 or 128   | <ul> <li>Two to four microcode formats that specify:</li> <li>Control flow (CF) instructions (64 bits). These include:<br/>general control flow instructions (such as branches and loops),<br/>instructions that allocate buffer space and import or export data, and<br/>instructions that initiate the execution of ALU, texture-fetch, or<br/>vertex-fetch clauses.</li> <li>ALU instructions (64 bits).</li> <li>Texture-fetch instructions (128 bits).</li> <li>Vertex-fetch instructions (128 bits).</li> <li>Instructions are identified in microcode formats by the _INST_ string in<br/>their field names and mnemonics. The functions of the instructions are<br/>described in Chapter 7, "Instruction Set."</li> </ul> |

| ALU Instruction<br>Group | 64 to 448   | <ul> <li>Variable-sized groups of instructions and constants that consist of:</li> <li>One to five 64-bit ALU instructions.</li> <li>Zero to two 64-bit literal constants.</li> <li>ALU instruction groups are described in Section 4.3, "ALU Instruction Slots and Instruction Groups," page 4-3.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Literal Constant         | 64          | Literal constants specify two 32-bit values, which can represent values associated with two elements of a 128-bit vector. These constants optionally can be included in ALU instruction groups.<br>Literal constants are described in Section 4.3, "ALU Instruction Slots and Instruction Groups," page 4-3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 2.3 Basic Instruction-Related Terms

| Term      | Size (bits)     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slot      | 64              | An ordered position within an ALU instruction group. Each ALU instruction group has one to seven slots, corresponding to the number of ALU instructions and literal constants in the instruction group.<br>Slots are described in Section 4.3, "ALU Instruction Slots and Instruction Groups," page 4-3.                                                                                                                                                                                                                                                                       |

| Clause    | 64 to unlimited | <ul> <li>A set of instructions of the same type. The types of clauses are:</li> <li>ALU clauses (which contain ALU instruction groups).</li> <li>Texture-fetch clauses.</li> <li>Vertex-fetch clauses.</li> <li>Clauses are initiated by control flow (CF) instructions and are described in Section 2.3, "Control Flow and Clauses," page 2-5, and Section 3.3, "Clause-Initiation Instructions," page 3-5.</li> </ul>                                                                                                                                                        |

| Allocate  | n/a             | Reserves storage space for data in an output buffer (a "scratch buffer,"<br>"ring buffer," "stream buffer," or "reduction buffer") or for data in an input<br>buffer (a "scratch buffer" or "ring buffer") prior to exporting (writing or read-<br>ing) data or addresses to, or from, that buffer. Space is allocated only for<br>data, not for addresses. After allocating space in a buffer, an <i>export</i> (write<br>or read) operation can be performed.                                                                                                                |

| Export    | n/a             | <ul> <li>To do any of the following:</li> <li>Write data from GPRs to an output buffer (a "scratch buffer," "frame buffer," "ring buffer," "stream buffer," or "reduction buffer").</li> <li>Write an address for data inputs to the memory controller.</li> <li>Read data from an input buffer (a "scratch buffer," or "ring buffer") to GPRs.</li> <li>The term <i>export</i> is a partial misnomer because it performs both input and output functions. Prior to exporting, an "allocate" operation must be performed to reserve space in the associated buffer.</li> </ul> |

| Fetch     | n/a             | Load data, using a vertex-fetch or texture-fetch instruction clause. Loads are not necessarily to general-purpose registers (GPRs); specific types of loads may be confined to specific types of storage destinations.                                                                                                                                                                                                                                                                                                                                                         |

| Vertex    | n/a             | A set of x,y (2D) coordinates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Quad      | n/a             | Four (x,y) data elements arranged in a 2-by-2 array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Primitive | n/a             | A point, line segment, or polygon before rasterization. It has vertices spec-<br>ified by geometric coordinates. Additional data can be associated with<br>vertices by means of linear interpolation across the primitive.                                                                                                                                                                                                                                                                                                                                                     |

| Fragment  | n/a             | <ul> <li>For graphics programming:</li> <li>The result of rasterizing a primitive. A fragment has no vertices; instead, it is represented by (x,y) coordinates.</li> <li>For general-purpose programming:</li> <li>A set of (x,y) data elements.</li> </ul>                                                                                                                                                                                                                                                                                                                    |

| Pixel     | n/a             | <ul> <li>For graphics programming:</li> <li>The result of placing a fragment in an (x,y) frame buffer.</li> <li>For general-purpose programming:</li> <li>A set of (x,y) data elements.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

Table 2.3

Basic Instruction-Related Terms (Cont.)

# 2.3 Control Flow and Clauses

Each program consists of two sections:

• Control Flow—Control flow instructions can:

- Initiate execution of ALU, texture-fetch, or vertex-fetch instructions.

- Allocate space in an input or output buffer.

- Export data to, or import data from, a buffer.

- Control branching, looping, and stack operations.

- *Clause*—A homogeneous group of instructions; each clause comprises ALU, texture-fetch, or vertex-fetch instructions exclusively. A control flow instruction that initiates an ALU, texture-fetch, or vertex-fetch clause does so by referring to an appropriate clause.

Table 2.4 provides a typical program flow example.

#### Table 2.4Flow of a Typical Program

|                                                                                                                                                                                                                                                                          | Microco                                                  | de Formats                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Function                                                                                                                                                                                                                                                                 | Control Flow (CF) Code                                   | Clause Code                                                                                                                         |

| Start loop.                                                                                                                                                                                                                                                              | CF_DWORD[0,1]                                            |                                                                                                                                     |

| Initiate texture-fetch clause.                                                                                                                                                                                                                                           | CF_DWORD[0,1]                                            |                                                                                                                                     |

| Texture-fetch or vertex-fetch clause to load data from memory to GPRs.                                                                                                                                                                                                   |                                                          | TEX_DWORD[0,1,2]                                                                                                                    |

| Initiate ALU clause.                                                                                                                                                                                                                                                     | CF_ALU_DWORD[0,1]                                        |                                                                                                                                     |

| ALU clause to compute on loaded data and lit-<br>eral constants. This example shows a single<br>clause consisting of a single ALU <i>instruction</i><br><i>group</i> containing five ALU instructions (two<br>quadwords each) and two quadwords of literal<br>constants. |                                                          | ALU_DWORD[0,1]<br>ALU_DWORD[0,1]<br>ALU_DWORD[0,1]<br>ALU_DWORD[0,1]<br>ALU_DWORD[0,1] LAST bit set<br>Literal[X,Y]<br>Literal[Z,W] |

| End loop.                                                                                                                                                                                                                                                                | CF_DWORD[0,1]                                            |                                                                                                                                     |

| Allocate space in an output buffer.                                                                                                                                                                                                                                      | CF_ALLOC_EXPORT_DWORD0<br>CF_ALLOC_EXPORT_DWORD1_BU<br>F |                                                                                                                                     |

| Export (write) results from GPRs to output buffer.                                                                                                                                                                                                                       | CF_ALLOC_EXPORT_DWORD0<br>CF_ALLOC_EXPORT_DWORD1_BU<br>F |                                                                                                                                     |

Control flow instructions:

- constitute the main program. Jump statements, loops, and subroutine calls are expressed directly in the control flow part of the program.

- include mechanisms to synchronize operations.

- indicate when a clause has completed.

- are required for buffer allocation in, and writing to, a program block's output buffer.

Some program types (VS, GS, DC, PS) have specific control flow instructions for synchronizing with other blocks.

Each clause, invoked by a control flow instruction, is a sequential list of instructions of limited length (for the maximum length, see sections on individual clauses). Clauses contain no flow control statements, but ALU clause instructions can apply a predicate on a per-instruction basis. Instructions within a single clause execute serially. Multiple clauses of a program can execute in parallel if they contain instructions of different types and the clauses are independent of one another. (Such parallel execution is invisible to the programmer except for increased performance.)

ALU clauses contain instructions for performing operations in each of the five ALUs (ALU.[X,Y,Z,W] and ALU.Trans) including setting and using predicates, and pixel kill operations (see Section 4.8.1, "Instructions for All ALU Units," page 4-19). Texture-fetch clauses contain instructions for performing texture and constant-fetch reads from memory. Vertex-fetch clauses are devoted to obtaining vertex data from memory. Systems lacking a vertex cache can perform vertex-fetch operations in a texture clause instead.

A predicate is a bit that is set or cleared as the result of evaluating some condition; subsequently, it is used either to mask writing an ALU result or as a condition itself. There are two kinds of predicates, both of which are set in an ALU clause.

- The first is a single predicate local to the ALU clause itself. Once computed, the predicate can be referred to in a subsequent instruction to conditionally write an ALU result to the indicated general-purpose register(s).

- The second type is a bit in a predicate stack. An ALU clause computes the predicate bits in the stack and manipulates the stack. A predicate bit in the stack can be referred to in a control-flow instruction to induce conditional branching.

# 2.4 Instruction Types and Grouping

There are four types of instructions:

- control flow instructions

- three clause types: control flow (CF), ALU, texture fetch, and vertex fetch.

There are separate instruction caches in the processor for each instruction type.

A CF program has no maximum size; however, each clause has a maximum size. When a program is organized in memory, the instructions must be ordered as follows:

- All CF instructions.

- All ALU clauses.

- All texture-fetch and vertex-fetch clauses.

The CPU host configures the base address of each program type before executing a program.

# 2.5 Program State

Table 2.5 through Table 2.8 summarize a programmer's view of the R600 program state that is accessible by a single thread in an R600 program. The tables do not include:

- states that are maintained exclusively by R600 hardware, such as the internal loop-control registers,

- states that are accessible only to host software, such as configuration registers, or

- the duplication of states for many execution threads.

The column headings in Table 2.5 through Table 2.8 have the following meanings:

- Access by R600 Software—Readable (R), writable (W), or both (R/W) by software executing on the R600 processor.

- Access by Host Software—Readable, writable, or both by software executing on the host processor. The tables do not include state objects, such as R600 configuration registers, that accessible only to host software.

- *Number per Thread*—The maximum number of such state objects available to each thread. In some cases, the maximum number is shared by all executing threads.

- Width—The width, in bits, of the state object.

| State                            | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread   | Width<br>(bits)   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|-----------------------|-----------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integer Constant<br>Register (I) | R                     | W                     | 1                 | 96<br>(3 x 32)    | The loop-variable constant specified in the CF_CONST field of the CF_DWORD1 microcode for-<br>mat for the current LOOP* instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Loop Index (aL)                  | R                     | No                    | 1                 | 13                | A register that is initialized by LOOP* instructions<br>and incremented by hardware on each iteration<br>of a loop, based on values provided in the LOOP*<br>instruction's CF_CONST field of the CF_DWORD1<br>microcode format. It can be used for relative<br>addressing of GPRs by any clause. Loops can<br>be nested, so the counter and index are stored<br>in the stack.<br>ALU instructions can read the current aL index<br>value by specifying it in the INDEX_MODE field of<br>the ALU_DWORD0 microcode format, or in the<br>ELEM_LOOP field of CF_ALLOC_EXPORT_DWORD1_*<br>microcode formats.<br>The register is 13 bits wide, but some instruc-<br>tions use only the low 9 bits. |

| Stack                            | No                    | No                    | Chip-<br>Specific | Chip-<br>Specific | The hardware maintains a single, multi-entry<br>stack for saving and restoring the state of nested<br>loops, pixels (valid mask and active mask, pred-<br>icates, and other execution details. The total<br>number of stack entries is divided among all<br>executing threads.                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 2.5Control-Flow State

Table 2.6 ALU State

| State                               | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread                                      | Width<br>(bits)     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------|-----------------------|-----------------------|------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

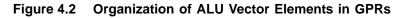

| General-Purpose<br>Registers (GPRs) | R/W                   | No                    | 127 minus<br>2 times<br>Clause-<br>Temporary<br>GPRs | 128<br>(4 x 32 bit) | Each thread has access to up to 127<br>GPRs, minus two times the number of<br>Clause-Temporary GPRs. Four GPRs are<br>reserved as Clause-Temporary GPRs that<br>persist only for one ALU clause (and thus<br>are not accessible to fetch and export<br>units).<br>GPRs can hold data in one of several for-<br>mats: the ALU can work with 32-bit IEEE<br>floats (S23E8 format with special values),<br>32-bit unsigned integers, and 32-bit signed<br>integers.                              |

| Clause-Tempo-<br>rary GPRs          | No                    | Yes                   | 4                                                    | 128<br>(4 x 32 bit) | GPRs containing clause-temporary vari-<br>ables. The number of clause-temporary<br>GPRs used by each thread reduces the<br>total number of GPRs available to the<br>thread, as described immediately above.                                                                                                                                                                                                                                                                                   |

| Address Regis-<br>ter (AR)          | W                     | No                    | 1                                                    | 36<br>(4 x 9 bit)   | A register containing a four-element vector<br>of indices that are written by MOVA instruc-<br>tions. Hardware reads this register. The<br>indices are used for relative addressing of<br>a constant file (called constant waterfall-<br>ing). This state only persists for one ALU<br>clause. When used for relative addressing,<br>a specific vector element must be selected.                                                                                                              |

| Constant Regis-<br>ters (CRs)       | R                     | W                     | 512                                                  | 128<br>(4 x 32 bit) | Registers that contain constants. Each reg-<br>ister is organized as four 32-bit elements of<br>a vector. Software can use either the CRs<br>or the off-chip <i>constant cache</i> , but not both.<br>DirectX calls these the Floating-Point Con-<br>stant (F) Registers.                                                                                                                                                                                                                     |

| Previous Vector<br>(PV)             | R                     | No                    | 1                                                    | 128<br>(4 x 32 bit) | Registers that contain the results of the previous ALU.[X,Y,Z,W] operations. This state only persists for one ALU clause.                                                                                                                                                                                                                                                                                                                                                                     |

| Previous Scalar<br>(PS)             | R                     | No                    | 1                                                    | 32                  | A register that contains the results of the previous ALU.Trans operations. This state only persists for one ALU clause.                                                                                                                                                                                                                                                                                                                                                                       |

| Predicate<br>Register               | R/W                   | No                    | 1                                                    | 1                   | A register containing predicate bits. The<br>bits are set or cleared by ALU instructions<br>as the result of evaluating some condition;<br>the bits are subsequently used either to<br>mask writing an ALU result or as a condi-<br>tion itself.<br>An ALU clause computes the predicate bits<br>in this register. A predicate bit in this regis-<br>ter can be referred to in a control-flow<br>instruction to induce conditional branching.<br>This state only persists for one ALU clause. |

| State       | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread | Width<br>(bits)         | Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------------|-----------------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pixel State | No                    | No                    | 1               | 192<br>(64 x 2<br>bits) | State bits that reflect each pixel's active<br>status as conditional instructions are exe-<br>cuted. The state can be <i>Active</i> , <i>Inactive-</i><br><i>branch</i> , <i>Inactive-continue</i> , or <i>Inactive-</i><br><i>break</i> .                                                                                                                                 |

| Valid Mask  | No                    | No                    | 1               | 64                      | A mask indicating which pixels have been killed by a pixel-kill operation. The mask is updated when a CF_INST_KILL instruction is executed.                                                                                                                                                                                                                                |

| Active Mask | W<br>(indirect)       | No                    | 1               | 1 bit per<br>pixel      | A mask indicating which pixels are cur-<br>rently executing and which are not<br>(1 = execute, 0 = skip). This can be<br>updated by PRED_SET* ALU instructions <sup>1</sup> ,<br>but the updates do not take effect until the<br>end of the ALU clause.<br>CF_ALU instructions can update this mask<br>with the result of the last PRED_SET*<br>instruction in the clause. |

## Table 2.6ALU State (Cont.)

1. An asterisk (\*) after a mnemonic string indicates that there are additional characters in the string that define variants.

### Table 2.7Vertex-Fetch State

| State                  | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread | Width<br>(bits) | Description                            |

|------------------------|-----------------------|-----------------------|-----------------|-----------------|----------------------------------------|

| Vertex-Fetch Constants | R                     | W                     | 128             | 84              | These describe the buffer format, etc. |

#### Table 2.8 Texture-Fetch and Constant-Fetch State

| State                | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread | Width<br>(bits) | Description                                                                                                                                                                                                                                                                    |

|----------------------|-----------------------|-----------------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Texture Samplers     | No                    | W                     | 18              | 96              | There are 18 samplers (16 for DirectX plus 2 spares) available for each of the VS, GS, PS program types, two of which are spares. A texture sampler constant is used to specify how a texture is to be accessed. It contains information such as filtering and clamping modes. |

| Texture<br>Resources | No                    | W                     | 160             | 160             | There are 160 resources available for each of the VS, GS, PS program types, and 16 for FS program types.                                                                                                                                                                       |

| State                                     | Access by<br>R600 S/W | Access by<br>Host S/W | # per<br>Thread | Width<br>(bits)         | Description                                                                                                                                                                                                                                                  |

|-------------------------------------------|-----------------------|-----------------------|-----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Border Color                              | No                    | W                     | 1               | 128<br>(4 x 32<br>bits) | This is stored in the texture pipeline, but is ref-<br>erenced in texture-fetch instructions.                                                                                                                                                                |

| Bicubic Weights                           | No                    | W                     | 2               | 176                     | These define the weights, one horizontal and<br>one vertical, for bicubic interpolation. The state<br>is stored in the texture pipeline, but referenced<br>in texture-fetch instructions.                                                                    |

| Kernel Size for<br>Cleartype<br>Filtering | No                    | W                     | 2               | 3                       | These define the kernel sizes, one horizontal<br>and one vertical, for filtering with Microsoft's<br>Cleartype™ subpixel rendering display tech-<br>nology. The state is stored in the texture<br>pipeline, but referenced in texture-fetch<br>instructions. |

## Table 2.8 Texture-Fetch and Constant-Fetch State (Cont.)

# Chapter 3 Control Flow (CF) Programs

A control flow (CF) program is a main program. It directs the flow of program clauses by using control-flow instructions (conditional jumps, loops, and subroutines), and it can include memory-allocation instructions and other instructions that specify when vertex and geometry programs have completed their operations. The R600 hardware maintains a single, multi-entry stack for saving and restoring active mask counters, returning addresses for subroutines.

CF instructions can:

- Execute an ALU, texture-fetch, or vertex-fetch clause. These operations take the address of the clause to execute, and a count indicating the size of the clause. A program can specify that a clause must wait until previously executed clauses complete, or that a clause must execute conditionally (only active pixels execute the clause, and the clause is skipped entirely if no pixels are active).

- Execute a DirectX9-style loop. There are two instructions marking the beginning and end of the loop. Each instruction takes the address of its paired LOOP\_START and LOOP\_END instructions. A loop reads from one of 32 constants to get the loop count, initial index value, and index increment value. Loops can be nested.

- Execute a DirectX10-style loop. There are two instructions marking the beginning and end of the loop. Each instruction takes an address of its paired LOOP\_START and LOOP\_END instructions. Loops can be nested.

- Execute a repeat loop (one that does not maintain a loop index). Repeat loops are implemented with the LOOP\_START\_NO\_AL and LOOP\_END instructions. These loops can be nested.

- Break out of the innermost loop. LOOP\_BREAK instructions take an address to the corresponding LOOP\_END instruction. LOOP\_BREAK instructions can be conditional (executing only for pixels that satisfy a break condition).

- Continue a loop, starting with the next iteration of the innermost loop. LOOP\_CONTINUE instructions take an address to the corresponding LOOP\_END instruction. LOOP\_CONTINUE instructions can be conditional.

- Execute a subroutine CALL or RETURN. A CALL takes a jump address. A RETURN never takes an address; it returns to the address at the top of the stack. Calls can be conditional (only pixels satisfying a condition perform the instruction). Calls can be nested.

- Call the vertex-fetch-shader (FS) clause. The address field in a VTX or VTX\_TC control-flow instruction is unused; the address of the vertex-fetch

clause is global and written by the host. Thus, it makes no sense to nest these calls.

- Jump to a specified address in the control-flow program. A JUMP instruction can be conditional or unconditional.

- Perform manipulations on the current active mask for flow control (for example: executing an ELSE instruction, saving and restoring the active mask on the stack).

- Allocate data-storage space in a buffer and import (read) or export (write) addresses or data.

- Signal that the geometry shader (GS) has finished exporting a vertex, and optionally the end of a primitive strip.

The end of the CF program is marked by setting the END\_OF\_PROGRAM bit in the last CF instruction in the program. The CF program terminates after the end of this instruction, regardless of whether the instruction is conditionally executed.

## 3.1 CF Microcode Encoding

The microcode formats and all of their fields are described in Chapter 8, "Microcode Formats.". An overview of the encoding is given below. The following instruction-related terms are used throughout the remainder of this document:

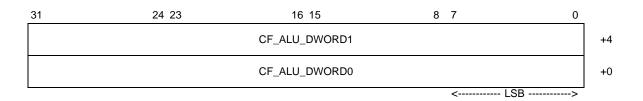

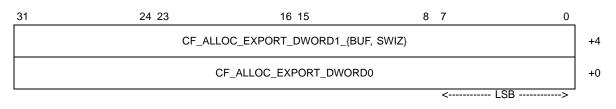

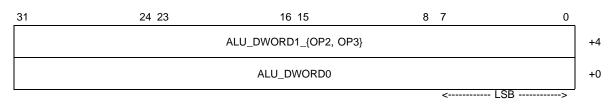

- Microcode Format—An encoding format whose fields specify instructions and associated parameters. Microcode formats are used in sets of two or four 32bit doublewords (dwords). For example, the two mnemonics, CF\_DWORD[0,1] indicate a microcode-format pair, CF\_DWORD0 and CF\_DWORD1, described in Section 8.1, "Control Flow (CF) Instructions," page 8-2.