# Memory FRAM

# 4 M Bit (512 K × 8)

# MB85R4001A

#### **■ DESCRIPTIONS**

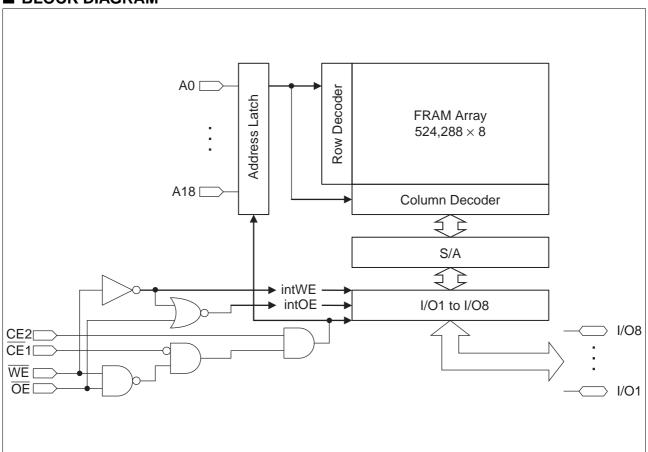

The MB85R4001A is an FRAM (Ferroelectric Random Access Memory) chip consisting of 524,288 words  $\times$  8 bits of nonvolatile memory cells fabricated using ferroelectric process and silicon gate CMOS process technologies.

The MB85R4001A is able to retain data without using a back-up battery, as is needed for SRAM.

The memory cells used in the MB85R4001A can be used for 10<sup>10</sup> read/write operations, which is a significant improvement over the number of read and write operations supported by Flash memory and E<sup>2</sup>PROM.

The MB85R4001A uses a pseudo-SRAM interface that is compatible with conventional asynchronous SRAM.

#### **■ FEATURES**

• Bit configuration : 524,288 words × 8 bits

• Read/write endurance : 10<sup>10</sup> times / byte

• Data retention : 10 years ( + 55 °C), 55 years ( + 35 °C)

Operating power supply voltage : 3.0 V to 3.6 V

Low power operation : Operating power supply current 15 mA (Typ)

Standby current 50 µA (Typ)

Operation ambient temperature range : −40 °C to +85 °C

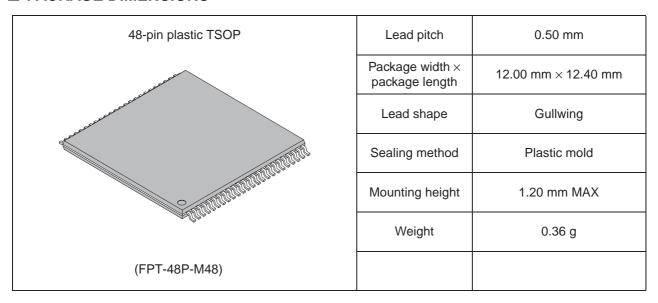

Package : 48-pin plastic TSOP (FPT-48P-M48)

RoHS compliant

## MB85R4001A

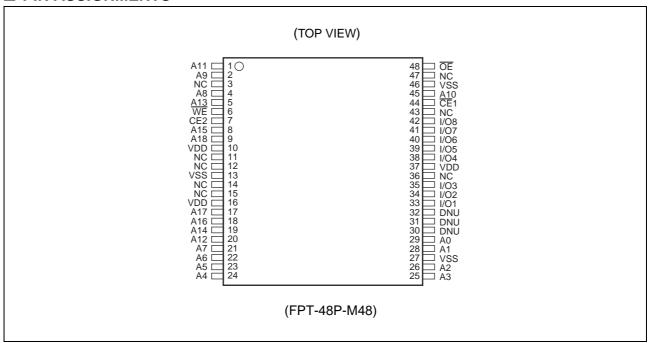

### **■ PIN ASSIGNMENTS**

#### **■ PIN DESCRIPTIONS**

| Pin Number                                | Pin Name     | Functional Description                                                 |

|-------------------------------------------|--------------|------------------------------------------------------------------------|

| 1, 2, 4, 5, 8, 9, 17 to 26, 28, 29,<br>45 | A0 to A18    | Address Input pins                                                     |

| 33 to 35, 38 to 42                        | I/O1 to I/O8 | Data Input/Output pins                                                 |

| 44                                        | CE1          | Chip Enable 1 Input pin                                                |

| 7                                         | CE2          | Chip Enable 2 Input pin                                                |

| 6                                         | WE           | Write Enable Input pin                                                 |

| 48                                        | ŌĒ           | Output Enable Input pin                                                |

| 10, 16, 37                                | VDD          | Supply Voltage pins Connect all three pins to the power supply.        |

| 13, 27, 46                                | VSS          | Ground pins Connect all three pins to ground.                          |

| 3, 11, 12, 14, 15, 36, 43, 47             | NC           | No Connect pins<br>Leave these pins open, or connect to VDD or<br>VSS. |

| 30 to 32                                  | DNU          | Do Not Use pins Make sure to connect these pins to ground.             |

#### **■ BLOCK DIAGRAM**

### **■ FUNCTIONAL TRUTH TABLE**

| Operation Mode                       | CE1 | CE2      | WE | OE  | I/O <sub>1</sub> to I/O <sub>8</sub> | <b>Supply Current</b> |  |

|--------------------------------------|-----|----------|----|-----|--------------------------------------|-----------------------|--|

|                                      | Н   | Х        | Х  | X X |                                      | Otom dh.              |  |

| Standby Precharge                    | Х   | L        | Х  | Х   | Hi-Z                                 | Standby<br>(IsB)      |  |

|                                      | X   | Х        | Н  | Н   |                                      | (100)                 |  |

| Read                                 | Z   | Н        | H  | L   |                                      |                       |  |

| Road                                 | L   | 工        | 11 | _   | Data Output                          |                       |  |

| Read<br>(Pseudo-SRAM, OE control*1)  | L   | Н        | Н  | Z   |                                      | Operation             |  |

| Write                                | 7_  | Н        | L  | Н   |                                      | (IDD)                 |  |

| VVIIC                                | L   | <u>_</u> | _  |     | Data Input                           |                       |  |

| Write<br>(Pseudo-SRAM, WE control*2) | L   | Н        | Z  | Н   |                                      |                       |  |

Note: L = V<sub>IL</sub>, H = V<sub>IH</sub>, X can be either V<sub>IL</sub>, V<sub>IH</sub>,  $\searrow$  or  $\surd$ , Hi-Z = High Impedance

\*1 :  $\overline{\text{OE}}$  control of the Pseudo-SRAM means the valid address at the falling edge of  $\overline{\text{OE}}$  to read.

\*2 : WE control of the Pseudo-SRAM means the valid address and data at the falling edge of WE to write.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol          | Rat         | Unit                        |       |

|-------------------------------|-----------------|-------------|-----------------------------|-------|

| Farameter                     | Зупион          | Min         | Max                         | Ollit |

| Power Supply Voltage*         | V <sub>DD</sub> | - 0.5       | + 4.0                       | V     |

| Input Pin Voltage*            | Vin             | - 0.5       | $V_{DD} + 0.5 \ ( \le 4.0)$ | V     |

| Output Pin Voltage*           | Vоит            | - 0.5       | $V_{DD} + 0.5 \ ( \le 4.0)$ | V     |

| Operation Ambient Temperature | TA              | <b>- 40</b> | + 85                        | °C    |

| Storage Temperature           | Тѕтс            | <b>– 55</b> | + 125                       | °C    |

<sup>\*:</sup> All voltages are referenced to VSS (ground 0 V).

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                     | Symbol          | Value               |     |                          |      |  |

|-------------------------------|-----------------|---------------------|-----|--------------------------|------|--|

| Farameter                     | Symbol          | Min                 | Тур | Max                      | Unit |  |

| Power Supply Voltage*         | V <sub>DD</sub> | 3.0                 | 3.3 | 3.6                      | V    |  |

| High Level Input Voltage*     | VIH             | $V_{DD} \times 0.8$ | _   | $V_{DD} + 0.5 (\le 4.0)$ | V    |  |

| Low Level Input Voltage*      | Vıl             | - 0.5               | _   | + 0.6                    | V    |  |

| Operation Ambient Temperature | TA              | <b>- 40</b>         | _   | + 85                     | °C   |  |

<sup>\*:</sup> All voltages are referenced to VSS (ground 0 V).

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

> No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

(within recommended operating conditions)

| Parameter                        | Symbol Condition |                                                                                                                                                                                   |                       | Value |     | Unit  |

|----------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----|-------|

| Farameter                        | Syllibol         | Condition                                                                                                                                                                         | Min                   | Тур   | Max | Ollit |

| Input Leakage Current*1          | lu               | $V_{IN} = 0 V to V_{DD}$                                                                                                                                                          |                       | _     | 10  | μΑ    |

| Output Leakage Current           | <b>I</b> LO      | $V_{OUT} = 0 \text{ V to } V_{DD},$<br>$\overline{CE}1 = V_{IH} \text{ or } \overline{OE} = V_{IH}$                                                                               |                       |       | 10  | μΑ    |

| Operating Power Supply Current*2 | loo              | $\overline{\text{CE}}$ 1 = 0.2 V, CE2 = V <sub>DD</sub> -0.2 V, I <sub>out</sub> = 0 mA                                                                                           |                       | 15    | 20  | mA    |

| Standby Current*3                | Isa              | $\overline{CE}$ 1 $\geq$ V <sub>DD</sub> -0.2 V<br>$\overline{CE}$ 2 $\leq$ 0.2 V<br>$\overline{OE}$ $\geq$ V <sub>DD</sub> -0.2 V, $\overline{WE}$ $\geq$ V <sub>DD</sub> -0.2 V | _                     | 50    | 150 | μΑ    |

| High Level Output Voltage        | Vон              | Iон = −1.0 mA                                                                                                                                                                     | V <sub>DD</sub> × 0.8 | _     | _   | V     |

| Low Level Output Voltage         | Vol              | loL = 2.0 mA                                                                                                                                                                      | _                     | _     | 0.4 | V     |

<sup>\*1:</sup> This also applies to DNU pins.

<sup>\*2 :</sup> During the measurement of IDD, the Address and Data In were taken to only change once per active cycle. Iout: output current

<sup>\*2 :</sup> All pins other than setting pins shall be input at the CMOS level voltages such as  $H \ge V_{DD} - 0.2 \text{ V}$ ,  $L \le 0.2 \text{ V}$ .

## MB85R4001A

#### 2. AC Characteristics

#### • AC Test Conditions

Power Supply Voltage : 3.0 V to 3.6 V Operation Ambient Temperature : -40 °C to +85 °C Input Voltage Amplitude : 0.3 V to 2.7 V

Input Rising Time : 5 ns Input Falling Time : 5 ns

Input Falling Time

Input Evaluation Level : 2.0 V / 0.8 V

Output Evaluation Level : 2.0 V / 0.8 V

Capacitance : 50 pF

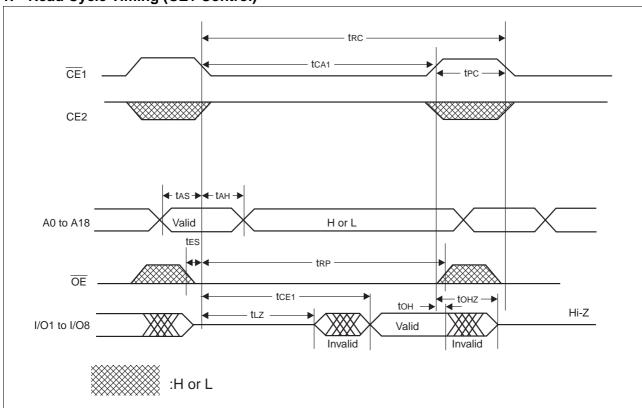

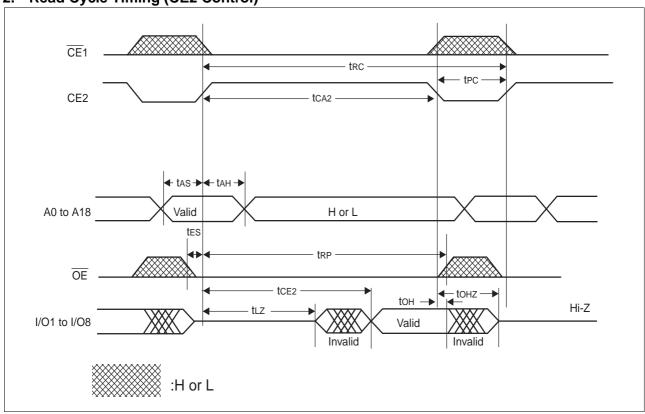

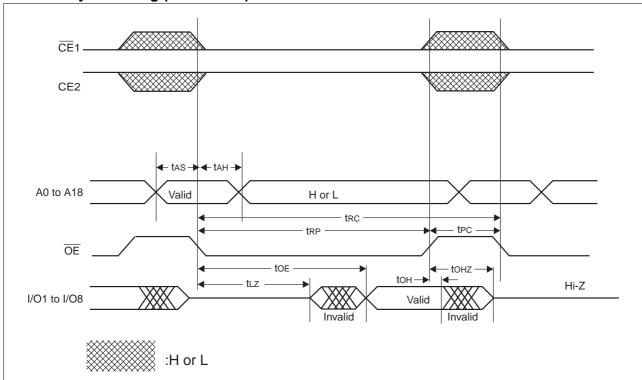

#### (1) Read Cycle

| Parameter            | Symbol           | Va  | lue | Unit |

|----------------------|------------------|-----|-----|------|

| r ai ailletei        | Symbol           | Min | Max | Onit |

| Read Cycle Time      | <b>t</b> RC      | 150 | _   | ns   |

| CE1 Active Time      | <b>t</b> CA1     | 120 | _   | ns   |

| CE2 Active Time      | t <sub>CA2</sub> | 120 | _   | ns   |

| OE Active Time       | <b>t</b> RP      | 120 | _   | ns   |

| Precharge Time       | <b>t</b> PC      | 20  | _   | ns   |

| Address Setup Time   | tas              | 0   | _   | ns   |

| Address Hold Time    | <b>t</b> ah      | 50  | _   | ns   |

| OE Setup Time        | <b>t</b> ES      | 0   | _   | ns   |

| Output Hold Time     | tон              | 0   | _   | ns   |

| Output Set Time      | <b>t</b> LZ      | 30  | _   | ns   |

| CE1 Access Time      | t <sub>CE1</sub> | _   | 120 | ns   |

| CE2 Access Time      | t <sub>CE2</sub> | _   | 120 | ns   |

| OE Access Time       | <b>t</b> oe      | _   | 120 | ns   |

| Output Floating Time | tонz             | _   | 20  | ns   |

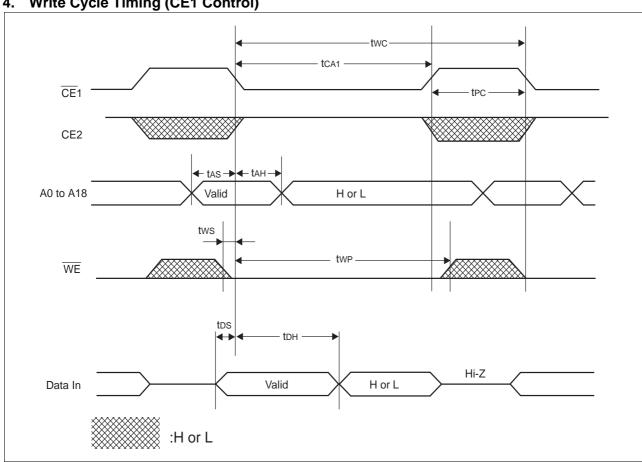

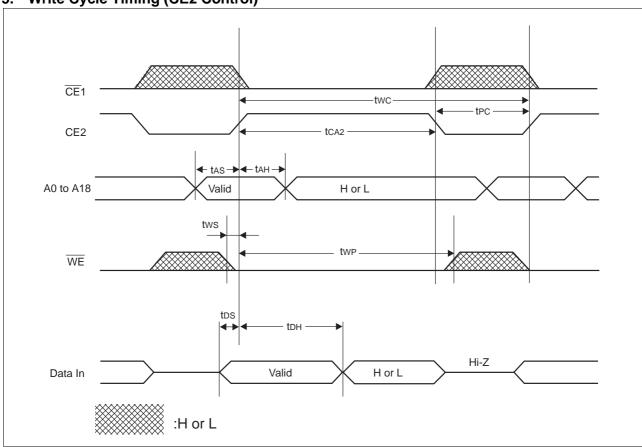

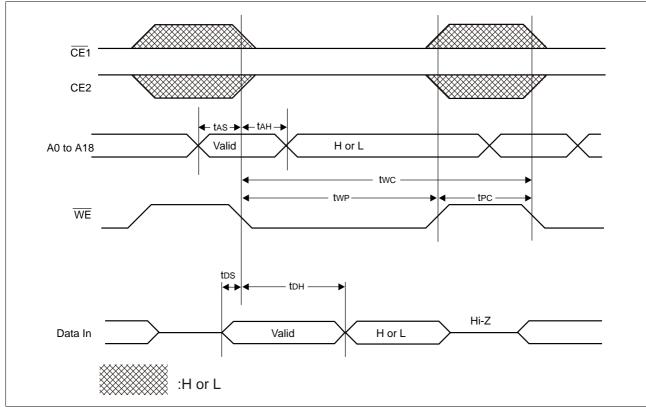

#### (2) Write Cycle

| Parameter          | Symbol           | Val | lue | Unit |

|--------------------|------------------|-----|-----|------|

| Parameter          | Symbol           | Min | Max | Unit |

| Write Cycle Time   | <b>t</b> wc      | 150 | _   | ns   |

| CE1 Active Time    | t <sub>CA1</sub> | 120 | _   | ns   |

| CE2 Active Time    | t <sub>CA2</sub> | 120 | _   | ns   |

| Precharge Time     | <b>t</b> PC      | 20  | _   | ns   |

| Address Setup Time | <b>t</b> AS      | 0   | _   | ns   |

| Address Hold Time  | tан              | 50  | _   | ns   |

| Write Pulse Width  | <b>t</b> wp      | 120 | _   | ns   |

| Data Setup Time    | <b>t</b> DS      | 0   |     | ns   |

| Data Hold Time     | tон              | 50  | _   | ns   |

| Write Setup Time   | tws              | 0   | _   | ns   |

## 3. Pin Capacitance

| Parameter                 | Symbol | Condition                                                       |     | Value |     | Unit  |

|---------------------------|--------|-----------------------------------------------------------------|-----|-------|-----|-------|

| Farameter                 | Зуппоп | Condition                                                       | Min | Тур   | Max | Oilit |

| Input Capacitance         | Cin    | V V V 0V                                                        | _   | _     | 10  | pF    |

| Output Capacitance        | Соит   | $V_{DD} = V_{IN} = V_{OUT} = 0 V,$<br>$f = 1 MHz, T_A = +25 °C$ | _   | _     | 10  | pF    |

| DNU Pin Input Capacitance | CDNU   |                                                                 | _   | _     | 10  | pF    |

#### **■ TIMING DIAGRAMS**

## 1. Read Cycle Timing (CE1 Control)

## 2. Read Cycle Timing (CE2 Control)

## 3. Read Cycle Timing (OE Control)

## 4. Write Cycle Timing (CE1 Control)

## 5. Write Cycle Timing (CE2 Control)

## 6. Write Cycle Timing (WE Control)

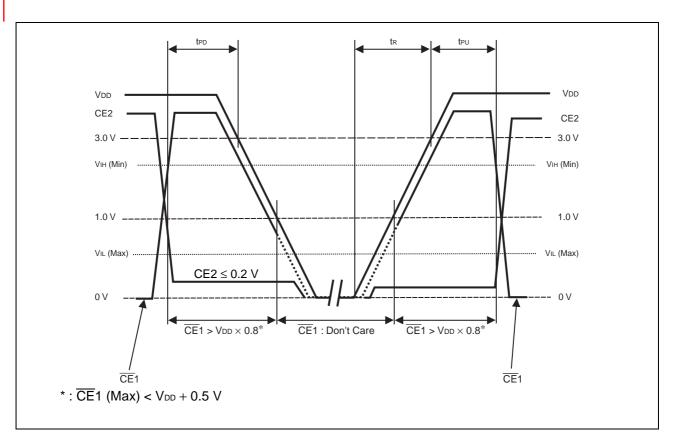

#### **■ POWER ON/OFF SEQUENCE**

| Parameter                         | Symbol      |      | Unit |     |       |

|-----------------------------------|-------------|------|------|-----|-------|

| Farameter                         | Syllibol    | Min  | Тур  | Max | Oilit |

| CE1 level hold time for Power OFF | <b>t</b> PD | 85   |      |     | ns    |

| CE1 level hold time for Power ON  | <b>t</b> PU | 85   |      |     | ns    |

| Power supply rising time          | <b>t</b> R  | 0.05 |      | 200 | ms    |

If the device does not operate within the specified conditions of read cycle, write cycle or power on/off sequence, memory data can not be guaranteed.

In case the power is turned on or off, use the power supply reset IC and fix the CE2 to low level, to prevent unexpected writing. Use either of  $\overline{\text{CE}}1$  or CE2, or both to disable control of the device.

#### **■ FRAM CHARACTERISTICS**

| Item                   | Min              | Max | Unit       | Parameter                                             |

|------------------------|------------------|-----|------------|-------------------------------------------------------|

| Read/Write Endurance*1 | 10 <sup>10</sup> | _   | Times/byte | Operation Ambient Temperature T <sub>A</sub> = +85 °C |

| Data Retention*2       | 10               | _   | Years      | Operation Ambient Temperature T <sub>A</sub> = +55 °C |

| Data Retention -       | 55               | _   | 1 Edis     | Operation Ambient Temperature T <sub>A</sub> = +35 °C |

<sup>\*1:</sup> Total number of reading and writing defines the minimum value of endurance, as an FRAM memory operates with destructive readout mechanism.

#### **■ NOTES ON USE**

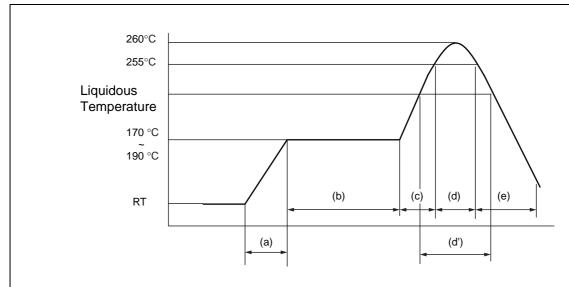

Data written before performing IR reflow is not guaranteed after IR reflow.

<sup>\*2 :</sup> Minimun values define retention time of the first reading/writing data right after shipment, and these values are calculated by qualification results.

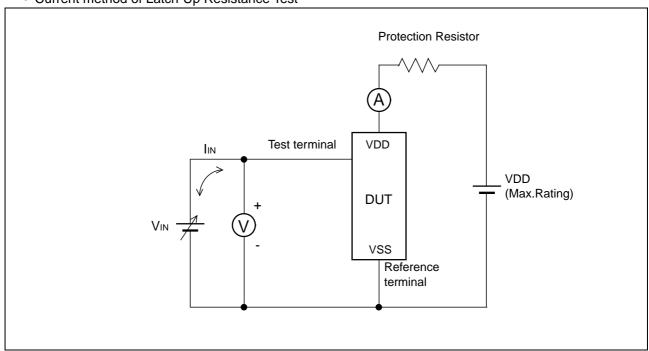

#### **■ ESD AND LATCH-UP**

| Test                                                                | DUT              | Value     |

|---------------------------------------------------------------------|------------------|-----------|

| ESD HBM (Human Body Model)<br>JESD22-A114 compliant                 |                  | ≥  2000 V |

| ESD MM (Machine Model)<br>JESD22-A115 compliant                     |                  | ≥  200 V  |

| ESD CDM (Charged Device Model)<br>JESD22-C101 compliant             |                  | _         |

| Latch-Up (I-test)<br>JESD78 compliant                               | MB85R4001ANC-GE1 | _         |

| Latch-Up (V <sub>supply</sub> overvoltage test)<br>JESD78 compliant |                  | _         |

| Latch-Up (Current Method)<br>Proprietary method                     |                  | ≥  300 mA |

| Latch-Up (C-V Method)<br>Proprietary method                         |                  | _         |

#### • Current method of Latch-Up Resistance Test

Note: The voltage  $V_{IN}$  is increased gradually and the current  $I_{IN}$  of 300 mA at maximum shall flow. Confirm the latch up does not occur under  $I_{IN} = \pm 300$  mA.

In case the specific requirement is specified for I/O and  $I_{\rm IN}$  cannot be 300 mA, the voltage shall be increased to the level that meets the specific requirement.

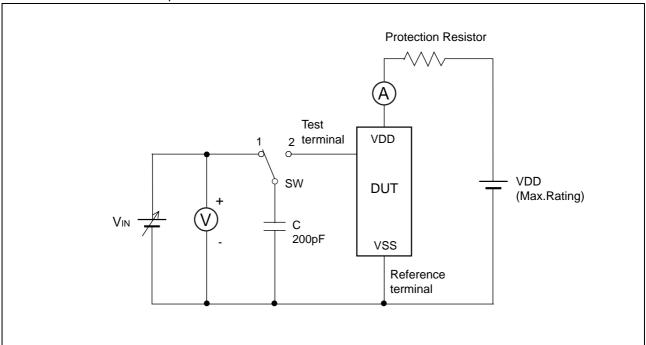

• C-V method of Latch-Up Resistance Test

Note: Charge voltage alternately switching 1 and 2 approximately 2 sec interval. This switching process is considered as one cycle.

Repeat this process 5 times. However, if the latch-up condition occurs before completing 5 times, this test must be stopped immediately.

#### ■ REFLOW CONDITIONS AND FLOOR LIFE

| Item                 | Condition                                                                                                          |                                                                                                                                      |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Method               | IR (infrared                                                                                                       | reflow), Convection                                                                                                                  |  |  |  |

| Times                | 2                                                                                                                  |                                                                                                                                      |  |  |  |

|                      | Before unpacking                                                                                                   | Please use within 2 years after production.                                                                                          |  |  |  |

|                      | From unpacking to 2nd reflow                                                                                       | Within 8 days                                                                                                                        |  |  |  |

| Floor life           | In case over period of floor life                                                                                  | Baking with 125 °C+/-3 °C for 24hrs+2hrs/-0hrs is required. Then please use within 8 days. (Please remember baking is up to 2 times) |  |  |  |

| Floor life condition | Between 5 °C and 30 °C and also below 70%RH required. (It is preferred lower humidity in the required temp range.) |                                                                                                                                      |  |  |  |

#### **Reflow Profile**

(a) Average ramp-up rate

(b) Preheat & Soak

(e) Cooling

(c) Average ramp-up rate (d) Peak temperature

(d') Liquidous temperature

: 1 °C/s to 4 °C/s : 170 °C to 190 °C, 60 s to 180 s

: 1 °C/s to 4 °C/s

: Temperature 260 °C Max; 255 °C within 10 s

: Up to 230 °C within 40 s or Up to 225 °C within 60 s or

Up to 220 °C within 80 s

: Natural cooling or forced cooling

Note: Temperature on the top of the package body is measured.

#### **■ RESTRICTED SUBSTANCES**

This product complies with the regulations below (Based on current knowledge as of November 2011).

- EU RoHS Directive (2002/95/EC)

- China RoHS (Administration on the Control of Pollution Caused by Electronic Information Products (电子信息产品污染控制管理办法))

- Vietnam RoHS (30/2011/TT-BCT)

Restricted substances in each regulation are as follows.

| Substances                            | Threshold | Contain status* |

|---------------------------------------|-----------|-----------------|

| Lead and its compounds                | 1,000 ppm | О               |

| Mercury and its compounds             | 1,000 ppm | 0               |

| Cadmium and its compounds             | 100 ppm   | О               |

| Hexavalent chromium compound          | 1,000 ppm | О               |

| Polybrominated biphenyls (PBB)        | 1,000 ppm | 0               |

| Polybrominated diphenyl ethers (PBDE) | 1,000 ppm | 0               |

<sup>\*:</sup> The mark of "O" shows below a threshold value.

# MB85R4001A

## **■ ORDERING INFORMATION**

| Part Number      | Package                              | Shipping form | Minimum shipping quantity |

|------------------|--------------------------------------|---------------|---------------------------|

| MB85R4001ANC-GE1 | 48-pin plastic TSOP<br>(FPT-48P-M48) | Tray          | 1                         |

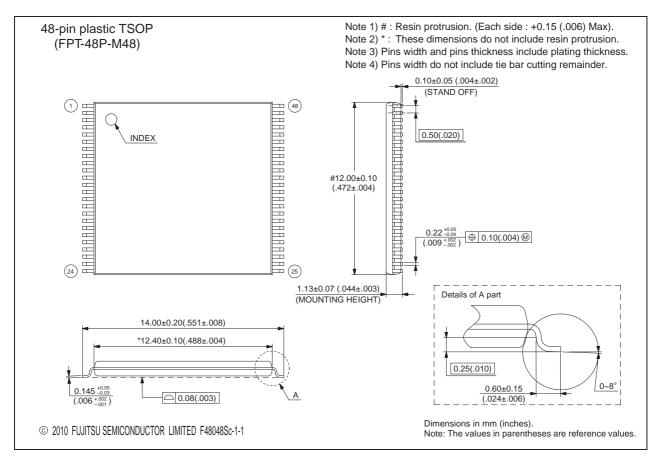

#### ■ PACKAGE DIMENSIONS

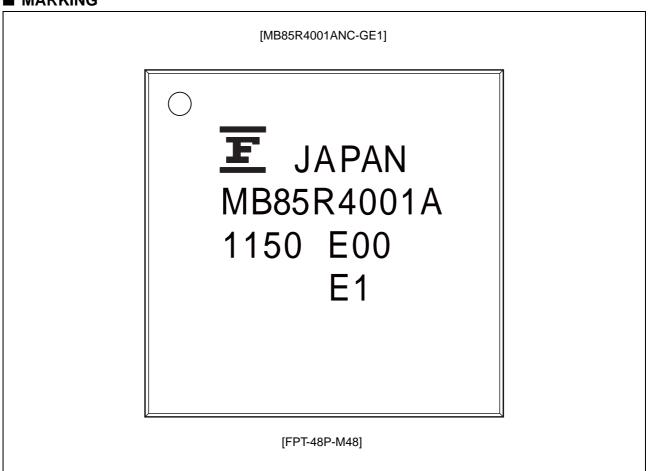

#### **■ MARKING**

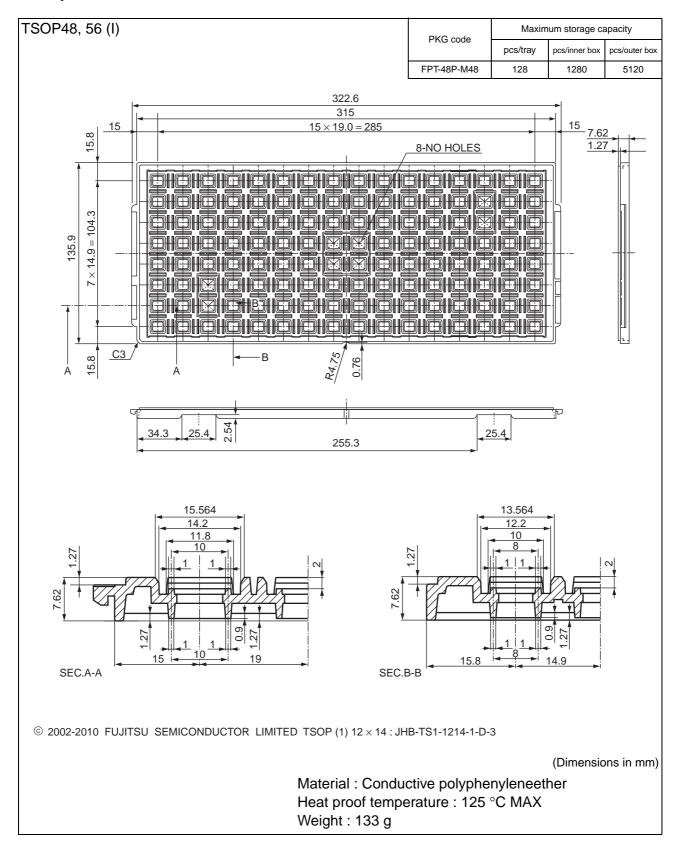

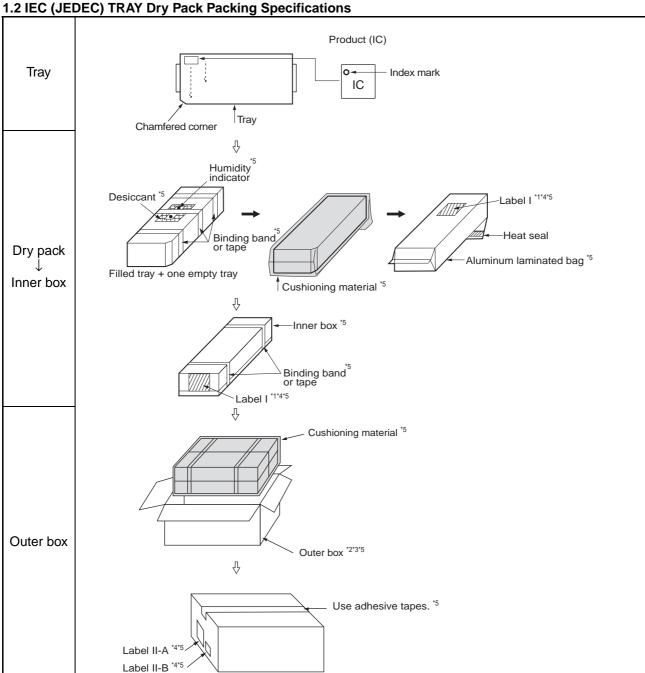

#### **■ SHIPPING FORM**

#### 1. Tray

#### 1.1 Tray Dimensions

- \*1: For a product of witch part number is suffixed with "E1", a " G (%) " marks is display to the moisture barrier

- \*2: The size of the outer box may be changed depending on the quantity of inner boxes.

- \*3: The space in the outer box will be filled with empty inner boxes, or cushions, etc.

- \*4: Please refer to an attached sheet about the indication label.

bag and the inner boxes.

\*5: The packing materials except tray may differ slightly from the color and dimensions depend on country of manufacture.

Note: The packing specifications may not be applied when the product is delivered via a distributer.

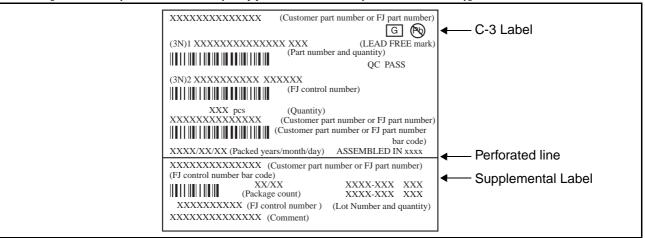

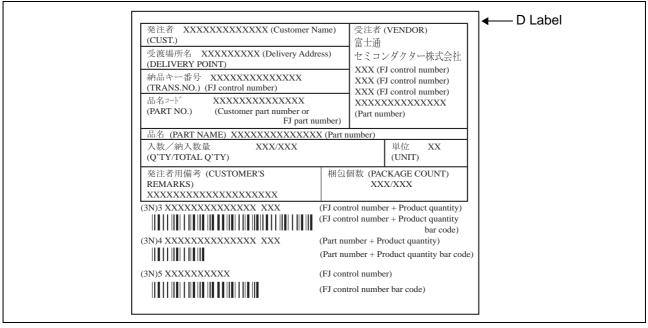

#### 1.3 Product label indicators

Label I: Label on Inner box/Moisture Barrier Bag/ (It sticks it on the reel for the emboss taping)

[C-3 Label (50mm x 100mm) Supplemental Label (20mm x 100mm)]

Label II-A: Label on Outer box [D Label] (100mm x 100mm)

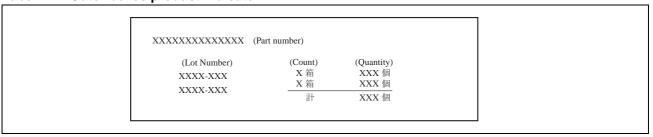

Label II-B: Outer boxes product indicate

Note: Depending on shipment state, "Label II-A" and "Label II-B" on the external boxes might not be printed.

# MB85R4001A

#### 1.4 Dimensions for Containers

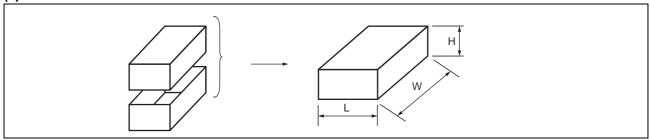

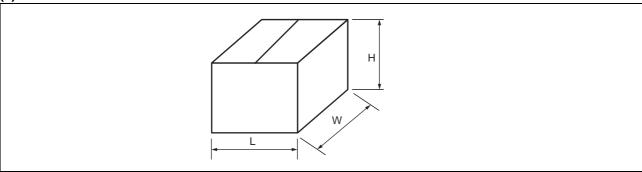

### (1) Dimensions for inner box

| L   | W   | Н  |

|-----|-----|----|

| 165 | 360 | 75 |

(Dimensions in mm)

### (2) Dimensions for outer box

| L   | W   | Н   |

|-----|-----|-----|

| 355 | 385 | 195 |

(Dimensions in mm)

## **■ MAJOR CHANGES IN THIS EDITION**

A change on a page is indicated by a vertical line drawn on the left side of that page.

| Page | Section                   | Change Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ■ FEATURES                | Revised the Data retention<br>10 years ( + 55 °C)<br>→10 years ( + 55 °C), 55 years ( + 35 °C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4    | ■ ABSOLUTE MAXIMUM RANGES | Revised the Storage Temperature $-40 ^{\circ}\text{C} \rightarrow -55 ^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11   | ■ POWER ON/OFF SEQUENCE   | Deleted the following description:  "Because turning the power-on from an intermediate level cause malfunction, when the power is turned on, VDD is required to be started from OV (see the figure below)."  Moved the following description under the table:  "If the device does not operate within the specified conditions of read cycle, write cycle or power on/off sequence, memory data can not be guaranteed. In case the power is turned on or off, use the power supply reset IC and fix the CE2 to low level, to prevent unexpected writing. Use either of CE1 or CE2, or both to disable control of the device." |

|      | ■ FRAM CHARACTERISTICS    | Revised the table and Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### Europe

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 902 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fsk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://sg.fujitsu.com/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. 30F, Kerry Parkside, 1155 Fang Dian Road, Pudong District, Shanghai 201204, China

Tel: +86-21-6146-3688 Fax: +86-21-6146-3660

http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 2/F, Green 18 Building, Hong Kong Science Park, Shatin, N.T., Hong Kong

Tel: +852-2736-3232 Fax: +852-2314-4207

http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department