# Four-Channel, Low Phase Noise, Low Power, Continuous Wave Transmitter

### **Features**

- Low phase noise

- 100V open drain N-channel

- High speed D flip-flop

- High speed MOSFET gate driver

- Up to 200MHz clock input

- V<sub>DD</sub> and V<sub>LL</sub> undervoltage lockout

### **Applications**

- Diagnostic medical ultrasound

- Fluid flow measurement

### **General Description**

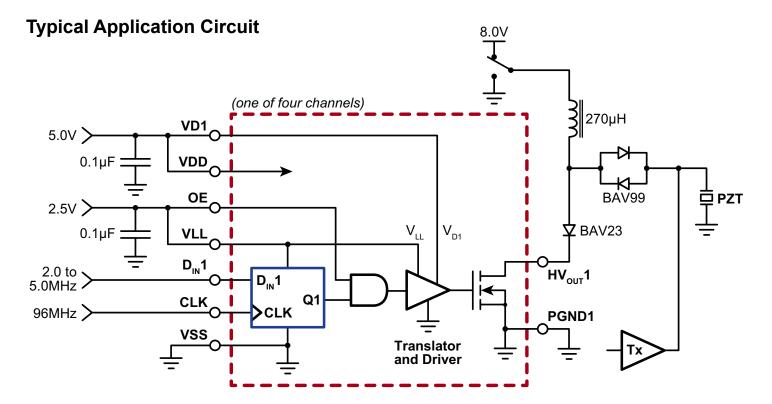

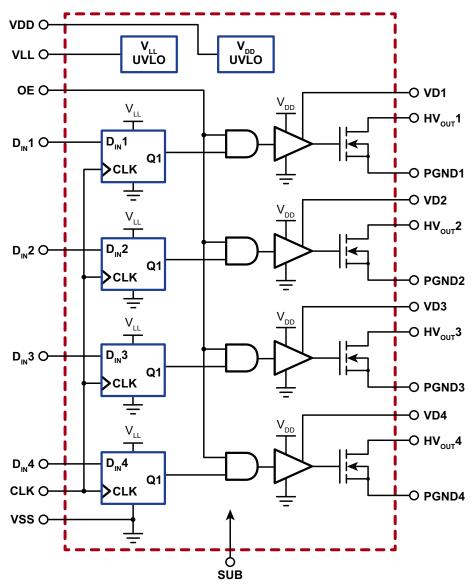

The Supertex CW01 is a four-channel, low phase noise, continuous wave transmit IC. A high speed D flip-flop is provided to allow the  $D_{\rm IN}$  frequency to be aligned to a high frequency clock. The output N-channel is turned on when a logic high is clocked into the D flip-flop. Data are clocked in during the low to high transition.

VD1, VD2, VD3 and VD4 are four individual input supply voltages for the N-channel output MOSFET gate drivers. High peak currents are drawn from these gate drives when the output MOSFETs are switching. To minimize jitter caused by voltage ripples, each channel has its own gate drive voltage pin; VD1, VD2, VD3 and VD4. A series ferrite bead and a decoupling capacitor are recommended on each VDX pin to minimize output jitter and channel to channel crosstalk.

Both  $V_{\rm DD}$  and  $V_{\rm LL}$  have undervoltage lockout to prevent spurious turn-on.

## **Ordering Information**

| Device | Package Option                                                      |

|--------|---------------------------------------------------------------------|

|        | 24-Lead QFN<br>4.00x5.00mm body<br>1.00mm height (max) 0.50mm pitch |

| CW01   | CW01K6-G                                                            |

-G indicates package is RoHS compliant ('Green')

## **Absolute Maximum Ratings**

| Parameter                                             | Value             |  |  |

|-------------------------------------------------------|-------------------|--|--|

| V <sub>LL</sub> , logic supply                        | -0.3 to +6.0V     |  |  |

| V <sub>DD</sub> , level translator voltage            | -0.5 to +6.0V     |  |  |

| V <sub>DX</sub> , gate drive voltage                  | -0.5 to +6.0V     |  |  |

| HV <sub>OUT</sub> , high voltage output drain voltage | -0.5 to 120V      |  |  |

| Maximum junction temperature                          | +125°C            |  |  |

| Storage temperature range                             | -65°C to +150°C   |  |  |

| Power dissipation, T <sub>A</sub> = 25°C              | 3.0W <sup>1</sup> |  |  |

| $\theta_{ja}$                                         | 26.9°C/W          |  |  |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

### Note:

1. Device mounted on a 4 layer 3" by 4" board.

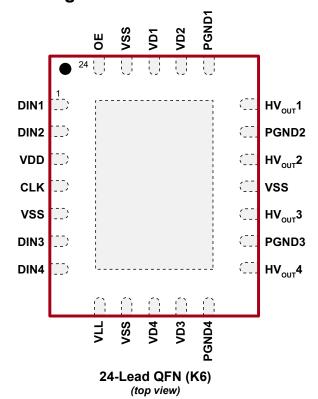

### **Pin Configuration**

## **Product Marking**

Package may or may not include the following marks: Si or

24-Lead QFN (K6)

DC Electrical Characteristics  $(V_{DD} = V_{DX} = 5.0V, V_{LL} = 2.5V, T_{J} = 25^{\circ}C \text{ unless otherwise specified})$

| Symbol               | Parameter                           |                    | Тур  | Max                | Unit | Test Conditions                                         |

|----------------------|-------------------------------------|--------------------|------|--------------------|------|---------------------------------------------------------|

| HV <sub>out</sub>    | High voltage output                 | 0                  | -    | 100                | V    |                                                         |

| $V_{DD}$             | V <sub>DD</sub> voltage range       | 4.5                | 5.0  | 5.5                | V    |                                                         |

| t <sub>vdd-on</sub>  | V <sub>DD</sub> rise time           | 50                 | -    | -                  | μs   |                                                         |

| V <sub>LL</sub>      | V <sub>LL</sub> voltage range       | 1.65               | 2.5  | 5.5                | V    |                                                         |

| t <sub>vll-on</sub>  | V <sub>LL</sub> rise time           | 50                 | -    | -                  | μs   |                                                         |

| V <sub>DIN</sub>     | Logic input voltage range           | 0                  | -    | V <sub>LL</sub>    | V    |                                                         |

| $V_{DX}$             | Gate drive voltage                  | 4.5                | 5.0  | 5.5                | V    |                                                         |

| t <sub>vdx-on</sub>  | V <sub>DX</sub> rise time           | 50                 | -    | -                  | μs   |                                                         |

| I <sub>DDQ</sub>     | V <sub>DD</sub> quiescent current   | -                  | 63   | 100                | μA   |                                                         |

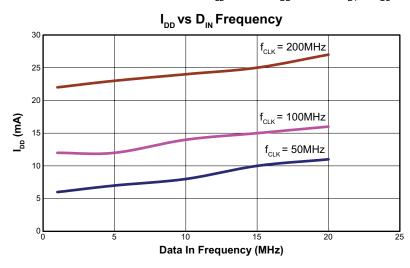

| I <sub>DD</sub>      | V <sub>DD</sub> average current     | -                  | 23.5 | 30                 | mA   | $f_{CLK}$ = 200MHz, $f_{OUT}$ = 5.0MHz, all 4-ch active |

| I <sub>LLQ</sub>     | V <sub>LL</sub> quiescent current   | -                  | 8.1  | 20                 | μA   |                                                         |

| I <sub>LL</sub>      | V <sub>LL</sub> average current     | -                  | 380  | 600                | μA   | $f_{CLK}$ = 200MHz, $f_{OUT}$ = 5.0MHz, all 4-ch active |

| I <sub>DXQ</sub>     | V <sub>DX</sub> quiescent current   | -                  | 0    | 1.0                | μA   |                                                         |

| I <sub>DX</sub>      | V <sub>DX</sub> average current     | -                  | 11.3 | 30                 | mA   | $f_{CLK}$ = 200MHz, $f_{OUT}$ = 5.0MHz, all 4-ch active |

| V <sub>IH</sub>      | Input logic high voltage            | 0.8V <sub>LL</sub> | -    | V <sub>LL</sub>    | V    |                                                         |

| V <sub>IL</sub>      | Input logic low voltage             | 0                  | -    | 0.2V <sub>LL</sub> | V    |                                                         |

| I <sub>IH</sub>      | Input logic high current            | -                  | -    | 1.0                | μA   |                                                         |

| I                    | Input logic high current            | -1.0               | -    | -                  | μA   |                                                         |

| R <sub>on</sub>      | Output on resistance                | -                  | 4.7  | 7.0                | Ω    | I <sub>IN</sub> = 100mA                                 |

| I <sub>SAT</sub>     | Output saturation current           | -                  | 0.8  | -                  | Α    | $V_{DD} = HV_{OUT} = 5.0V$                              |

| <br>HVleak           | High voltage output leakage         | -                  | -    | 10                 | μA   | HV <sub>OUT</sub> = 100V                                |

| UVLO_V <sub>LL</sub> | UVLO trip point for V <sub>LL</sub> | -                  | 1.5  | -                  | V    |                                                         |

| UVLO_V <sub>DD</sub> | UVLO trip point for V <sub>DD</sub> | -                  | 4.0  | -                  | V    |                                                         |

| T <sub>J</sub>       | Operating junction temperature      | -40                | -    | +125               | °C   |                                                         |

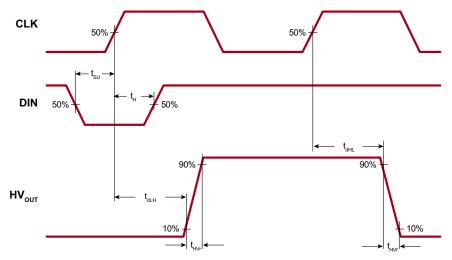

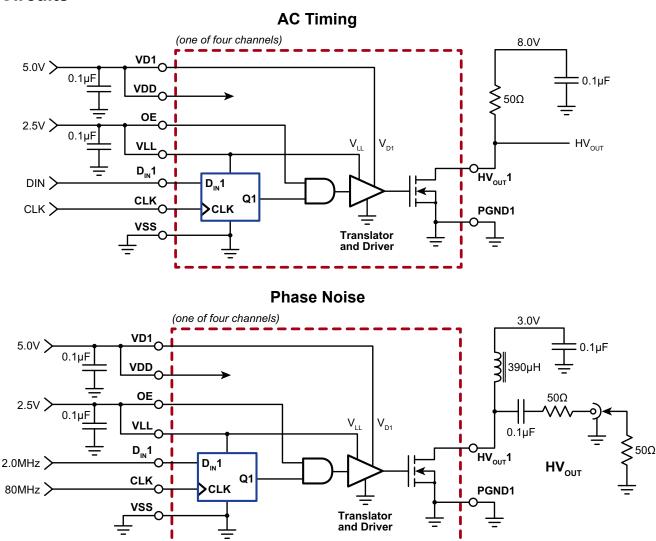

**AC Electrical Characteristics**  $(V_{DD} = V_{DX} = 5.0V, V_{LL} = 2.5V, T_J = 25^{\circ}C \text{ unless otherwise specified})$

| Symbol                          | Parameter                                                 | Min | Тур  | Max  | Unit   | Test Conditions                                                                                                       |

|---------------------------------|-----------------------------------------------------------|-----|------|------|--------|-----------------------------------------------------------------------------------------------------------------------|

| f <sub>CLK</sub>                | Clock frequency                                           | 0   | -    | 200  | MHz    | -                                                                                                                     |

| t <sub>r</sub> , t <sub>f</sub> | Clock rise and fall times                                 | -   | 0.5  | 5.0  | ns     | -                                                                                                                     |

| t <sub>su</sub>                 | Set-up time, DIN to CLK                                   | 2.0 | -    | -    | ns     | -                                                                                                                     |

| t <sub>H</sub>                  | Hold time, DIN from CLK                                   | 1.0 | -    | -    | ns     | -                                                                                                                     |

| t <sub>HVf</sub>                | HV <sub>out</sub> fall time                               | -   | 0.8  | -    | ns     | Load = $50\Omega$ to 8.0V.<br>See timing diagram                                                                      |

| t <sub>HVr</sub>                | HV <sub>OUT</sub> rise time                               | -   | 3.3  | -    | ns     | Load = $50\Omega$ to 8.0V.<br>See timing diagram                                                                      |

| t <sub>dLH</sub>                | Delay time from CLK to HV <sub>OUT</sub> from low to high | -   | 5.1  | -    | ns     | Load = $50\Omega$ to 8.0V.<br>See timing diagram                                                                      |

| t <sub>dHL</sub>                | Delay time from CLK to HV <sub>OUT</sub> from high to low | -   | 2.6  | -    | ns     | Load = $50\Omega$ to 8.0V.<br>See timing diagram                                                                      |

| $\Delta t_{	extsf{dLHdelay}}$   | Delay time matching for t <sub>dLH</sub>                  | -   | 0.5  | 1.0  | ns     | -                                                                                                                     |

| $\Delta t_{	ext{dHLdelay}}$     | Delay time matching for t <sub>dHL</sub>                  | -   | 0.5  | 1.0  | ns     | -                                                                                                                     |

| t <sub>OE(ON)</sub>             | Output enable turn-on time                                | -   | -    | 10   | μs     | -                                                                                                                     |

| t <sub>OE(OFF)</sub>            | Output enable turn-off time                               | -   | -    | 0.1  | μs     | -                                                                                                                     |

|                                 | Output conscitones                                        | -   | 8.0  | -    | pF     | At 8.0V                                                                                                               |

| C <sub>OUT</sub>                | Output capacitance                                        | -   | 4.0  | -    | pF     | At 100V                                                                                                               |

| Phase<br>noise                  | Phase noise                                               | -   | -171 | -160 | dBC/Hz | dB below carrier CLK = 80MHz, D <sub>IN</sub> = 2.0MHz freq offset = 1.0kHz noise bandwidth = 140Hz See test circuit. |

## **Block Diagram**

## **Timing Diagram**

### **Test Circuits**

**Typical Performance Curve** (Test conditions:  $V_{LL} = 2.5V$ ,  $V_{DD} = 5.0V$ ,  $V_{D1} = V_{D2} = V_{D3} = V_{D4} = 5.0V$ , no load)

# **Pin Configuration and Description**

| Pin#          | Function            | Description                                                                                  |

|---------------|---------------------|----------------------------------------------------------------------------------------------|

| 1             | D <sub>IN</sub> 1   | D flip-flop logic input for HV <sub>OUT</sub> 1. Logic high will turn on output N-channel.   |

| 2             | D <sub>IN</sub> 2   | D flip-flop logic input for HV <sub>OUT</sub> 2. Logic high will turn on output N-channel.   |

| 3             | VDD                 | Level translator supply. Should be at the same potential as $V_{\scriptscriptstyle DX}$ .    |

| 4             | CLK                 | Logic clock input.                                                                           |

| 5             | VSS                 | Ground. Should be externally shorted to all PGND and VSS pins.                               |

| 6             | D <sub>IN</sub> 3   | D flip-flop logic input for HV <sub>OUT</sub> 3. Logic high will turn on output N-channel.   |

| 7             | D <sub>IN</sub> 4   | D flip-flop logic input for HV <sub>OUT</sub> 4. Logic high will turn on output N-channel.   |

| 8             | VLL                 | Logic input supply voltage.                                                                  |

| 9             | VSS                 | Ground. Should be externally shorted to all PGND and VSS pins.                               |

| 10            | VD4                 | Gate drive supply voltage for $HV_{OUT}4$ . Should be at the same potential as $V_{DD}$ .    |

| 11            | VD3                 | Gate drive supply voltage for $HV_{OUT}$ 3. Should be at the same potential as $V_{DD}$ .    |

| 12            | PGND4               | Power ground for HV <sub>OUT</sub> 4. Should be externally shorted to all PGND and VSS pins. |

| 13            | HV <sub>OUT</sub> 4 | Drain output for HV <sub>OUT</sub> 4.                                                        |

| 14            | PGND3               | Power ground for HV <sub>OUT</sub> 3. Should be externally shorted to all PGND and VSS pins. |

| 15            | HV <sub>OUT</sub> 3 | Drain output for HV <sub>OUT</sub> 3.                                                        |

| 16            | VSS                 | Ground. Should be externally shorted to all PGND and VSS pins.                               |

| 17            | HV <sub>OUT</sub> 2 | Drain output for HV <sub>OUT</sub> 2.                                                        |

| 18            | PGND2               | Power ground for HV <sub>OUT</sub> 2. Should be externally shorted to all PGND and VSS pins. |

| 19            | HV <sub>out</sub> 1 | Drain output for HV <sub>OUT</sub> 1.                                                        |

| 20            | PGND1               | Power ground for HV <sub>OUT</sub> 1. Should be externally shorted to all PGND and VSS pins. |

| 21            | VD2                 | Gate drive supply voltage for $HV_{OUT}2$ . Should be at the same potential as $V_{DD}$ .    |

| 22            | VD1                 | Gate drive supply voltage for $HV_{OUT}1$ . Should be at the same potential as $V_{DD}$ .    |

| 23            | VSS                 | Ground. Should be externally shorted to all PGND and VSS pins.                               |

| 24            | OE                  | Output enable logic input. Logic low will turn all HV <sub>OUT</sub> off.                    |

| Center<br>Pad |                     | Should be externally shorted to all PGND and VSS pins.                                       |

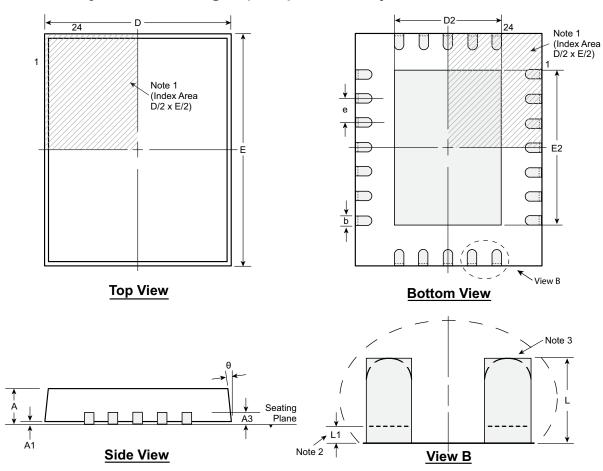

## 24-Lead QFN Package Outline (K6)

## 4.00x5.00mm body, 1.00mm height (max), 0.50mm pitch

### Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symb           | ol  | Α    | A1   | А3          | b    | D     | D2   | E     | E2   | е           | L             | L1   | θ          |

|----------------|-----|------|------|-------------|------|-------|------|-------|------|-------------|---------------|------|------------|

|                | MIN | 0.80 | 0.00 |             | 0.18 | 3.85* | 2.50 | 4.85* | 3.50 |             | <i>†</i> 0.30 | 0.00 | <b>0</b> ° |

| Dimension (mm) | NOM | 0.90 | 0.02 | 0.20<br>REF | 0.25 | 4.00  | 2.65 | 5.00  | 3.65 | 0.50<br>BSC | 0.40          | -    | -          |

| ()             | MAX | 1.00 | 0.05 | 11          | 0.30 | 4.15* | 2.80 | 5.15* | 3.80 |             | <i>†</i> 0.50 | 0.15 | 14°        |

JEDEC Registration MO-220, Variation VGHD-1, Issue K, June 2006

Drawings not to scale.

Supertex Doc.#: DSPD-24QFNK64X5P050, Version A101111.

(The package drawings in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2012 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.