# Linear, 100mA, Constant Current LED Driver with Enable Input

#### **Features**

- ► 100mA ±5% constant current drive

- Built-in reverse polarity protection

- Logic level enable

- Dimmable via EN pin

- Overtemperature protection

- 90V max rating for transient immunity

### **Applications**

- Flashlights

- Specialty lighting

- Low voltage signage

- Low voltage lighting

#### **General Description**

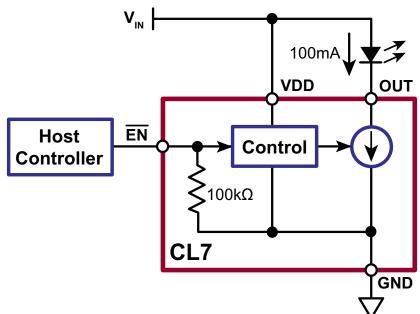

The CL7 is a linear fixed current regulator designed for driving high brightness LEDs at 100mA from nominal 12V, 24V, and 48V power supplies. With a maximum rating of 90V, it is able to withstand transients without the need for additional transient protection circuitry. The CL7 is offered in the 8-Lead SOIC package.

An active low enable input  $(\overline{EN})$  allows logic level control of the LED for on/off control or PWM dimming. The enable input has 100k $\Omega$  pull-down resistance. For applications not needing an enable input, refer to the CL6 data sheet.

Over temperature protection shuts off the LED current when the die temperature rises above  $135^{\circ}C$  (nominal). Full LED current resumes when the die temperature falls below  $105^{\circ}C$  (nominal).

## **Typical Application Circuit**

# **Ordering Information**

| Part Number | Package Options           | Packing   |  |  |

|-------------|---------------------------|-----------|--|--|

| CL7SG-G     | 8-Lead SOIC (w/heat slug) | 2500/Reel |  |  |

-G denotes a lead (Pb)-free / RoHS compliant package

# **Absolute Maximum Ratings**

| Parameter                        | Value           |

|----------------------------------|-----------------|

| Supply voltage, V <sub>DD</sub>  | -25V to +100V   |

| Output voltage, V <sub>OUT</sub> | -25V to +100V   |

| Enable voltage, $V_{EN}$         | -0.5V to +6.5V  |

| Operating junction temperature   | -40°C*          |

| Storage temperature              | -65°C to +150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### Note:

Maximum junction temperature internally limited.

#### **Typical Thermal Resistance**

| Package                           | θ <sub>ja</sub> |

|-----------------------------------|-----------------|

| 8-Lead SOIC (w/heat slug)         | 84°C/W*         |

| * Mounted on JEDEC test PCB (2s 2 | ·(p)            |

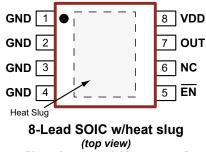

# **Pin Configuration**

# **Product Marking**

| CL7 |

|-----|

|-----|

Year Sealed = Week Sealed ot Number \_\_\_ = "Green" Packaging

Package may or may not include the following marks: Si or 8-Lead SOIC w/heat sug

#### **Pin Designation**

|     | U      |                                                                                        |

|-----|--------|----------------------------------------------------------------------------------------|

| Pin | Name   | Description                                                                            |

| VDD | VDD    | Supply voltage for the CL7                                                             |

| OUT | Output | Connect the LED between this pin and the supply voltage                                |

| GND | Ground | Circuit common                                                                         |

| ĒN  | Enable | Active low enable input - this input has an internal $100k\Omega$ pull-down resistance |

#### Recommended Operating Conditions (all voltages with respect to GND pin)

| Sym              | Parameter                                         |                    | Min        | Тур | Max      | Units | Conditions |

|------------------|---------------------------------------------------|--------------------|------------|-----|----------|-------|------------|

| V <sub>DD</sub>  | Supply voltage                                    | Normal<br>Extended | 6.5<br>6.5 | -   | 28<br>90 | V     |            |

| V <sub>OUT</sub> | Voltage at OUT pin <sup>(1)</sup> Normal Extended |                    | 4.0<br>4.0 | -   | 28<br>90 | V     |            |

| $T_{J}$          | Junction temperature <sup>(2</sup>                | -40                | -          | 119 | °C       |       |            |

Note:

Continuous operation at high V<sub>OUT</sub> voltages may result in activation of over temperature protection. Use appropriate heat sinking. 1.

Maximum junction temperature internally limited. 2.

#### Thermal Characteristics (Guaranteed by design - not production tested)

| Sym              | Parameter                   | Min | Тур | Max | Units | Conditions |

|------------------|-----------------------------|-----|-----|-----|-------|------------|

| T                | Over-temperature limit      | 120 | 135 | 150 | °C    |            |

| T <sub>HYS</sub> | Over-temperature hysteresis | -   | 30  | -   | °C    |            |

#### **Electrical Characteristics**

(Over normal recommended operating conditions unless otherwise specified. All voltages with respect to GND pin. Production tested @ 25°C.)

| Sym                   | Parameter                                                     | Min            | Тур             | Max               | Units | Conditions                                                                                  |

|-----------------------|---------------------------------------------------------------|----------------|-----------------|-------------------|-------|---------------------------------------------------------------------------------------------|

| I <sub>DD</sub>       | Current into VDD pin                                          | 3.0            | 5.0             | 10                | mA    |                                                                                             |

| I <sub>out</sub>      | Current into OUT pin <sup>1</sup>                             | 95<br>90<br>50 | 100<br>100<br>- | 105<br>110<br>120 | mA    | Normal conditions, 25°C<br>Normal conditions, full temp <sup>2</sup><br>Extended conditions |

| I <sub>OUT(OFF)</sub> | Current into OUT pin with VDD pin open or $\overline{EN} = 1$ | -              | -               | 10                | μA    | V <sub>DD</sub> = open                                                                      |

| V <sub>EN(ON)</sub>   | Enable voltage, on                                            | -              | -               | 0.8               | V     |                                                                                             |

| V <sub>EN(OFF)</sub>  | Enable voltage, off                                           | 2.4            | -               | -                 | V     |                                                                                             |

| R <sub>EN</sub>       | Enable pull-down resistance                                   | -              | 100             | -                 | kΩ    |                                                                                             |

| V <sub>OFF</sub>      | Voltage at VDD to shut off LED current                        | -              | -               | 1.0               | V     | Ι <sub>ουτ</sub> < 10μΑ                                                                     |

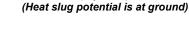

| t <sub>on</sub>       | On delay, EN to OUT                                           | -              | 3.0             | -                 | μs    | ĒN = 0V                                                                                     |

| t <sub>off</sub>      | Off delay, $\overline{EN}$ to OUT                             | -              | 0.1             | -                 | μs    | ĒN = 5V                                                                                     |

| t <sub>RISE</sub>     | Current rise time, $\overline{EN}$ to OUT                     | -              | 4.0             | -                 | μs    | ĒN = 0V                                                                                     |

| t <sub>FALL</sub>     | Current fall time, $\overline{EN}$ to OUT                     | -              | 0.3             | -                 | μs    | <u>EN</u> = 5V                                                                              |

Note:

Continuous operation at high  $V_{out}$  voltages may result in activation of over temperature protection. Use appropriate heat sinking. Maximum junction temperature internally limited. 1.

2.

# Timing

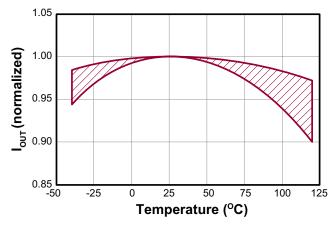

# I<sub>out</sub> vs Temperature

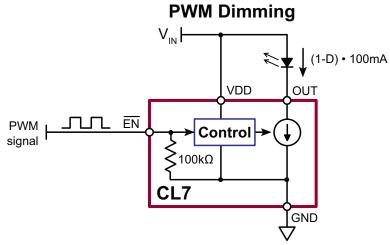

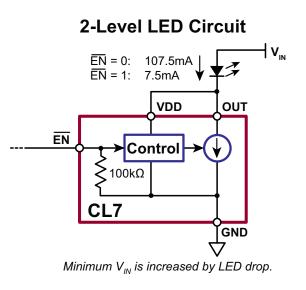

# **Application Circuits**

D is the portion of time the PWM signal is high.

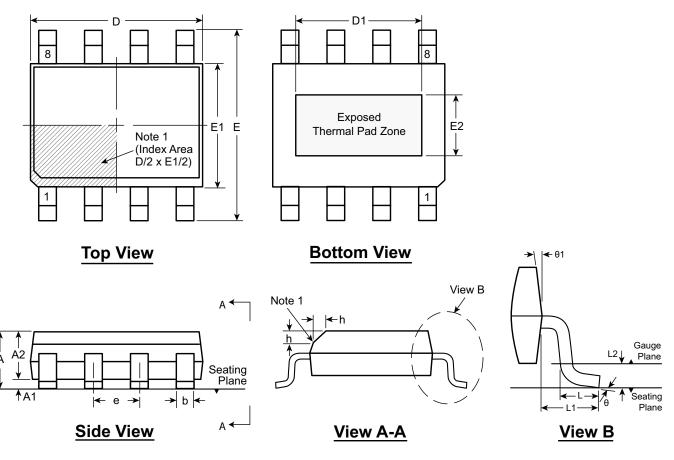

# 8-Lead SOIC (Narrow Body w/Heat Slug) Package Outline (SG) 4.90x3.90mm body, 1.70mm height (max), 1.27mm pitch

#### Notes:

1. If optional chamfer feature is not present, a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/ identifier; an embedded metal marker; or a printed indicator.

| Symbo             | ol  | Α     | A1   | A2    | b    | D     | D1                | E     | E1    | E2                | е           | h    | L    | L1          | L2          | θ          | θ1              |

|-------------------|-----|-------|------|-------|------|-------|-------------------|-------|-------|-------------------|-------------|------|------|-------------|-------------|------------|-----------------|

|                   | MIN | 1.25* | 0.00 | 1.25  | 0.31 | 4.80* | 3.30 <sup>†</sup> | 5.80* | 3.80* | 2.29†             |             | 0.25 | 0.40 |             |             | <b>0</b> 0 | <b>5</b> °      |

| Dimension<br>(mm) | NOM | -     | -    | -     | -    | 4.90  | -                 | 6.00  | 3.90  | -                 | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -               |

| (mm)              | MAX | 1.70  | 0.15 | 1.55* | 0.51 | 5.00* | 3.81 <sup>†</sup> | 6.20* | 4.00* | 2.79 <sup>†</sup> | DOO         | 0.50 | 1.27 |             | вее         | <b>8</b> 0 | 15 <sup>0</sup> |

JEDEC Registration MS-012, Variation BA, Issue E, Sept. 2005.

\* This dimension is not specified in the JEDEC drawing.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc. #: DSPD-8SOSG, Version D041009.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.