# UM0169 User manual

# Configuration and programming software (CAPS) tool for µPSD families

# Introduction

Configuration and Programming Software (CAPS) is the configuration software for the  $\mu$ PSD family microcontroller. The CAPS configuration tool allows you to easily configure the  $\mu$ PSD using simple dragand-drop and point-and-click operations. CAPS also supports In-System-Programming through an external JTAG adapter, allowing fast In-System-Programming of  $\mu$ PSD in development or even in production.

This is the user manual for CAPS. The purpose of this manual is to explain CAPS software functionality. When working with the CAPS tool, you are also encouraged to download the datasheet associated with your particular device; the datasheet may provide the only source of important configuration information needed for your design.

*Getting started* gives an introduction to device configuration and programming, and the CAPS features. This section also describes CAPS installation procedures. Although installation may seem trivial, it is highly recommended that you carefully follow the instructions because many problems are often caused by incorrectly installing CAPS.

This is followed by the *Introduction to CAPS* section, which introduces the CAPS *Design Flow* and menu environment. An example of a simple project is included as a way to quickly familiarize you with basic concepts and the user interface.

The *Using the wizard* and *Working in advanced mode* sections give more detailed information about how to use CAPS features. These sections describe the user interface for common design functions, for the various CAPS modes of operation.

The appendices provide reference material useful for design and analysis.

| 1 | Gettir | ng started                                                     |

|---|--------|----------------------------------------------------------------|

|   | 1.1    | Installation 4                                                 |

|   |        | 1.1.1 System requirements                                      |

|   |        | 1.1.2 Installing CAPS                                          |

|   |        | 1.1.3 Uninstalling CAPS                                        |

|   | 1.2    | Setting up the target hardware 5                               |

|   | 1.3    | How to use this manual 5                                       |

|   | 1.4    | Recommended reading 6                                          |

| 2 | Introc | luction to CAPS                                                |

|   | 2.1    | Project development                                            |

|   | 2.2    | The user interface                                             |

|   |        | 2.2.1 The project menu                                         |

|   |        | 2.2.2 The tools menu                                           |

|   |        | 2.2.3 The edit menu                                            |

|   |        | 2.2.4 The view menu                                            |

|   |        | 2.2.5 The help menu                                            |

|   | 2.3    | Starting a project                                             |

|   |        | 2.3.1 Creating a new project                                   |

|   |        | 2.3.2 Opening an existing project                              |

|   |        | 2.3.3 Choosing a design method16                               |

|   | 2.4    | An example using the DK3400 17                                 |

|   |        | 2.4.1 Creating a new project                                   |

|   |        | 2.4.2 Designing your project                                   |

|   |        | 2.4.3 Programming your target device                           |

|   |        | 2.4.4 Ending your CAPS session                                 |

| 3 | Using  | the wizard                                                     |

|   | 3.1    | Specifying the memory map 30                                   |

|   | 3.2    | Firmware placement                                             |

|   | 3.3    | Specifying external chip selects                               |

|   | 3.4    | Setting security and sector protection, and fitting the design |

|   | 3.5    | Validating and programming the target device                   |

|   |        | 3.5.1 File checksum                                            |

|   |        | 3.5.2 Target device setup and validation                       |

|   |        | 3.5.3 Reset hardware                                           |

|   |        |                                                                |

|   |      | 3.5.4    | Program target device                          | . 32 |

|---|------|----------|------------------------------------------------|------|

|   | 3.6  | Ending   | g the wizard session                           | 32   |

|   |      |          |                                                |      |

| 4 | Work | ing in a | advanced mode                                  | 33   |

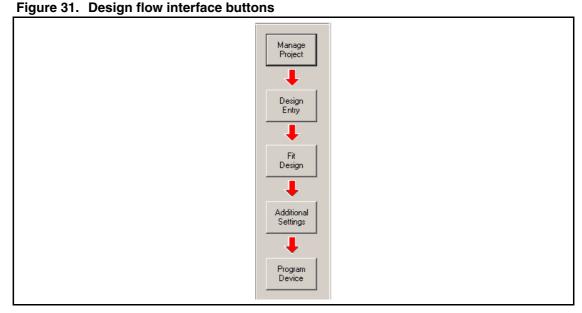

|   | 4.1  | Desigr   | ח flow                                         | 33   |

|   |      | 4.1.1    | Manage project dialog                          | . 34 |

|   |      | 4.1.2    | Design entry forms                             | . 35 |

|   |      | 4.1.3    | Fit design command                             | . 35 |

|   |      | 4.1.4    | Additional settings form                       | . 35 |

|   |      | 4.1.5    | Program device form                            | . 36 |

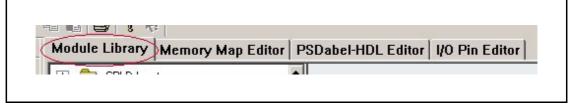

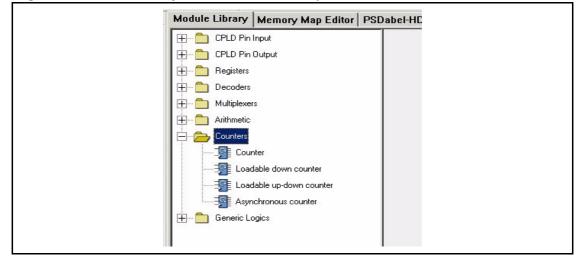

|   | 4.2  | Using    | the module library                             | 36   |

|   |      | 4.2.1    | Adding and editing a logic module              | . 37 |

|   |      | 4.2.2    | Deleting a logic module                        | . 38 |

|   |      | 4.2.3    | Connecting modules                             | . 38 |

|   | 4.3  | Specif   | ying the memory map                            | 38   |

|   |      | 4.3.1    | Using the memory map template                  | . 39 |

|   |      | 4.3.2    | Other memory map editor functions              | . 40 |

|   | 4.4  | Firmw    | are placement                                  | 41   |

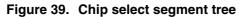

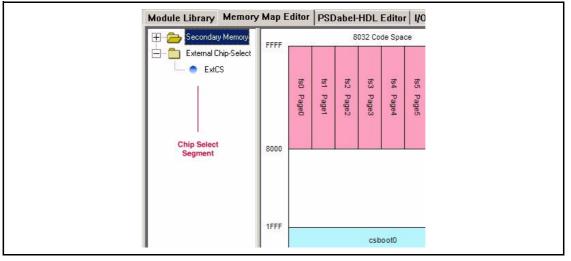

|   | 4.5  | Specif   | ying chip selects                              | 42   |

|   |      | 4.5.1    | Defining chip selects in graphical mode        | . 42 |

|   |      | 4.5.2    | Using direct entry mode to define chip selects | . 43 |

|   | 4.6  | Editing  | PSDabel-HDL code                               | 44   |

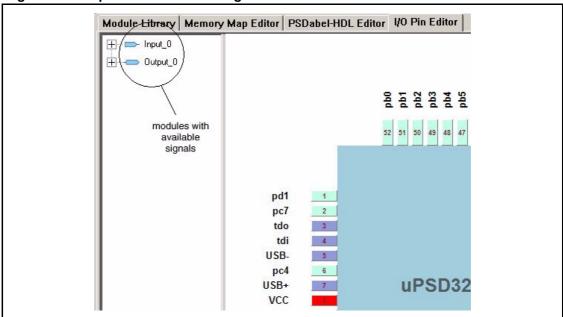

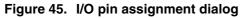

|   | 4.7  | Specif   | ying I/O pin assignment                        | 45   |

|   |      | 4.7.1    | Assign a signal to a pin                       | . 46 |

|   |      | 4.7.2    | Unassign a signal to a pin                     | . 48 |

|   |      | 4.7.3    | Assign a configurable function to a pin        | . 48 |

|   | 4.8  | Fitting  | the design                                     | 48   |

|   | 4.9  | Setting  | g security                                     | 49   |

|   | 4.10 | Setting  | g a JTAG/ISP user code                         | 49   |

|   | 4.11 | Setting  | g sector protection                            | 50   |

|   | 4.12 | Valida   | ting and programming the target device         | 50   |

|   |      |          | JTAG-ISP operations for single device view     |      |

|   |      | 4.12.2   | JTAG-ISP operations for multiple device view   | . 54 |

|   |      |          | Compute checksum                               |      |

|   |      |          | Generate ATE file                              |      |

|   |      | 4.12.5   | Target hardware operations                     | . 59 |

|   |      |          |                                                |      |

|                 | 4.12.6    | Assert/de-assert reset                |

|-----------------|-----------|---------------------------------------|

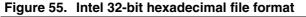

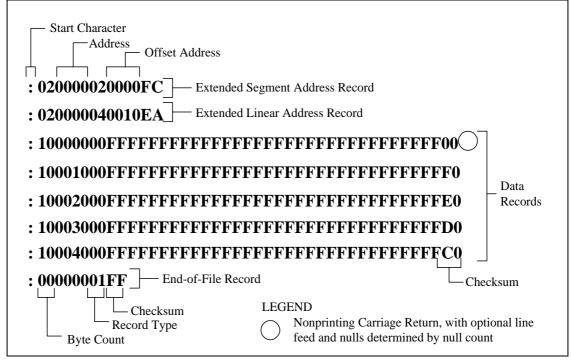

| Appendix        | A Intel h | hex-32 record format61                |

| A. <sup>-</sup> | I Data re | ecord                                 |

| A.2             | 2 End re  | ecord                                 |

| A.3             | B Extend  | ded segment address record 62         |

| A.4             | 4 Extend  | ded linear address record 62          |

| Appendix        | B Projec  | ct Report                             |

| Appendix        | C Flash   | LINK Cable – Install fast JTAG driver |

| C.*             | 1 Driver  | installation                          |

| C.2             | P Worka   | round solutions                       |

|                 |           |                                       |

# **1** Getting started

Before using CAPS, you must install the software on your PC and, also, connect your target device, if you plan to program the device.

This section discusses the following topics needed to begin using the CAPS software.

- CAPS software installation.

- Setting up the target hardware.

- The recommended approach to using this manual.

- Complementary documentation considered to be useful when using the CAPS software.

# 1.1 Installation

This section describes the requirements and procedures needed to install the CAPS software.

#### 1.1.1 System requirements

The CAPS PC configuration minimally requires:

- PC with an Intel Pentium processor running a 32-bit Microsoft Operating System:

- Microsoft Windows XP

- Windows 2000

- Windows 98

- Windows ME

- Windows NT with Service Pack 6

- 32 MB RAM

- 25 MB hard disk space available

- Note: To use RLINK-ST, a USB port is required with a USB-supporting Windows Operating System (Win98SE, Win2000, Me, XP). Note that Win95, Win98 First Edition and NT4.0 do NOT support USB.

- **Caution:** FlashLINK Cable: JTD driver (OD) is NOT supported on dual-processor systems or hyperthreading enabled systems. Refer to *Appendix C: FlashLINK Cable – Install fast JTAG driver*, for workaround options for both dual-processor and hyperthreading systems.

# 1.1.2 Installing CAPS

Follow these procedures and the on-screen instructions to install CAPS.

- 1. Download the compressed CAPS software from the website.

- 2. Extract the contents of the *.zip* file into a temporary directory.

- 3. Double-click the extracted executable, *setup.exe*, to initiate the installation, and follow the on-screen prompts to install CAPS in the development environment. This executable installs all the necessary files and configures the PC environment for running CAPS. You may be prompted to restart your PC before running CAPS for the first time following the installation.

CAPS installation includes a number of utilities. Documentation for the utilities is located in the subdirectory \*Docs* where CAPS is installed.

| Utility Executable | Description                                                                    |  |  |

|--------------------|--------------------------------------------------------------------------------|--|--|

| ObjFileEditor.exe  | Programming data file (.OBJ) editor.                                           |  |  |

| uFLink.exe         | Standalone JTAG/ISP programming utility.                                       |  |  |

| uMerge.exe         | Merge firmware utility.                                                        |  |  |

| uObjOsf.exe        | Program data file conversion utility. Convert obj-to-osf and osf-to-obj files. |  |  |

Table 1. CAPS utility programs

Subdirectory *Projects* is also created, and is the default location for storing your CAPS project files. For example, if CAPS is installed in base directory *C*:\*CAPS*, the *Projects* directory is located at *C*:\*CAPS*\*Projects*.

#### 1.1.3 Uninstalling CAPS

To uninstall CAPS, select **Start | Programs | STMicroelectronics - CAPS | Uninstall CAPS**. This removes all CAPS executable software and desktop references.

Note: Any project files and environment files are preserved so they are available following a CAPS software upgrade. However, it is a safe practice to backup your project files before uninstalling and reinstalling the software.

# 1.2 Setting up the target hardware

If you are using CAPS features that interact with the target hardware, such as programming the flash, configure and power the target hardware before starting a CAPS session. (Refer to the the User Guide for your particular target hardware, found at http://www.st.com/mcu/).

- Note: 1 The device under test must be the same as the target device you select when you create your project.

- *2* Follow the instructions below referring to the device-specific quick start guide or design guide as needed.

- 1. Connect either the RLINK-ST USB cable or the FlashLINK parallel cable to your PC, and connect the other end of the JTAG interface to the target board.

- 2. Configure jumpers according to the quick start or design guide documentation for the target board.

- 3. Attach the power plug to the power jack of the target board.

- 4. Switch ON the target board.

### **1.3** How to use this manual

Use these recommendations as a guide to learning the CAPS software.

- Read *Getting started* to learn what CAPS is and to install the software for the first time.

- Read *Introduction to CAPS* to get a basic understanding of CAPS procedures and an understanding of the user interface fundamentals. The section provides a quickstart for understanding CAPS. More advanced users may skip this section.

- Read *Using the wizard* to learn how to design with CAPS, using the wizard assistant. This section provides a reference for the wizard mode of operation.

- Users with more complex design requirements beyond the scope of the wizard templates should read *Working in advanced mode*. This section provides a reference for the advanced mode of operation.

# 1.4 Recommended reading

You are also encouraged to download the datasheet associated with a particular device. The datasheet may be the only source of important configuration information needed for your design.

# 2 Introduction to CAPS

This section introduces you to CAPS, presenting the following topics:

- Project development steps and considerations.

- A reference for the CAPS user interface.

- Beginning steps needed to start a project.

- An example of a simple project, using the wizard mode of operation.

# 2.1 Project development

The CAPS software guides the designer through the process of configuring a target device for a particular application, using the following project development steps.

- 1. Create a unique project for each device under test/application combination.

- Automatically generate the Hardware Description Language (HDL) for the PLD logic, given address decoding, paging, segmentation, chip selects, general-purpose logic and I/ O pin assignments.

- 3. "Fit" the design to the silicon architecture, merging the design with your Intel hex-format firmware file.

- 4. Program the resulting programming data file into the device under test.

- 5. Save your project to a file for later use.

# 2.2 The user interface

This section is a reference for the CAPS user interface. To learn how to begin using the interface to work with a project, see *Starting a project*.

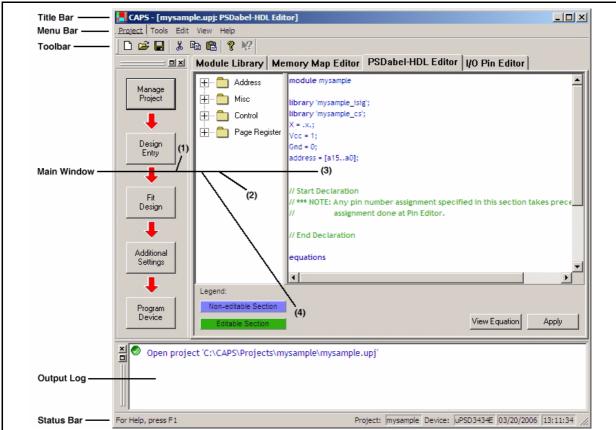

*Figure 1: CAPS user interface* shows the basic CAPS user interface components, followed by a brief description of each component. Following subsections describe the menu bar selections in more detail. Components and functionality specific to the different modes of operation are described in *Using the wizard* and *Working in advanced mode*.

The CAPS software is a Windows-based program. As such, the user interface implements basic interface functionality commonly found in Windows programs.

#### Figure 1. CAPS user interface

Menu barUse the menu bar to access these CAPS design functions:<br/>The project menu, The tools menu, The edit menu, The view<br/>menu and The help menu. (These functions are described<br/>in more detail beginning with 2.2.1: The project menu.ToolbarThe toolbar provides quick access to common menu bar<br/>functions, including:

- Create a new project.

- Open an existing project.

- Save a project.

- File editing functions: cut, copy and paste.

- Help using CAPS.

| Main window       | The main window displays the CAPS design entry forms.<br>The window may consist of multiple panes, depending on<br>the current design function.                                                                                                                                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | <ul> <li><i>Figure 1: CAPS user interface</i> is an example of a window with four panes, from the advanced mode of operation:</li> <li>A navigation pane to the left.</li> <li>A design function selection pane to the right.</li> <li>A file contents window on the far right.</li> <li>A legend and command window on the bottom.</li> <li>Some modes of operation may also have function tabs across the top of the window, as shown in the example figure.</li> </ul> |

| Output log window | The output log window echoes all commands executed by CAPS along with informational and progress messages.                                                                                                                                                                                                                                                                                                                                                                |

| Note:             | This window is made visible by checking the Output Log option in the View menu.                                                                                                                                                                                                                                                                                                                                                                                           |

| Status bar        | <ul> <li>The status bar displays:</li> <li>Current project name.</li> <li>Target device.</li> <li>Today's date. (MM/DD/YYYY)</li> <li>Current time (HH:MM:SS)</li> </ul>                                                                                                                                                                                                                                                                                                  |

The CAPS user interface also provides the following aids to using the software.

- Descriptive pop-up error messages.

- Explicit design flow sequencing that models the actual design process.

- Detailed directions on most forms that describe input field formats and how to use the form.

- An output log to provide user interface feedback.

#### 2.2.1 The project menu

The project menu allows users to manage the project life cycle, set project preferences and exit the CAPS program.

This section describes the operations available in the project menu.

| Figure 2. | Project menu |                               |         |

|-----------|--------------|-------------------------------|---------|

|           |              | 📕 CAPS - [mysample.upj: Modul | e Li    |

|           |              |                               |         |

|           |              | Project Tools View Help       |         |

|           |              |                               | 42<br>1 |

|           |              | Open Project                  | irar    |

|           |              | Close Project                 |         |

|           |              | Save Project                  |         |

|           |              | Save As Project               |         |

|           |              | Change Target Device          |         |

|           |              | Delete Project                |         |

|           |              | Import PSDsoft Project        |         |

|           |              | Recent Projects               |         |

|           |              | Preference                    |         |

|           |              | About                         |         |

|           |              | Exit CAPS                     |         |

|           |              |                               |         |

|           |              |                               |         |

| New Project          | Creates a new project.                                                                                                                                                                                                                                                                                                                           |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Open Project         | Opens an existing project.                                                                                                                                                                                                                                                                                                                       |  |

| Close Project        | Closes the currently active project. Other projects previously opened within the same CAPS session remain open.                                                                                                                                                                                                                                  |  |

| Save Project         | Saves the currently active project.                                                                                                                                                                                                                                                                                                              |  |

| Save as Project      | <ol> <li>Saves the currently active project to a different file name.</li> <li>Enter the new project name (see <i>2.3.1: Creating a new project</i> for project name constraints).</li> <li>Optionally, enter or modify the project description</li> <li>Click the <b>Save</b> button.</li> </ol>                                                |  |

| Change Target Device | Selects another target device ONLY within the same<br>product family, from the expandable device tree list.<br>Changing the package type invalidates the pin re-<br>assignment done in the Pin Editor window and also requires<br>a refitting of the design. (Note that the target device may<br>only be changed when working in advanced mode). |  |

57

| Delete Project         | Deletes a project and all files associated with the project.                                                                                                                                                                                                                     |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Import PSDsoft Project | Imports an existing project created using the PSDsoft tool.                                                                                                                                                                                                                      |

| Recent Projects        | Lists the most recently opened projects. A project may be opened by double-clicking on a list entry.                                                                                                                                                                             |

| Preference             | Sets the CAPS design environment. Select either "Single device view" or "Multiple Device view" for the JTAG/ISP property. Preferences may only be changed while in advanced mode.                                                                                                |

| About<br>Note:         | <ul> <li>Displays details about a project:</li> <li>Project name.</li> <li>Project folder.</li> <li>Device family.</li> <li>Part number.</li> <li>Voltage.</li> <li>Project description.</li> <li>The project must already be open in either wizard or advanced mode.</li> </ul> |

| Exit CAPS              | Exit the CAPS program.                                                                                                                                                                                                                                                           |

### 2.2.2 The tools menu

The tools menu provides access to useful utilities for working with projects. This section describes the utilities available in the tools menu.

| Project Tools View | / Help          |        |

|--------------------|-----------------|--------|

| 🗋 🖆 Generate       | Project Report  |        |

| <b>D</b> X         | Module Library  | Memory |

| Manage             | 🕂 🖳 CPLD Inp    | ut     |

| Project            | 🛉 🕂 🗂 CPLD Out  | put    |

|                    | 🕂 🕂 💼 Registers |        |

|                    | 📕 🕂 💼 Decoders  |        |

| Generate Project Report | Produces a text file report of your design, describing the project and showing the fitting results.                                                                                                                                                                     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Once the fitting process is complete and without errors, a summary of the fitting result is displayed as a text file in a separate window. The result shows detailed resource utilization, I/O pin and configuration information, and address and data bus assignments. |

|                         | See Project Report for an example.                                                                                                                                                                                                                                      |

#### 2.2.3 The edit menu

The edit menu provides basic editing functions. These are the standard Windows *cut*, *copy* and *paste* editing functions.

Note: The edit menu item is context sensitive, and is only available when the PSDabel-HDL Editor feature is selected (4.6: Editing PSDabel-HDL code).

This section describes the operations available in the edit menu.

#### Figure 4. Edit menu

| CAPS - [my    | rsample.upj: PSDabel-HD                   |

|---------------|-------------------------------------------|

| Project Tools | Edit View Help                            |

| 🔤 🖻 🖾         | Undo Ctrl+Z                               |

|               | Cut Ctrl+X<br>Copy Ctrl+C<br>Paste Ctrl+V |

| Project       | Misc                                      |

| •             |                                           |

| Undo  | Reverses the last editing command.                                           |

|-------|------------------------------------------------------------------------------|

| Cut   | Removes the selected text, saving it in the clipboard.                       |

| Сору  | Copies the selected text to the clipboard.                                   |

| Paste | Copies the last text buffer in the clipboard to the current cursor location. |

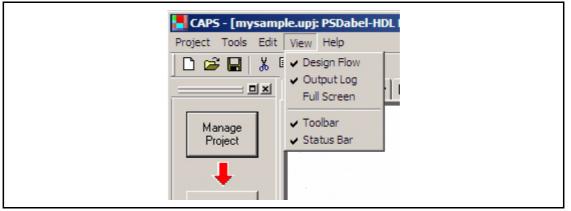

#### 2.2.4 The view menu

The view menu selection allows the user to specify the user interface panes to be displayed while working on a project. Check the menu item to enable the display.

This section describes the operations available in the view menu.

#### Figure 5. View menu

| Design Flow |       | Displays the CAPS design flow pane when working in advanced mode.                                                                             |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|             | Note: | This option is unavailable in wizard mode.                                                                                                    |

| Output Log  |       | Display the output log pane that shows commands executed by CAPS, informational and status messages ( <i>Figure 1: CAPS user interface</i> ). |

| Full Screen |       | Maximizes the CAPS display interface on the screen.                                                                                           |

| Toolbar     |       | Displays the toolbar (Figure 1: CAPS user interface).                                                                                         |

| Status Bar  |       | Displays the status bar (Figure 1: CAPS user interface).                                                                                      |

#### 2.2.5 The help menu

The help menu provides access to various links to obtain technical information about STMicroelectronics Microcontroller products and to report questions or issues related to CAPS.

This section describes the operations available in the help menu.

| Project View | Help          |                                      |      |

|--------------|---------------|--------------------------------------|------|

| 🗅 🗃 🔚        | Web Sites 🔹 🕨 | Home Page                            |      |

|              | About CAPS    | CAPS Update                          |      |

|              |               | Related Documentation and Software 🔸 | uPSD |

|              |               | FAQs                                 | STR9 |

|              |               | Forums                               |      |

| Web Sites  | Displays links to obtain technical information about<br>STMicroelectronics Microcontroller products and to report<br>questions or issues regarding CAPS. A link to Frequently<br>Asked Questions (FAQs) is also provided. (See <i>Figure 6.:</i><br><i>Help menu</i> for a list of the links provided). |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| About CAPS | Displays CAPS software version, copyright, contact and licensing information.                                                                                                                                                                                                                           |

# 2.3 Starting a project

Every CAPS session begins by opening a project. You may either create a new project or open an existing project. Once the project is opened and the basic project preferences are selected, you may choose to use either wizard mode or advanced mode to configure your project.

This section describes the beginning steps common to all projects.

#### 2.3.1 Creating a new project

Follow these steps to create a new project.

- 1. Use either the **New** icon in the toolbar or the **Project** | **New Project** ... menu item (*Figure 2.: Project menu*) to create a new project.

- 2. In the *Create Project* dialog, use the **Browse** button to specify the name of your project and directory where the project files are to be created. (The default project name is *new.upj* and the default directory is *c:\CAPS\Projects\new*; note that the default project name is the same as the directory name).

- 3. Enter an optional project description in the *Description* text box.

- 4. To accept the default project name and directory, click **Open** in the file browser dialog. To choose another directory, use the file browser to navigate to the desired directory. Then, either use the default *Project Name* or enter a new name for your project. After a new directory and project name are entered, click **Open**.

Note: The project is saved to disk only after the wizard or advanced mode procedures are successfully completed.

A valid project name,

- Can have a maximum number of 45 characters.

- Must begin with an alphanumeric character, an underscore (\_) or a tilde (~). Names are not case-sensitive.

- Cannot include symbols or punctuation marks.

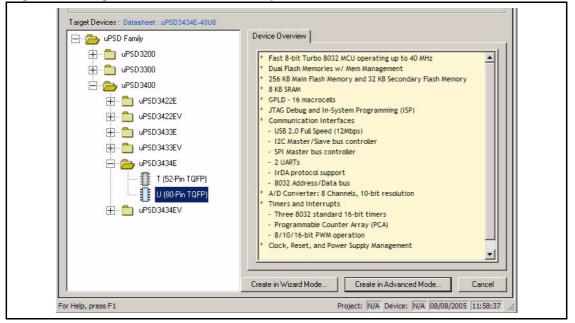

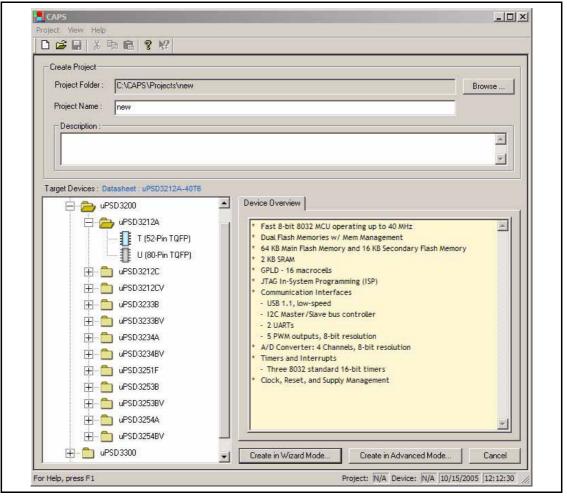

- 5. For new projects, a target device must also be specified. Using the device list tree in the *Target Devices* dialog, expand the tree until your target device appears, then click on the device icon. A description of the device appears in the *Device Overview* window to the right, and the name of the datasheet associated with the device appears in the *Target Devices* label line.

Available devices include all devices currently supported by CAPS software.

The following figure shows an example in which the 80-pin uPSD3434E device is selected.

Figure 7. Target Device Selection Example

Continue configuring your project using either wizard mode or advanced mode, according to the guidelines discussed in *2.3.3: Choosing a design method*.

#### 2.3.2 Opening an existing project

Follow these steps to open an existing project.

- 1. Use either the **Open** icon in the toolbar or the **Project** | **Open Project** ... menu item (*Figure 2.: Project menu*) to open an existing project.

- In the Open Project dialog, use the **Browse** button to use the file browser to locate the directory where your existing project file resides. A project file name with extension *.upj* is displayed. Click on the file name then click **Open** to open the file. Your previously saved project *Description* and *Target Device* are displayed.

*Note:* You may edit the project description, however, notice that the target device may not be changed.

Continue configuring your project using either wizard mode or advanced mode, according to the guidelines discussed in *2.3.3: Choosing a design method*.

#### 2.3.3 Choosing a design method

CAPS provides two modes for working with projects: wizard mode and advanced mode. Wizard mode offers a simple step-by-step approach to entering the design. It is intended for new users who are unfamiliar with many CAPS design features. Use advanced mode to access the full range of CAPS features.

One indication that advanced mode should be used rather than wizard mode is that one of the available memory maps does not meet your system requirements, for example.

For a discussion of the design facilities offered using wizard mode, refer to *Using the wizard*. For a discussion of the complete CAPS feature set, refer to *Working in advanced mode*.

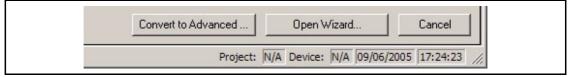

To create a project using the CAPS wizard facilities, click the **Create in Wizard Mode** button (*Figure 8.: Initial design mode option buttons*). Alternatively, click the **Create in Advanced Mode** button to create a project using advanced mode.

#### Figure 8. Initial design mode option buttons

| Create in Wizard Mode | Create in Advanced Mode          | Cancel       |

|-----------------------|----------------------------------|--------------|

|                       | Project: N/A Device: N/A 09/06/2 | 005 17:20:50 |

For an existing wizard mode project, you may choose to continue to work with the project in wizard mode or convert the project to advanced mode by clicking the appropriate button, as shown in *Figure 9.: Wizard design mode option selection buttons*.

#### Figure 9. Wizard design mode option selection buttons

Note:

: A project originally created using the wizard can be converted to advanced mode by opening the project and clicking **Convert to Advanced**. However, once the project is converted, it is not possible to revert to the wizard design mode at a later time. You may wish to first make a copy of your project before switching to advanced mode.

For an existing advanced mode project, you may only continue to work with the project in advanced mode by clicking the **Open** button, as shown in *Figure 10.: Advanced design mode option selection buttons*.

|   |                  | Open              | Cancel          |  |

|---|------------------|-------------------|-----------------|--|

| _ | Project: N/A Dev | vice: N/A 09/06/2 | 005 17:22:27 // |  |

Figure 10. Advanced design mode option selection buttons

Click Cancel in any of the design modes to quit the project.

# 2.4 An example using the DK3400

The purpose of this example is to demonstrate the basic design steps using CAPS. The example uses the wizard mode of operation to show how easy it is to design a project for the most common types of target device configurations.

We begin by creating a new project, which we name *blink\_led*. Because we intend to program the  $\mu$ PSD DK3400 development board, we choose the  $\mu$ PSD3434E, 80-pin TQFP, as the target device.

Note: This demonstration uses an example provided with the RIDE development environment. The same procedures can be used for your in-house project, choosing the target device that matches your hardware.

Next, we use the CAPS wizard to define the memory map and the firmware files to download into flash. For this example, we omit external chip selects, security and sector protection specifications.

The wizard maps the contents of the firmware files to the physical memory, translating absolute addresses to physical addresses used to program the target device. We call this "fitting" the design to the silicon architecture, which the wizard does transparently.

We then verify the communication link and operation of the target development board before programming the flash.

Finally, we close the CAPS session and save our project.

#### 2.4.1 Creating a new project

Because this is a new project, we first need to create the project. From the **Project** menu click on **New Project** ..., as shown in *Figure 11*.

```

Figure 11. Create project

```

| CAPS                                         |

|----------------------------------------------|

| Project View Help                            |

| New Project<br>Open Project<br>Close Project |

| Save Project<br>Save As Project              |

| Change Target Device                         |

| Delete Project                               |

| Import PSDsoft Project                       |

| Recent Projects                              |

| Preference                                   |

| About                                        |

| Exit CAPS                                    |

|                                              |

This displays the project dialog, shown in Figure 12.

Figure 12. New project

Click on the **Browse** ... button to enter a project name and choose a directory location for the project, using the dialog shown in *Figure 13*.

| Figure | 13. | Project | name | dialog |

|--------|-----|---------|------|--------|

|--------|-----|---------|------|--------|

| New            |                    |            | <u>?</u> × |

|----------------|--------------------|------------|------------|

| Look in: 📔     | Projects           | 💌 🗢 🖻 🖝    | <u>.</u> . |

| new            |                    |            |            |

|                |                    |            |            |

|                |                    |            |            |

|                |                    |            |            |

|                |                    |            |            |

| File name:     | new.upj            | (          | Open       |

| Files of type: | CAPS Files (*.upj) | <b>▼</b> ( | Cancel     |

You may choose another directory or accept the default project \*CAPS*\*Projects* location. Enter your project name and click **Open** to create the project. We enter the project name *blink\_led*.

#### Figure 14. Project blink\_led assignment

| I              |                    |        |

|----------------|--------------------|--------|

| File name:     | blink_led.upj      | Open   |

| Files of type: | CAPS Files (*.upj) | Cancel |

| Files of type: | CAPS Files (*.upj) | Cancel |

Click **Open** to open a new project filename.

The dialog displays the default or new *Project Folder* you selected [1] and the default or new *Project Name* [2], as shown in *Figure 15*.

| Create Project Project Folder: [C:\CAPS\Projects\blink_led Project Folder: [C:\CAPS\Projects\blink_led Project Name : [blink_led Description:     blink_led Description:     blink_led demo project         3  Target Devices : Datasheet: uPSD3434E-40U6          uPSD Family         uPSD 3000         uPSD 3000         uPSD 3400         uPSD 3400         uPSD 3422E         uPSD 3432E         uPSD 3432E         uPSD 3432E         uPSD 3432E         uPSD 3434E         uPSD 343EV         uPSD 3434E         uPSD | oject View Help<br>C 😅 🖬 🐇 🖻 💼 💡 😵 💋 🦯                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| uPSD Family         uPSD 3200         uPSD 3300         uPSD 3400         uPSD 3400         uPSD 3422E         uPSD 3422E         uPSD 3422E         uPSD 3432E         uPSD 3433E         uPSD 3433E         uPSD 3433E         uPSD 3434E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Project Folder : C:\CAPS\Projects\blink_led Project Name : blink_led Description : blink_led demo project 2                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Browse |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | uPSD Family     uPSD3200     uPSD3300     uPSD3400     uPSD3422E     uPSD3422E     uPSD3433E     uPSD3433E     uPSD3433E     uPSD3433E     uPSD3434E     uPSD3434E | <ul> <li>Fast 8-bit Turbo 8032 MCU operating up to 40 MHz</li> <li>Dual Flash Memories w/ Mem Management</li> <li>256 KB Main Flash Memory and 32 KB Secondary Flash Memory</li> <li>8 KB SRAM</li> <li>GPLD - 16 macrocells</li> <li>JTAG Debug and In-System Programming (ISP)</li> <li>Communication Interfaces <ul> <li>USB 2.0 Full Speed (12Mbps)</li> <li>12C Master /Slave bus controller</li> <li>SPI Master bus controller</li> <li>SPI Master bus controller</li> <li>2 UARTs</li> <li>IrDA protocol support</li> <li>8032 Address/Data bus</li> <li>A/D Converter: 8 Channels, 10-bit resolution</li> </ul> </li> </ul> |        |

| Figure | 15  | Project | specification |

|--------|-----|---------|---------------|

| riuure | 10. | FIDIECL | Specification |

You may also enter an optional project Description [3].

The next step is to select the target device, using the *Target Devices* window device folder tree. We select the  $\mu$ PSD3434E, 80-pin TQFP [4]. Notice that when you select the target device, the tabbed *Device Overview* window displays device-specific information. (Click on other devices to see the contents of this window change). Select the target device corresponding to your hardware.

This completes the steps used to open a CAPS project. Remember that the project is not saved until you reach the final step of the wizard mode of operation. Click the **Create in Wizard Mode...** button to continue, and configure the firmware to the target device.

### 2.4.2 Designing your project

The wizard mode of operation lets you configure your project by choosing from common configuration options.

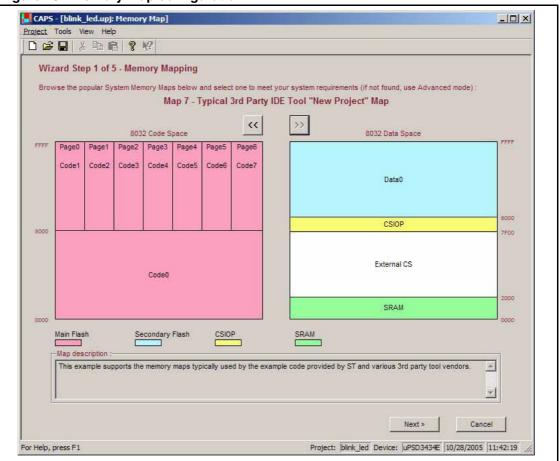

The first wizard design step, *Figure 16*, displays the memory map configuration dialog.

Note: If you selected an 80-pin device, there are five wizard design steps. If you selected a 52-pin device, there are four wizard design steps. The external chip selects step is omitted for 52-pin devices because of GPIO limitations.

#### Figure 16. Memory map configuration

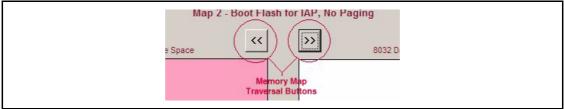

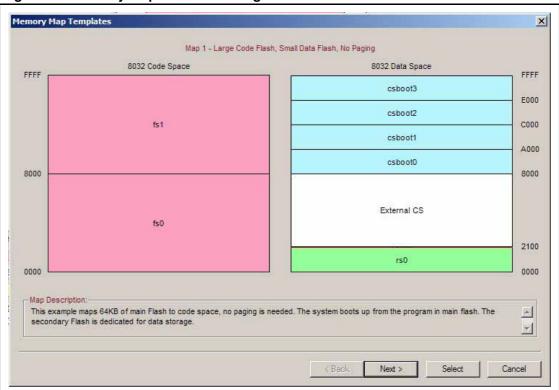

Use the double-arrow scroll buttons to traverse the available memory map options. Choose the memory map corresponding to your hardware and firmware.

Each memory map option window displays a description of the memory configuration and Code, Data and Paging attributes. The dialog also shows a graphic visualization of the memory layout. (The legend describes the color-coded memory segments and descriptive text is provided in the *Map description* window).

If there are no special memory requirements for code or data space and no chip select requirements, use the default memory configuration: *Large Code Flash, Small Data Flash, No Paging.* However, because this example uses Port D for the LED, we select Map 7 (*Typical 3rd Party IDE Tool "New Project" Map*) for the correct CSIOP settings.

Once you have selected the desired memory configuration for your target application using the memory map navigation buttons, click the **Next** > button at the bottom of the screen to go to the *Firmware Placement* design step.

Use the *Firmware Placement* dialog, shown in *Figure 17*, to associate a firmware *.hex* file with your project.

| Wizard Step 2 of 5 - Firmware Place   | ement                                          |

|---------------------------------------|------------------------------------------------|

| First : Specify 8032 MCU filename for | or CODE based on your selected Memory Map:     |

| Code0                                 | Browse                                         |

| Code1                                 | Browse                                         |

| Code2                                 | Browse                                         |

| Code3                                 | Browse                                         |

| Code4                                 | Browse                                         |

| Code5                                 | Browse                                         |

| Code6                                 | Browse                                         |

| Code7                                 | Browse,                                        |

|                                       |                                                |

| Second : Specify 8032 MCU filenar     | me for DATA based on your selected Memory Map: |

| Data0                                 | Browse                                         |

|                                       |                                                |

|                                       |                                                |

|                                       |                                                |

#### Figure 17. Firmware placement

Click the **Browse** ... button to use the file browser to select your firmware file, or enter a fully qualified path and filename. Because this example uses the RIDE *led\_blink* example, we select file *LED\_BLINK.HEX*, located at

C:\RIDE\EXAMPLES\8051\DERIVATIVES\ST\_UPSD\UPSD3400\LED\_BLINK. (Figure 18).

#### Figure 18. Firmware file browser

| Open<br>Look in: 🔁 | C LED_BLINK         | ▼ ← ₺ | <u>?×</u> |

|--------------------|---------------------|-------|-----------|

|                    |                     |       |           |

|                    |                     |       |           |

|                    |                     |       |           |

| File name:         | LED_BLINK.HEX       |       | Open      |

| Files of type:     | e: Hex Files (*hex) | •     | Cancel    |

Click **Open** to select the firmware file, which is then displayed in the *Code0* text box shown in *Figure 19*.

| t Tools View Help                               |                                          |

|-------------------------------------------------|------------------------------------------|

| <b>≱ 🖬   ∦ № №     ? №</b>                      |                                          |

| Vizard Step 2 of 5 - Firmware Placement         |                                          |

| First : Specify 8032 MCU filename for CODE base | d on your selected Memory Man            |

|                                                 |                                          |

| Code0 C:\RIDE\EXAMPLES\8051\DERIVATIVES\        | ST_UPSD\UPSD3400\LED_BLINK\LED_BLINK.HEX |

| Code1                                           | Browse.                                  |

| Code2                                           | Browse.                                  |

| Code3                                           | Browse.                                  |

| Code4                                           | Browse.                                  |

| Code5                                           | Browse.                                  |

| Code6                                           | Browse.                                  |

| Code7                                           | Browse.                                  |

| .41                                             |                                          |

| Second : Specify 8032 MCU filename for DATA     | based on your selected Memory Map:       |

| Data0                                           |                                          |

|                                                 | Browse.                                  |

| <u></u>                                         |                                          |

|                                                 |                                          |

|                                                 |                                          |

|                                                 | < Back Next > Can                        |

|                                                 |                                          |

Figure 19. Firmware file display

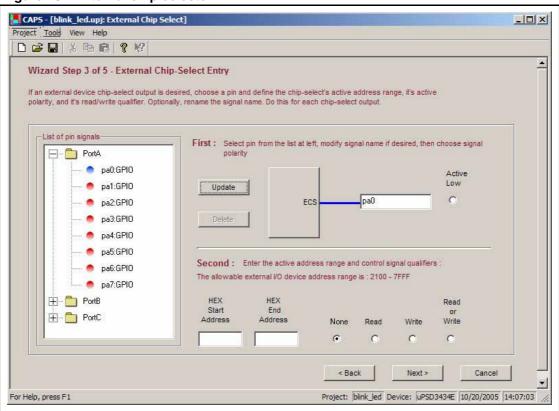

Click **Next>** to continue to the next step, which will be either the *External Chip-Select Entry*, *Figure 20*, or *Configuration Settings* dialog, *Figure 21*.

Note: This step, 3 of 5, is only applicable to 80-pin devices. If your project uses the 52-pin device, you will not see Figure 20 but will continue with the Configuration Settings step, shown in Figure 21.

23/75

#### Figure 20. External chip selects

Because our example does not need any special chip-selects declared, we continue to the next step without making any entries on this form.

Click Next> to continue to the Configuration Settings dialog, Figure 21.

57

| CAPS - [blink_led.upj: Co                                              | nfiguration]    |                                       |                                                                              |

|------------------------------------------------------------------------|-----------------|---------------------------------------|------------------------------------------------------------------------------|

| reject Tools View Help                                                 |                 |                                       |                                                                              |

| D 🚅 🖬   X 🖻 🛍                                                          | 8 N?            |                                       |                                                                              |

| Wizard Step 4 of 5 -<br>Optional configuration choi<br>Security        | ces.            | on Settings                           |                                                                              |

| -Sector Protection                                                     |                 |                                       |                                                                              |

| Main Flash :                                                           |                 | Secondary Flash                       |                                                                              |

| E Sector 0                                                             | Sector 4        | Sector 0                              |                                                                              |

|                                                                        | Sector 5        | E Sector 1                            |                                                                              |

| Sector 2                                                               |                 | Sector 2                              |                                                                              |

| E Sector 3                                                             | Sector 7        | Sector 3                              |                                                                              |

| Description                                                            |                 |                                       |                                                                              |

| Use this field to facilitate<br>this information.<br>Default: FFFFFFFF | your programmin | g contents and revision level identif | cation. The setting of the security options will not affect the reading of A |

|                                                                        |                 |                                       |                                                                              |

|                                                                        |                 |                                       |                                                                              |

|                                                                        |                 |                                       | < Back Next > Cancel                                                         |

|                                                                        |                 |                                       | Project: blink_led Device: uPSD3434E 10/20/2005 14:08:23                     |

Figure 21. Configuration settings

We accept the default settings for Security and Sector Protection.

Click Next > to continue to the JTAG ISP Operations dialog.

At this point, the CAPS software is able to "fit" the design to the silicon architecture. You may notice a small delay while CAPS "fits" the design. This creates a programming data file in your project directory, named *blink\_led.obj* in our example.

#### 2.4.3 Programming your target device

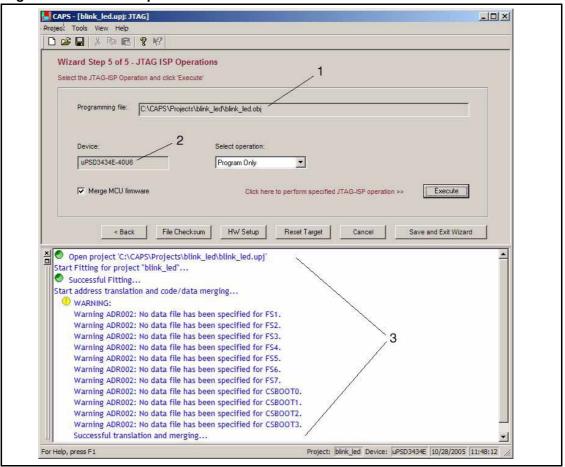

*Figure 22* shows the device programming dialog.

#### Figure 22. JTAG ISP operations

The name of the programming data file created in the previous step is displayed in the *Programming file* window [1] and the selected device is displayed in the *Device* window [2]. The *Output Log* displays the fitting results [3], provided logging is enabled using the *View* menu.

Before programming the device, it is necessary to specify the type of connection to the target device and to verify connectivity. Click **HW Setup** to begin the connectivity dialog (*Figure 23*). Because we use RLINK in this example, we accept the default *Hardware Selection* (*RLink*) setting and click the **RLink Connect Test** button to verify connectivity.

#### Figure 23. Hardware setting

| Hardware Setting           | X                   |

|----------------------------|---------------------|

| Hardware Selection : RLink | RLink Connect Test  |

|                            | Target Connect Test |

| Cancel                     | ОК                  |

Note: If you are using FlashLINK, use the drop-down menu to select the FlashLINK connection.

After a short delay during which a loopback test is performed, a successful test message is displayed, provided the loopback test passed (*Figure 24*). If the test failed, check the hardware power and cable connections.

#### Figure 24. RLINK connect test status

| RLink Connect Test Status  |

|----------------------------|

| RLink connect test passed. |

| OK                         |

Click **OK** to acknowledge the test results and continue.

In the same way, test connectivity to the target board by clicking the **Target Connect Test** button (*Figure 23*).

The *Target connect test passed* message (*Figure 25*) indicates there is no open circuit along the JTAG chain on the target board.

#### Figure 25. Target connect test status

| Target Connect Test Status  | × |

|-----------------------------|---|

| Target connect test passed. |   |

| ОК                          |   |

Click OK to acknowledge the test results message.

Click OK or Cancel to exit the Hardware Setting dialog window (Figure 23).

Use the *Select operation* drop-down menu, *Figure 22*, to choose the desired JTAG-ISP operation. In our example, we choose the *Program Only* option. As we shall see, a blank test will be done before programming the device.

Click **Execute** to begin the selected operation.

CAPS always verifies that the device is blank before attempting to program the device. If the device is not blank, CAPS prompts to erase the chip (*Figure 26*).

Click Yes to erase the chip and to continue with programming flash.

#### Figure 26. Device blank test

| JTAG-ISP Operations                                                |

|--------------------------------------------------------------------|

| The device is not blank.<br>Do you want to do the full chip erase? |

| Yes No                                                             |

The Output Log shows the programming progress (*Figure 27*). In this example, the log shows the progress of the erasing [1] and programming [2] steps. When device programming is complete, the log displays "Successful JTAG operation."

| CAPS - [blink_led.upj]                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ject <u>T</u> ools <u>V</u> iew <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                       |

| ) 🚅 🖬 👗 🖻 🛍 🤶 🌾 👘                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| Wizard Step 5 of 5 - JTAG ISP 0                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| Select the JTAG-ISP Operation and click '                                                                                                                                                                                                                                                                                                                                                              | Execute'                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| Programming file: C:\CAPS\Pro                                                                                                                                                                                                                                                                                                                                                                          | sjects\blink_led\blink_led.obj                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| Device:                                                                                                                                                                                                                                                                                                                                                                                                | Select operation:                                                                                                                                                                                                                                                                                                     |

| uPSD3434E-40U6                                                                                                                                                                                                                                                                                                                                                                                         | Program Only                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

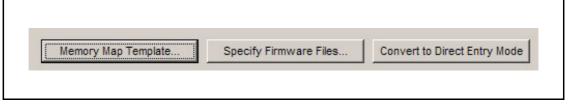

| 🔽 Merge MCU firmware                                                                                                                                                                                                                                                                                                                                                                                   | Click here to perform specified JTAG-ISP operation >>                                                                                                                                                                                                                                                                 |