## STBus communication system concepts and definitions

## Abstract

This document introduces the concepts and definitions referring to the STBus, the communication system (interconnect) developed for system-on-chip (SoC) applications and whose usage inside and outside ST is becoming wider and wider.

The basic terminology, the main concepts and the various available protocols are presented at a detailed but accessible level, to allow the reader to gain familiarity with the STBus and gain the background knowledge required to implement an STBus system.

## Objectives

The objective of this document is to provide all the information required to understand the STBus. It covers the communication protocols and the interfaces.

#### Audience

This document addresses its audience as the interconnect architects, the interconnect designers, the application engineers and the project leaders.

The document can be used as a complete and concise reference about the STBus communication system by anyone starting architectural or design activities about the STBus.

57

# Contents

| 1 | Introd | luction                    |                                                                | 4              |

|---|--------|----------------------------|----------------------------------------------------------------|----------------|

|   | 1.1    | STBus                      | overview                                                       | 4              |

|   |        | 1.1.1                      | Basic terminology                                              | . 4            |

|   |        | 1.1.2                      | Protocol                                                       | . 5            |

|   |        | 1.1.3                      | Interfaces                                                     | . 6            |

|   |        | 1.1.4                      | Components                                                     | . 6            |

| 2 | STBu   | s signa                    | ls                                                             | 8              |

|   | 2.1    | Control                    | signals                                                        | 8              |

|   |        | 2.1.1                      | Initiator to target                                            | . 8            |

|   |        | 2.1.2                      | Target to initiator                                            | . 9            |

|   | 2.2    | Transac                    | tion signals                                                   | 10             |

|   |        | 2.2.1                      | Initiator to target                                            | 10             |

|   |        | 2.2.2                      | Target to initiator                                            | 13             |

|   | 2.3    | Service                    | signals                                                        | 14             |

|   | 2.4    | Test sig                   | nals                                                           | 15             |

| 3 | STBu   | s proto                    | cols                                                           | 16             |

| • | 3.1    | •                          | protocol (peripheral)                                          |                |

|   | 0.1    | 3.1.1                      | Type 1 interface definition                                    |                |

|   |        | 3.1.2                      | Type 1 signal and timing                                       |                |

|   |        | 3.1.3                      | Address usage                                                  |                |

|   |        | 3.1.4                      | Byte enables usage                                             |                |

|   |        | 3.1.5                      | Opcode usage                                                   |                |

|   |        | 3.1.6                      | Response opcode usage                                          |                |

|   |        | 3.1.7                      | Basic transaction description                                  |                |

|   |        | 3.1.8                      | Examples                                                       |                |

|   |        | 3.1.9                      | Remarks on response request delay                              | 24             |

|   | 3.2    | 0.1.0                      |                                                                |                |

|   |        |                            | protocol (basic)                                               | 26             |

|   |        |                            | protocol (basic)                                               |                |

|   |        | Type 2                     |                                                                | 27             |

|   |        | Type 2  <br>3.2.1          | Type 2 interface definition                                    | 27<br>28       |

|   |        | Type 2  <br>3.2.1<br>3.2.2 | Type 2 interface definition         Type 2 signals and timings | 27<br>28<br>29 |

|                 | 3.2.6    | Byte enables usage                                             |

|-----------------|----------|----------------------------------------------------------------|

|                 | 3.2.7    | Opcode usage                                                   |

|                 | 3.2.8    | Response opcode usage                                          |

|                 | 3.2.9    | Basic transactions description                                 |

|                 | 3.2.10   | Chunk definition                                               |

|                 | 3.2.11   | Message definition                                             |

|                 | 3.2.12   | Examples                                                       |

| 3.3             | Туре З   | protocol (advanced) 48                                         |

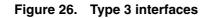

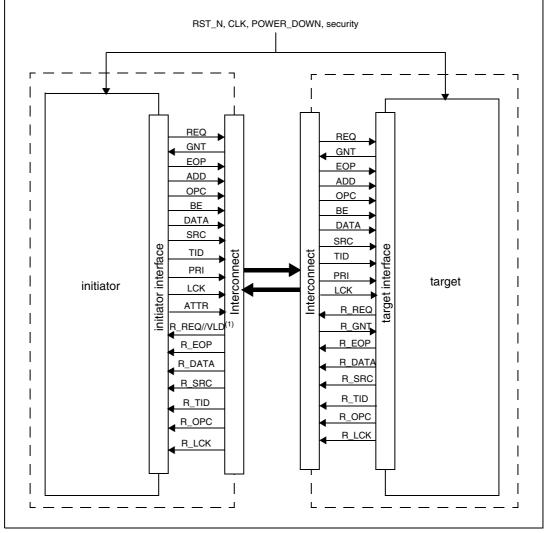

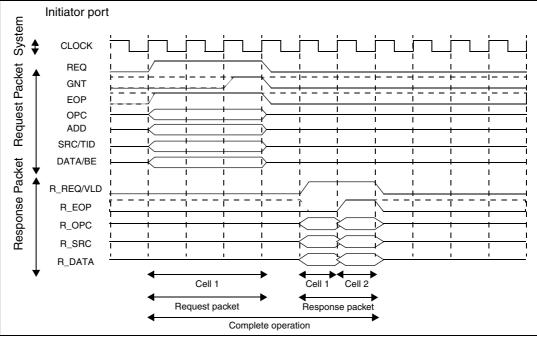

|                 | 3.3.1    | Type 3 interfaces definition                                   |

|                 | 3.3.2    | Type 3 signals and timings 50                                  |

|                 | 3.3.3    | Type 3 enhancements/changes compared to type 2                 |

|                 | 3.3.4    | Address usage                                                  |

|                 | 3.3.5    | Byte enables usage                                             |

|                 | 3.3.6    | Opcode usage                                                   |

|                 | 3.3.7    | Response opcode usage                                          |

|                 | 3.3.8    | Attribute signal usage53                                       |

|                 | 3.3.9    | Basic transaction description54                                |

|                 | 3.3.10   | Chunks and messages description54                              |

|                 | 3.3.11   | Examples                                                       |

| 3.4             | Error m  | anagement                                                      |

|                 | 3.4.1    | Error causes                                                   |

|                 | 3.4.2    | Error management                                               |

|                 | 3.4.3    | Error management in type 161                                   |

|                 | 3.4.4    | Error management in type 2 62                                  |

|                 | 3.4.5    | Error management in type 3 62                                  |

|                 | 3.4.6    | Behavior of the STBus building blocks with respect to errors63 |

|                 |          |                                                                |

| Appendix A G    | ilossary |                                                                |

| Revision histor | <b>y</b> |                                                                |

## 1 Introduction

The STBus is a set of protocols, interfaces, primitives and architectures specifying an interconnect subsystem, versatile in terms of performance, architecture and implementation.

The STBus is the result of the evolution of the interconnect subsystem developed for microcontrollers dedicated to consumer applications such as, set top boxes, ATM networks, digital still cameras and others. Such an interconnect was born from the accumulation of ideas converging from different sources, such as the transputer (ST20), the Chameleon program (ST40, ST50), MPEG video processing and VCI (virtual component interface) organization.

Today the STBus is not only a communication system characterized by protocol, interfaces, transaction set and IPs, but also a technology allowing design and implementation of communication networks for SoCs with the support of a development environment including tools for system level design and architectural exploration, silicon design, physical implementation and verification.

## 1.1 STBus overview

### 1.1.1 Basic terminology

This section introduces some basic concepts that define a common language to be used when referring to an STBus based system.

For IPs connected to the STBus, two kinds of blocks are defined:

| initiator                                 | Any block able to generate traffic toward the interconnect in order to access the system resources (memory, peripherals and so on).                                                                                                                                                      |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| target                                    | Any block being a resource for the system (memory, peripheral and so on), accessed by initiators.                                                                                                                                                                                        |  |  |

| In terms of data traffic                  | over the interconnect, the following definitions are given:                                                                                                                                                                                                                              |  |  |

| transaction                               | An exchange of information between a generic initiator and a generic target.                                                                                                                                                                                                             |  |  |

| cell                                      | The basic amount of information that can be transferred within a clock cycle; the amount of information transmitted depends on the data bus size.                                                                                                                                        |  |  |

| packet                                    | A collection of cells, building an uninterruptible transfer; the number<br>of cells building the packet depends on the operation size and the<br>data bus size.                                                                                                                          |  |  |

| It is possible to build a different ways: | a more complex data structure using STBus interface signals in                                                                                                                                                                                                                           |  |  |

| chunk                                     | A collection of packets linked together by the LOCK (LCK) signal (see <i>Section 2.1: Control signals on page 8</i> ). Such a data structure allows locking the target until the transfer is completed. During the transfer no other initiators can access the target (uninterruptible). |  |  |

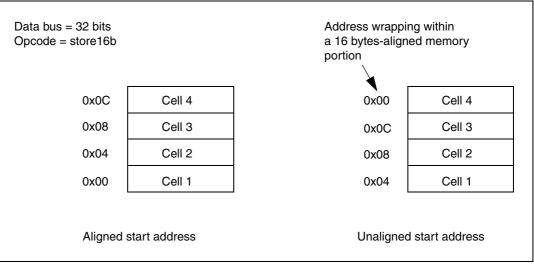

message A collection of chunks linked together by the TID[4] signal (see *Section 2.2: Transaction signals on page 10*). Such a data structure allows the transfer of a huge amount of data and exploits, when possible, proper routing schemes that optimize memory accesses and efficiency, particularly when accessing page based memories (such as DDR SDRAM).

#### 1.1.2 Protocol

Three different types of the STBus protocol exist, each having a different level of complexity in terms of both performance and implementation.

- **Type 1** is the simplest protocol and is intended to be used for peripherals registers access. No pipeline applies. It acts as an RG protocol. Load/store on 1, 2, 4, and 8 bytes are supported.

- **Type 2** adds pipeline features. It is equivalent to the "basic" RGV protocol. It supports all operation code for ordered transactions. The number of the requesting cells (that is, in a packet) is the same as the number of the response ones.

- **Type 3** is an advanced protocol implementing split transactions for high bandwidth requirements (high performance systems). It supports out of order executions. The packet response size might be different than the packet request size (the number of cells differs between request and response). The interfaces map the STBus transaction set on a physical set of wires defined by this interface.

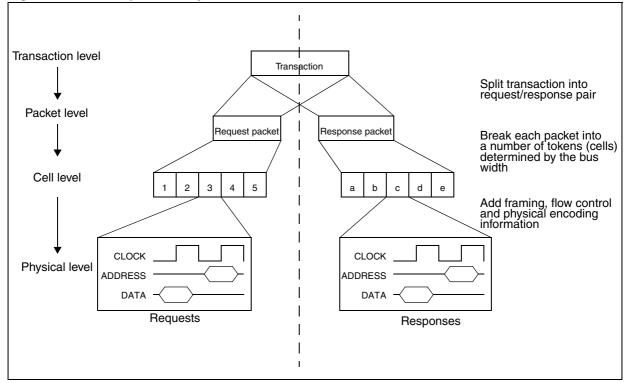

The STBus protocol can be seen as organized in layers, as shown in *Figure 1*.

#### Figure 1. STBus protocol layers

### 1.1.3 Interfaces

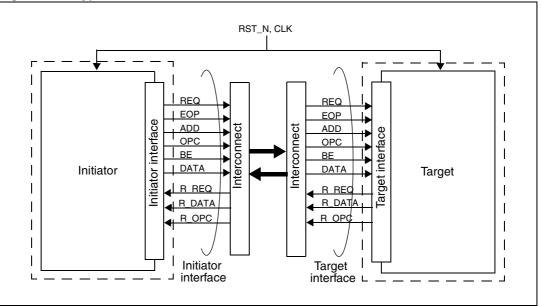

There are two different types of interfaces: one between the initiator and the interconnect, the other between the interconnect and the target.

The difference between the interfaces consists of some signals that are used by one interface and not by the other one, and by some signals that are present in both the interfaces but whose behavior changes depending on the interface itself (for example, refer to the GRANT signal in *Section 2.1: Control signals on page 8*).

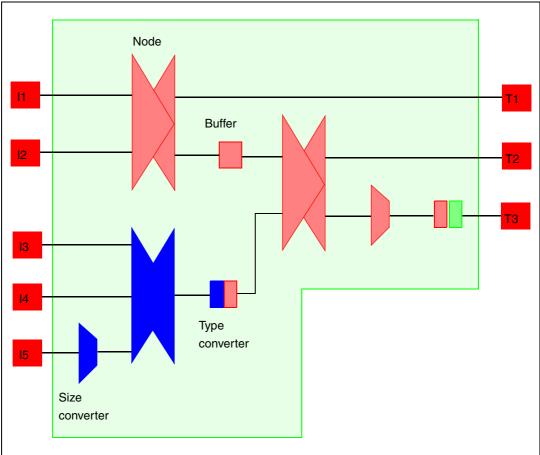

#### 1.1.4 Components

The components, or building blocks, of an STBus communication system are:

- node

- write posting handler

- register decoder

- generic converter

The node is responsible for the arbitration and the routing of the transactions. The arbitration is performed by one or more arbiters, the routing is performed by the datapath through a set of multiplexers and demultiplexers, driven by the signals generated by the arbiter(s).

The write posting handler is responsible for the management of posted store transactions.

The register decoder is basically a node specific for type 1 IPs. It arbitrates among type 1 initiators, and allows access to type 1 targets, usually peripherals and registers banks.

The generic converter can behave as one or more of the following blocks:

| buffer              | Used as retiming stage and is typically used to break critical paths, especially between blocks placed far from each other in the system floorplan.                                                                               |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| size converter      | Used to connect two blocks with different bus sizes to each other.                                                                                                                                                                |

| type converter      | Used to connect two blocks following different STBus protocols to each other.                                                                                                                                                     |

| frequency converter | Used to connect two blocks working at different frequencies to each<br>other, when the two clocks are completely uncorrelated<br>(asynchronous mode) or when a phase relationship between them<br>exists (semi-synchronous mode). |

|                     |                                                                                                                                                                                                                                   |

The generic converter can simultaneously perform a set of the operations (that is, size, type and frequency conversion) when behaving as in the blocks listed above.

*Figure 2* shows an example of STBus interconnect where nodes, buffers, size and type converters are used. In *Figure 2* red blocks are type 3 blocks, blue blocks are type 2 blocks and green blocks are type 1 blocks.

Figure 2. Example of STBus interconnect system

# 2 STBus signals

This chapter contains a list of all signals and are defined in the context of the STBus protocols. Depending on the specific STBus protocol, not all the signals are required.

According to the protocol type, some signals are supported and some are not. In the tables in the following sections, supported signals are marked with 'S', unsupported signals are marked with 'U'. Among the supported signals, the mandatory and optional signals are highlighted in the sections dealing in detail with the three different protocols.

The STBus signals present at any STBus module interface can be grouped into three sets:

- control signals

- transaction signals

- service signals

## 2.1 Control signals

The control signals determine when a transaction starts, when it finishes, and if two or more consecutive transactions are linked together to build more complex transactions.

#### 2.1.1 Initiator to target

#### Table 1. STBus control signals: initiator to target

| Table 1. STBUS control signals: Initiator to target |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

|-----------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Signal                                              | name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Protocols                        |

| REQ<br>(request)                                    |      | The request is the signal used by the initiator interface to communicate that it wants to start a transaction. Once the request is asserted, all the signals associated with the packet to be transmitted must be kept constant until the grant signal (GNT) is received from the target interface, meaning the transaction has effectively started.<br>The cell is actually transferred in correspondence to the clock rising edge, where both REQ and GNT are high.                               | Type 1 S<br>Type 2 S<br>Type 3 S |

| GNT<br>(grant)                                      |      | The grant is the signal with which a transaction is considered started after a request has been asserted.<br>The GNT generated by a node as consequence of the arbitration is a "causal" grant (grant on request), while the grant generated by a target module is a "default" grant and is itself an information signal about the availability of the target to accept a new request. The cell is actually transferred in correspondence to the clock rising edge where both REQ and GNT are high. | Type 1 U<br>Type 2 S<br>Type 3 S |

| EOP<br>(end of pack                                 | (et) | The end of packet is the signal marking the last cell of a currently transmitted packet. It is mainly used by the node to ensure a packet cannot be interrupted.                                                                                                                                                                                                                                                                                                                                    | Type 1 S<br>Type 2 S<br>Type 3 S |

| LCK<br>(lock)                                       |      | The lock signal is used to link together two or more packets to build complex transactions, such as chunks and READMODIFYWRITE operations (see <i>Reserved operations on page 33</i> ).                                                                                                                                                                                                                                                                                                             | Type 1 U<br>Type 2 S<br>Type 3 S |

# 2.1.2 Target to initiator

### Table 2. STBus control signals: target to initiator

| Signal name                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Protocols                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| R_REQ<br>(response request)      | The response request is the signal used by the target<br>interface to communicate that it wants to complete a<br>transaction. Once the R_REQ is asserted, all the signals<br>associated with the response packet to be transmitted must<br>be kept constant until R_GNT is received from the initiator<br>interface, meaning the transaction has completed.                                                                                                                                                                                                                  | Type 1 S<br>Type 2 S<br>Type 3 S |

| R_GNT<br>(response grant)        | The response grant is the signal with which a transaction is considered complete after an R_REQ has been asserted.<br>R_GNT generated by a node as a consequence of the response arbitration is a "causal" response grant. The R_GNT generated by a legacy module such as a converter is a "default" response grant which informs of the availability of the legacy module to accept a new response.<br>Pure initiators don't have the R_GNT signal, since they are supposed to initiate traffic generation provided that they are able to handle all the related responses. | Type 1 U<br>Type 2 S<br>Type 3 S |

| R_EOP<br>(response end of packet | The response end of packet is the signal that marks the last<br>cell of the currently transmitted response packet. It is mainly<br>used by the node to ensure a response packet cannot be<br>interrupted.                                                                                                                                                                                                                                                                                                                                                                    | Type 1 U<br>Type 2 S<br>Type 3 S |

| R_LCK<br>(response lock)         | The response lock signal is used to link together two or more response packets during the transmission of complex transactions, such as responses to chunks.                                                                                                                                                                                                                                                                                                                                                                                                                 | Type 1 U<br>Type 2 S<br>Type 3 S |

# 2.2 Transaction signals

## 2.2.1 Initiator to target

### Table 3. STBus transaction signals: initiator to target

| Signal name                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Protocols                        |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ADD[31:n]<br>(address with $n = 0, 1, 2, 3, 4, 5$ depending on<br>the data bus size)               | This is the address of the memory location which the initiator<br>wants to access. The address of a transaction must be<br>transaction-aligned.<br>For example, an 8-byte operation can be addressed to 0x0,<br>0x8 and 0x10, but not to addresses 0x4 and 0xC.                                                                                                                                                                                                                                                              | Type 1 S<br>Type 2 S<br>Type 3 S |

| DATA[ $8^2^n$ -1:0]<br>(data with n = 0, 1, 2, 3,<br>4, 5 depending on the<br>data bus size)       | This is the data the initiator wants to send to the target in case of store operations.                                                                                                                                                                                                                                                                                                                                                                                                                                      | Type 1 S<br>Type 2 S<br>Type 3 S |

| BE[ $2^{n}$ -1:0]<br>(byte enables with n = 0, 1, 2, 3, 4, 5<br>depending on the data<br>bus size) | The byte enables signal defines which bytes within a cell are<br>significant. For operations whose size is smaller than the<br>data width, BE specifies the low order address bits.<br>For example, with an LD1 in a 32-bit system, address bits<br>[1:0] are implicitly encoded in the BE signal.<br>In systems where BE signals are not defined, all cells are<br>assumed to be valid.                                                                                                                                     | Type 1 S<br>Type 2 S<br>Type 3 S |

| OPC[7:0]<br>(opcode)                                                                               | This signal defines the type of operation the initiator wants to<br>perform. OPC is composed of three parts.<br>Bits [3:0] indicate the operation type, for example,<br>load/store/cache operation.<br>Bits [6:4] specify the size of the operation, for example, the<br>number of bytes the operation involves.<br>Bit 7 is reserved and in multiplexed buses/systems is used to<br>distinguish between request and response packets. The<br>STBus interconnect is a non-multiplexed system so bit 7<br>must always be low. | Type 1 S<br>Type 2 S<br>Type 3 S |

| SRC[9:0]<br>(source identifier)                                                                    | SRC is used for two reasons: the lowest bits can be used by<br>the initiator to identify possible internal sub processes, the<br>highest bits are used by the interconnect to unambiguously<br>identify the initiator itself.                                                                                                                                                                                                                                                                                                | Type 1 U<br>Type 2 S<br>Type 3 S |

| Signal name                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Protocols                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| TID[7:0]<br>(transaction identifier) | <ul> <li>The TID signal is used by the initiator to label a transaction with additional information.</li> <li>It is split into two fields: TID[3:0] uniqueness information, TID[7:4] enhancement information.</li> <li>The uniqueness information is used by type 3 initiators to unambiguously identify the transaction. This allows the correct response to be detected in the case of out of order traffic. Type 2 initiators don't have this capability.</li> <li>The enhancement information is used to enhance the processing of an operation without changing its functionality. The following fields are defined:</li> <li>TID[4] : not end of message</li> <li>'0' = this transaction has no relationship to the next transaction (end of message)</li> <li>'1' = the next transaction is related to this transaction (member of a message)</li> <li>TID[5] : not device access</li> <li>'0' = this store operation will not be posted</li> <li>'1' = this store operation may be posted (that is, the system may choose to return an early response, deleting the true response when it is returned to improve performance reducing the latency between grant and response)</li> <li>TID[6] : store and forward</li> <li>'0' = each time a cell is received/assembled, it can be immediately propagated to the target interface</li> <li>TID[7] : reserved</li> <li>The message information is used by the initiator to indicate that the system should attend to keep message components together. This can increase performance with access to a page-based memory such as the SDRAM.</li> <li>The write posting information is used by the initiator to indicate that the information is used by the initiator to indicate that the information in response to a write operation will be ignored so that a 'dummy' response can then be returned early.</li> <li>The store and forward information is used to drive the storage behavior to the buffers.</li> </ul> | Type 1 U<br>Type 2 S<br>Type 3 S |

| Table 3. | STRue transaction signals: initiator to target (continued) |

|----------|------------------------------------------------------------|

| Table 3. | STBus transaction signals: initiator to target (continued) |

| Signal name                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Protocols                        |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| PRI[3:0]<br>(priority)                | The PRI signal labels the request packet with an urgency<br>level which the interconnect may use to implement<br>preferential arbitration.<br>The priority is encoded into a 4-bit field (1111 = highest<br>priority, 0000 = lowest priority).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Type 1 U<br>Type 2 S<br>Type 3 S |

| ATTR[15:0]<br>(transaction attribute) | The ATTR signal is used by the initiator to label a transaction<br>with an additional attribute field, according to the following<br>description.<br>ATTR[3:0] : protection information (PROT)<br>ATTR[7:4] : cacheability (CACHE)<br>ATTR[9:8] : addressing policy type (PTYPE)<br>ATTR[15:10] : reserved for user-defined applications<br>The following fields are defined:<br>- PROT[0] : privilege level (0 = normal, 1 = privileged)<br>- PROT[1] : security (0 = secure, 1 = non secure)<br>- PROT[2] : data or instruction (0 = data, 1 = instruction)<br>- PROT[3] : exclusive lock (0 = disabled, 1 = enabled)<br>- CACHE[0] : bufferability (0 = non bufferable, 1 = bufferable)<br>- CACHE[1] : cacheability (0 = non cacheable, 1 =<br>cacheable)<br>- CACHE[2] : read allocate (0 = not write allocate, 1 = read<br>allocate)<br>- CACHE[3] : write allocate (0 = not write allocate, 1 = write<br>allocate)<br>- PTYPE[1:0] : addressing policy (00 = fixed, 01 =<br>incremental, 10 = wrapped, 11 = reserved)<br>The explicit addressing POLICY TYPE (PTYPE) signal has<br>been introduced to allow STBus type 3 initiators to generate<br>asymmetric load/store commands to AMBA AHB/APB<br>targets. | Type 1 U<br>Type 2 U<br>Type 3 S |

Table 3.

STBus transaction signals: initiator to target (continued)

# 2.2.2 Target to initiator

| Table 4. | STBus transaction signals: target to initiator |

|----------|------------------------------------------------|

|----------|------------------------------------------------|

| Signal name                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Protocols                        |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| R_DATA[ $8^2^n$ -1:0]<br>(response data with<br>n = 0, 1, 2, 3, 4, 5<br>depending on the data<br>bus size) | R_DATA is the data read from memory at a specified location during a load operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Type 1 S<br>Type 2 S<br>Type 3 S |

| R_OPC[7:0]<br>(response opcode)                                                                            | The R_OPC signal is used by the target to label a response<br>to an operation according to the following description:<br>$R_OPC[0]$ : operation status (0 = success, 1 = failure)<br>$R_OPC[1]$ : specifies whether the error has been originated<br>by a target external to the interconnect (when 0) or, by the<br>interconnect itself (when 1) as a consequence, for example,<br>of wrong address or security violation. When $R_OPC[0] = 0$ ,<br>$R_OPC[1]$ is meaningless.<br>$R_OPC[2]$ : reserved<br>$R_OPC[3]$ : operation type (0 = write, 1 = read)<br>$R_OPC[6:4]$ : operation type (copy of OPC[6:4])<br>$R_OPC[7]$ : fixed to 1 <sup>(1)</sup> .<br>Type 1 modules implement only bit 0 of this field. | Type 1 S<br>Type 2 S<br>Type 3 S |

| R_SRC[9:0]<br>(response source)                                                                            | The R_SRC signal is a copy of the SRC signal associated to<br>the respective request packet and is used by the interconnect<br>to identify the initiator to which the response has to be<br>routed.<br>For an initiator, the lowest bits can be used to detect the<br>internal subprocess to which the response is related.                                                                                                                                                                                                                                                                                                                                                                                         | Type 1 U<br>Type 2 S<br>Type 3 S |

| R_TID[7:0]<br>(response transaction<br>identifier)                                                         | The R_TID signal is a copy of the TID signal sent during the transmission of the request packet, and is used by type 3 initiators to detect the request packet to which the response is related.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Type 1 U<br>Type 2 S<br>Type 3 S |

1. R\_OPC[7] is reserved for systems which implement multiplexed request/response transports.

# 2.3 Service signals

| Table 5. | STBus service signals |

|----------|-----------------------|

|----------|-----------------------|

| Signal name                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                   | Protocols                        |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| CLK<br>(module clock)                              | All modules require a clock for the STBus interface.<br>All STBus signals are synchronous and significant on the<br>clock rising edge.                                                                                                                                                                                                                                                                                        | Type 1 S<br>Type 2 S<br>Type 3 S |

| RST_N<br>(module reset)                            | All STBus modules must be reset, and during reset all STBus<br>request signals have to be inactive. How the module is reset<br>depends on the reset methodology used in the specific<br>design flow. However, unless otherwise indicated, the reset<br>should be assumed to be asynchronous and active low.                                                                                                                   | Type 1 S<br>Type 2 S<br>Type 3 S |

| SECURITY[n-1:0]<br>(target security mode)          | This signal is generated by the system security controller (if<br>one is used).<br>At most, n equals the number of type 3 targets accessible<br>through the interconnect system. The signal states whether<br>the target is secure or non-secure, there by affecting the way<br>in which requests are routed to it through STBus nodes.<br>For a given target, 0 = target secure, 1 = target unsecure.                        | Type 1 U<br>Type 2 U<br>Type 3 S |

| POWER_DOWN[n-1:0]<br>(target power down<br>status) | This signal is generated by the system power management<br>controller (if one is used).<br>At most, n equals the number of type 3 targets accessible<br>through the interconnect system. The signal states whether<br>the target is on or in power-down mode, there by affecting the<br>routing of requests to it through STBus nodes.<br>For a given target,: 0 = target in power up mode, 1 = target in<br>power down mode. | Type 1 U<br>Type 2 U<br>Type 3 S |

# 2.4 Test signals

The STBus interconnect is fully scannable for testability reasons. However the test signals do not appear explicitly at STBus components or interconnect system interfaces, since application of test methodology is left to the system integration process and is neither performed at block level nor at interconnect level.

The test signals to be added to STBus interface are the standard ones, as shown in Table 6.

Table 6.STBus test signals

| Signal name                          | Description                                                                                                                                  | Protocols                        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| TST_SCANENABLE<br>(scan test enable) | The STBus interconnect can be fully scanned for testability.<br>The TST_SCANENABLE signal is used to enable the scan<br>test operation mode. | Type 1 S<br>Type 2 S<br>Type 3 S |

| TST_SCANIN<br>(scan test input)      | This is the scan chain(s) input used during the scan test operation mode.                                                                    | Type 1 S<br>Type 2 S<br>Type 3 S |

| TST_SCANOUT<br>(scan test output)    | This is the scan chain(s) output to be monitored during the scan test operation mode.                                                        | Type 1 S<br>Type 2 S<br>Type 3 S |

## **3 STBus protocols**

The STBus interface family contains a number of interface variants with differing performances and complexity costs. In selecting which type of STBus interface to use in a specific design, the designer should consider the module and system costs, and select the simplest interface with the appropriate features and data width for that system.

To ensure easy availability of third party support and IPs, the STBus interfaces and protocols are closely related to the industry standards being developed by the open virtual standard interface alliance (VSIA).

A general concept related to memory addressing is the concept of endianess. The endianess affects the way in which data is organized in memory. The data field is made up of a set of byte quantities, each byte being associated uniquely with a specific byte enable bit. Each byte is organized as a little endian bit quantity. The data field may contain multiple bytes, these are organized in a byte significant manner. This means modules accessed by operations which are equal to the interface width of that module do not depend on endianness. However, the addressing of sub-word quantities is dependent on the endianess of the module associated with that interface.

*Table 7* shows an example of how sub-word quantities are interpreted by differing systems for a 4-byte system.

|                           | byte        |      |     | little e | ndian |     |     | big e |     |     |

|---------------------------|-------------|------|-----|----------|-------|-----|-----|-------|-----|-----|

| data                      | lane        | lane | 3   | 2        | 1     | 0   | 3   | 2     | 1   | 0   |

| 4 byte, add               | dress + 0   |      | MSB | +2       | +1    | LSB | MSB | +1    | +2  | LSB |

| 2 byte add                | lress + 0   |      |     |          | MSB   | LSB | MSB | LSB   |     |     |

| 2 byte add                | lress + 2   |      | MSB | LSB      |       |     |     |       | MSB | LSB |

| 1 byte <sup>(1)</sup> , a | address + 0 |      |     |          |       | LSB | MSB |       |     |     |

| 1 byte, add               | dress + 1   |      |     |          | LSB   |     |     | MSB   |     |     |

| 1 byte, add               | dress + 2   |      |     | LSB      |       |     |     |       | MSB |     |

| 1 byte, add               | dress + 3   |      | LSB |          |       |     |     |       |     | MSB |

Table 7.Endianess mechanism

1. For a single byte quantity the MSB and LSB are equivalent.

The main difference between the two addressing modes is the way in which the bytes of a word are interpreted within the memory locations: in little endian, a data word is accessed starting from the least significant byte (LSB) and proceeding toward the most significant byte (MSB). While in big endian the access starts from the most significant byte and proceeds toward the least significant byte. This means that, for a write operation to a memory location, the bytes building a data word are swapped within the data word.

For example, if an IP wants to write the four bytes B1, B2, B3 and B4 starting from address 0x0 (that is, B1 at 0x0, B2 at 0x1, B3 at 0x2 and B4 at 0x3) it has to build the following 4-byte word in little endian:

B4B3B2B1

and the following one in big endian: B1B2B3B4.

Doc ID 14178 Rev 2

The following sections introduce the three different STBus protocols: type 1 (peripheral), type 2 (basic) and type 3 (advanced).

## 3.1 Type 1 protocol (peripheral)

The type 1, or peripheral, STBus interface is the simplest of the STBus family. It is targeted at modules which require a simple, low complexity, medium data rate communication path with the rest of the system.

This typically includes standalone modules such as general purpose input/outputs (GPIOs) and UARTS, or modules which require independent control interfaces in addition to their main memory interface, or internal interfaces which do not require pipelines.

The supported operation subset is targeted at simple memory devices and supports read and write operations of up to 8 bytes. The interface is organized to minimize the need for the target device to interpret the operation, allowing the correct operation to be achieved by handling larger data quantities as if they were a series of smaller accesses.

#### 3.1.1 Type 1 interface definition

#### Figure 3. Type 1 interfaces

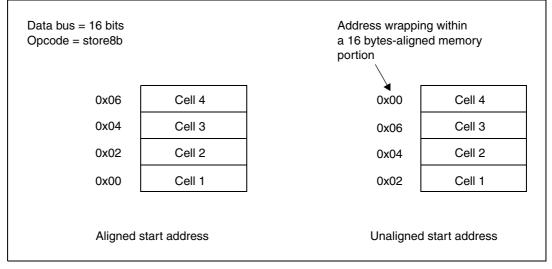

The type 1 interface is a simple handshake interface which supports a limited set of operations. These operations are mapped onto a packet containing one or more cells at the interface.

Each request cell contains information on the operation type (OPC), the position of the last cell in the operation (EOP), the address of the operation (ADD) and the associated data (DATA) in case of write to memory. This cell is passed to the target, which indicates it has accepted the cell by asserting a handshake (R\_REQ) and passes back a response. This response is also a packet containing a number of cells, each cell containing data (R\_DATA) and optionally error information (R\_OPC).

All type 1 devices are required to instantiate all mandatory signals, however simple devices may choose to only use a subset of these signals, leaving unused signals existing at the interface. These unused signals may not be connected if the functionality associated with the signal is not required.

As most modules are expected to be reused in large SOC systems with complex software, it is recommended that modules should implement a very basic error model which allows information on an incorrect operation to be passed back to debug software and helps build robust systems. The R\_OPC field is an optional signal which may be used to achieve this. It is typically used to indicate that a specific operation is not supported or, that accesses to some address locations within this device are not allowed. The system (as a whole) is able to use this information to indicate a potential problem. Devices which do not implement an error module are always assumed to do the operations correctly.

#### 3.1.2 Type 1 signal and timing

The signals given within *Table 8* are defined for type 1 initiators and targets. Signals which are mandatory for an interface are marked with 'M', signals which are optional and should only be implemented if required are marked with 'O'.

| Signal group          | Full name                    | Cignal nome                          | Direction    | Initiator            |      | Target              |      |

|-----------------------|------------------------------|--------------------------------------|--------------|----------------------|------|---------------------|------|

| Signal group          | Fuil name                    | Signal name                          | Direction    | Timing               | Туре | Timing              | Туре |

| Request flow          | Request                      | REQ                                  | init to targ | early <sup>(1)</sup> | М    | late <sup>(2)</sup> | М    |

| control and framing   | End of packet <sup>(3)</sup> | EOP                                  | init to targ | early                | 0    | late                | 0    |

|                       | Opcode                       | OPC[2:0]                             | init to targ | early                | М    | late                | М    |

|                       |                              | OPC[3] <sup>(4)</sup>                | init to targ | early                | 0    | late                | М    |

| Request contents      | Address                      | ADD[31:size <sup>(5)</sup> ]         | init to targ | early                | М    | late                | М    |

|                       | Byte enable <sup>(6)</sup>   | BE[(2 <sup>size</sup> -1):0]         | init to targ | early                | 0    | late                | М    |

|                       | Data <sup>(7)</sup>          | DATA[(8 * 2 <sup>size</sup> -1):0]   | init to targ | early                | 0    | late                | 0    |

| Response flow control | Response request             | R_REQ                                | targ to init | late                 | М    | early               | М    |

| Desarra               | Response opcode              | R_OPC                                | targ to init | late                 | 0    | early               | М    |

| Response content      | Response data <sup>(8)</sup> | R_DATA[(8 * 2 <sup>size</sup> -1):0] | targ to init | late                 | 0    | early               | 0    |

1. Early is defined as being in the first 20% of the clock cycle.

2. Late is defined as being in the first 80% of the clock cycle.

3. Initiator may not use it if generating single-cell packets only, target may not implement it only if its data size is 8 bytes.

4. Initiator may not use it since it has no defined meaning, target must implement if for reusability reasons.

5. Size defines the width of the interface, it may take a value between 0 and 3 and corresponds to interface widths of 1, 2, 4 or 8 bytes (8, 16, 32 or 64 bits).

6. Initiator may not use it if accessing entire words only.

7. Not used if initiator/target is read-only.

8. Not used if initiator/target is write-only.

Note: The STBus interconnect top level and building blocks always have all the signals at each interface, only external initiator and target IPs can use the optional signals.

Doc ID 14178 Rev 2

### 3.1.3 Address usage

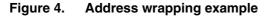

As far as the address of a packet is concerned, the following rule applies: the packet address must be opcode aligned, that is, it has to be a multiple of the number of bytes to be transferred within the packet. This means that:

- for 1-byte operations valid addresses are 0x0, 0x1, 0x2, 0x3 and so on

- for 2-byte operations valid addresses are 0x0, 0x2, 0x4, 0x6 and so on

- for 4-byte operations valid addresses are 0x0, 0x4, 0x8, 0xC and so on

- for 8-byte operations valid addresses are 0x0, 0x8, 0x10, 0x18 and so on

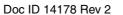

If the start address of a packet is not transaction aligned, then a wrapping of the address has to be implemented, in order to keep the cells of the packet within the allowed memory portion aligned to the transaction. *Figure 4* shows the concept of address wrapping through an example.

Note: In type 1 and type 2 systems, the address wrapping for misaligned start addresses has to be performed by the initiators. In type 3 systems, the address wrapping can be performed by the targets as for store operations the address can be constant within a packet and for loads only one cell is generated.

### 3.1.4 Byte enables usage

Byte enables is a signal (BE), whose size is equal to the number of bytes the data bus is composed of and may be defined in two ways:

- when the size of the operation (in bytes) is smaller than the data bus size (in bytes) the BE signal represents the lowest part of the address and must obey the addressing rule "the packet address must be opcode aligned"

- when the size of the operation is bigger than the data bus size, BE is simply a mask specifying which bytes of the overall word are affected by the operation

To clarify the second definition: consider a store of a 2-byte operation (STORE2B) in a 32-bit (4 bytes) context. The address is a 30-bit signal (ADD[31:2]) and BE is a 4-bit signal (BE[3:0]).

To write 2 bytes starting from the address 0, use:

ADD = 0x0000 0000

BE = 0011

Only bytes 0 and 1 are written. To write 2 bytes starting from the address 2, use:

$ADD = 0x0000\ 0000$ BE = 0xC (0b1100)

Only bytes 2 and 3 are written.

Since the STORE2B operation must obey the rule regarding transaction alignment, valid addresses for a 2-byte operation are addresses that are 2-byte aligned (0x0, 0x2, 0x4, 0x6, 0x8 and so on). Addresses that are 1-byte aligned (0x1, 0x3, 0x5, 0x7 and so on) are not legal for this operation.

This implies that the BE signal cannot be "1001" or "0110" for this operation. The same applies for other bus and opcode sizes.

### 3.1.5 Opcode usage

The encoding used on the peripheral interface is given in Table 9.

| Operation         | bit[3] | bit[2:1] | bit[0] |  |  |  |

|-------------------|--------|----------|--------|--|--|--|

| load byte         | 0      | 00       | 1      |  |  |  |

| load two bytes    | 0      | 01       | 1      |  |  |  |

| load four bytes   | 0      | 10       | 1      |  |  |  |

| load eight bytes  | 0      | 11       | 1      |  |  |  |

| store byte        | 0      | 00       | 0      |  |  |  |

| store two bytes   | 0      | 01       | 0      |  |  |  |

| store four bytes  | 0      | 10       | 0      |  |  |  |

| store eight bytes | 0      | 11       | 0      |  |  |  |

| reserved          | 1      |          | 1      |  |  |  |

The encoding is not generally interpreted by the interconnect or transport medium. This information remains constant across all the cells associated with this operation. Large (greater than 8 bytes) and compound operations are not supported on the peripheral interface.

If an unsupported operation is presented to a target then, if possible, the target device should indicate an error to the system. Irrespective of error support the target must always return a response.

#### 3.1.6 Response opcode usage

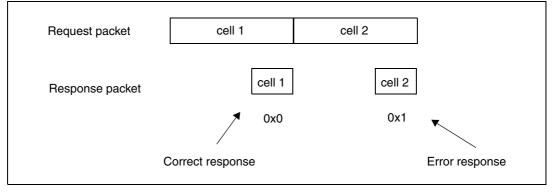

The response opcode (R\_OPC) field is used by the target to give information about the status of the operation. When the operation is successfully completed, the R\_OPC signal has the value 0. When the operation fails, either because of a wrong address or an unsupported opcode, the R\_OPC signal has the value 1. Some type 1 targets may assert the R\_OPC when there is a write attempt is performed on read-only registers.

# 3.1.7 Basic transaction description

## LOAD m bytes

| Abbreviation          | LD1, LD2, LD4, LD8                                                                                                                                                                                                                                                                                                  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Definition            | Read a single aligned word of m bytes from the target to the initiator. Valid sizes for m are defined to be $2^n$ where n is an integer in the range 0 to 3.                                                                                                                                                        |

| Qualifiers            | ADD[31:n]: the address of the word to be accessed.                                                                                                                                                                                                                                                                  |

|                       | BE[n-1:0]: the byte enable indicates which bytes within the word are significant.                                                                                                                                                                                                                                   |

|                       | R_DATA [8 x $2^{n}$ -1:0]: data to be transferred, the significance of bytes within this field is inferred from the byte enable information.                                                                                                                                                                        |

|                       | R_OPC: result of operation.                                                                                                                                                                                                                                                                                         |

| Comments              | Load implements a read operation between the initiator and the target.                                                                                                                                                                                                                                              |

| STORE m bytes         |                                                                                                                                                                                                                                                                                                                     |

| Abbreviation          | ST1, ST2, ST4, ST8                                                                                                                                                                                                                                                                                                  |

| Definition            | Write a single aligned word of m bytes from the initiator to the target, overwriting the location at that address with the data transferred. Valid sizes for m are defined to be $2^n$ where n is an integer in the range 0 to 3.                                                                                   |

| Qualifiers            | ADD[31:n]: the address of the word to be accessed.                                                                                                                                                                                                                                                                  |

|                       | BE[n-1: 0]: the byte enable indicates which bytes within the word are significant.                                                                                                                                                                                                                                  |

|                       | DATA[8 x 2 <sup>n</sup> -1:0]: data to be transferred.                                                                                                                                                                                                                                                              |

| Comments              | Store implements a write operation between an initiator and a target.                                                                                                                                                                                                                                               |

| Unsupported operation | ation                                                                                                                                                                                                                                                                                                               |

| Definition            | Return a response on reception of the operation.                                                                                                                                                                                                                                                                    |

| Comments              | The target device should always return an error if possible if<br>presented with an operation which is reserved. This allows the<br>operation set to be extended for future systems without making<br>existing IPs redundant. The response will always contain one<br>response cell for each request cell received. |

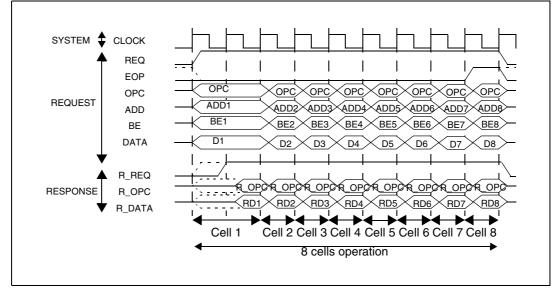

### 3.1.8 Examples

### 3.1.9 Remarks on response request delay

The following four example behavior types are theoretically possible for a multi-cell type 1 transaction consisting of the transmission of a packet composed of four cells.

#### Example 1

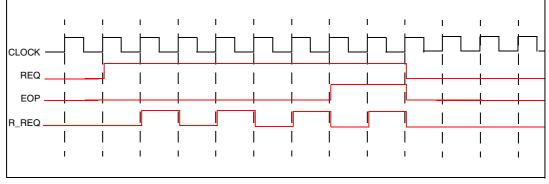

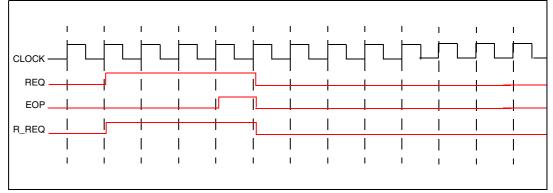

All R\_REQ coming with one (or more) cycles of delay with respect to the REQ for each cell of the packet.

#### Example 2

First R\_REQ coming with respect to one cycle of delay with respect to the REQ, the others coming in the same cycle as the REQ.

### Figure 10. Initial response delay

### Example 3

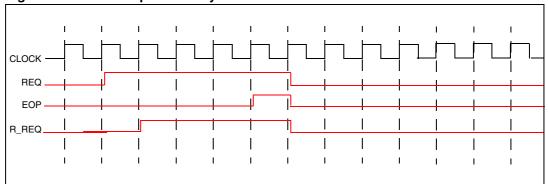

R\_REQ coming in the same cycle as the REQ for all the cells of the packet.

#### Example 4

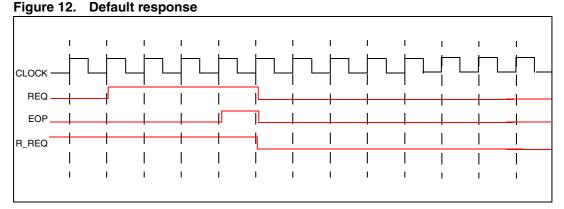

R\_REQ coming before the REQ (default grant behavior, see Section 3.2.4 on page 30).

Currently, the T3/T1 and T2/T1 converters and the register decoder work in the example behavior type shown in *Example 1*, but have not been verified with the other examples. They might work with the example behavior type shown in *Example 2*, but it is unlikely that they will work with the behavior types shown in *Example 3* and *Example 4*.

The T1/T3 converter works with the example shown in Example 2.

Most of the IP having a T1 interface work with the example shown in *Example 1*.

In terms of protocol specification, *Example 3* is a violation of the rule stating that there cannot be an R\_REQ without a REQ, so *Example 3* is not allowed in type 1 protocol.

It is also true that, for timing reasons, *Example 2* is unlikely, even if it could be useful for slow peripherals (so slow that timing is easily met).

The example shown in *Example 1* is the most likely and currently the most widely supported, but is inefficient. The example shown in *Example 2* represents the optimum solution in cases of multi-cell packet operations. So the examples shown in *Example 1* and *Example 2* are the only examples allowed.

Note: It is possible that an incompatibility among IPs working only following the example shown in Example 1, and IPs working following the example shown in Example 2, must be solved at hardware level.

## 3.2 Type 2 protocol (basic)

The type 2 or basic STBus interface increases the performance and functionality of the STBus ports. It supports all type 1 functionality and adds split transactions and the ability to support all transactions including compound operations, source labelling and some priority and transaction labelling/hint information.

It is targeted at devices which need high performance and pipelined operation but do not require the additional system efficiency associated with shaped request/response packets or the ability to re-order outstanding operations to improve performances.

Simple devices are required to support the following signals for a type 2 interface: REG, GNT, EOP, ADD, OPC, BE, DATA, R\_OPC, R\_EOP, R\_DATA, however, certain operations also require support for LCK and the initiator may choose to implement additional optional functionality as shown by the signals described in the following section. The system also allows a robust error handling model to be implemented. While this is recommended, some systems may choose not to implement this functionality.

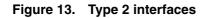

## 3.2.1 Type 2 interface definition

1. VLD is equivalent to R\_REQ for initiators and can be assumed to be R\_REQ in a system for which R\_GNT is always '1'.

#### 3.2.2 Type 2 signals and timings

The signals listed in *Table 10* are defined for type 2 initiators and targets. Signals which are mandatory for an interface are marked with 'M', signals which are optional and should only be implemented if required are marked with 'O'. Signals marked with '-' are not used.

| Circul array                | Eull nome                                   | Signal name                          | Divention      | Initiator            |      | Target |      |

|-----------------------------|---------------------------------------------|--------------------------------------|----------------|----------------------|------|--------|------|

| Signal group                | Full name                                   | Signal name                          | Direction      | Timing               | Туре | Timing | Туре |

|                             | request                                     | REQ                                  | init to target | early <sup>(1)</sup> | М    | late   | М    |

| Request flow<br>control and | grant                                       | GNT                                  | target to init | late                 | М    | early  | М    |

| atomicity and<br>framing    | end of packet <sup>(2)</sup>                | EOP                                  | init to target | early                | 0    | late   | М    |

| Iranning                    | lock <sup>(3)</sup>                         | LCK                                  | init to target | early                | 0    | late   | -    |

|                             | opcode                                      | OPC[6:0]                             | init to target | early                | М    | late   | М    |

|                             | opcode                                      | OPC[7] <sup>(4)</sup>                | init to target | early                | 0    | late   | М    |

|                             | address                                     | ADD[31:size <sup>(5)</sup> ]         | init to target | early                | М    | late   | М    |

|                             | byte enable <sup>(6)</sup>                  | BE[(2 <sup>size</sup> -1):0]         | init to target | early                | 0    | late   | М    |

|                             | data <sup>(7)</sup>                         | DATA[(8 * 2 <sup>size</sup> -1):0]   | init to target | early                | 0    | late   | 0    |

| Request cell<br>content     | source identity <sup>(8)</sup>              | SRC[9:0]                             | init to target | early                | 0    | late   | -    |

|                             | not end of message <sup>(9)</sup>           | TID[4]                               | init to target | early                | 0    | late   | -    |