# Linux support package (LSP) v2.3 for SPEAr

# Introduction

SPEAr is a family of highly customizable ARM-based embedded MPUs suitable for use in many different kinds of application.

SPEAr Linux Support Package consists of a collection of all the Linux drivers that control the specific hardware controllers embedded in SPEAr as well as the set of bootloaders for performing the low level hardware configuration and loading of the Linux OS.

LSPv2.3 handles, in a single source tree, the following SPEAr devices: SPEAr600, SPEAr300, SPEAr310 and SPEAr320.

LSPv2.3 is integrated into the STLinux 2.3 distribution, which is a full featured distro consisting of more than 500 RPM packages.

Please refer to http://www.stlinux.com for more details.

# Contents

| 1 | Boot   | loader c  | overview                                        |  |

|---|--------|-----------|-------------------------------------------------|--|

|   | 1.1    | XLoader   |                                                 |  |

|   |        | 1.1.1     | Building XLoader                                |  |

|   | 1.2    | U-Boot    |                                                 |  |

|   |        | 1.2.1     | U-Boot overview                                 |  |

|   |        | 1.2.2     | Features                                        |  |

|   |        | 1.2.3     | Building U-Boot                                 |  |

|   |        | 1.2.4     | U-Boot commands                                 |  |

|   |        | 1.2.5     | Booting Linux with U-Boot                       |  |

| 2 | Linux  | OS and    | I device driver general information             |  |

| 3 | Platfo | rm sect   | ion                                             |  |

|   | 3.1    | General   | purpose timer (GPT) driver 25                   |  |

|   |        | 3.1.1     | Hardware overview                               |  |

|   |        | 3.1.2     | Software overview                               |  |

|   |        | 3.1.3     | GPT driver usage                                |  |

|   | 3.2    | Vector in | nterrupt controller (VIC) driver 31             |  |

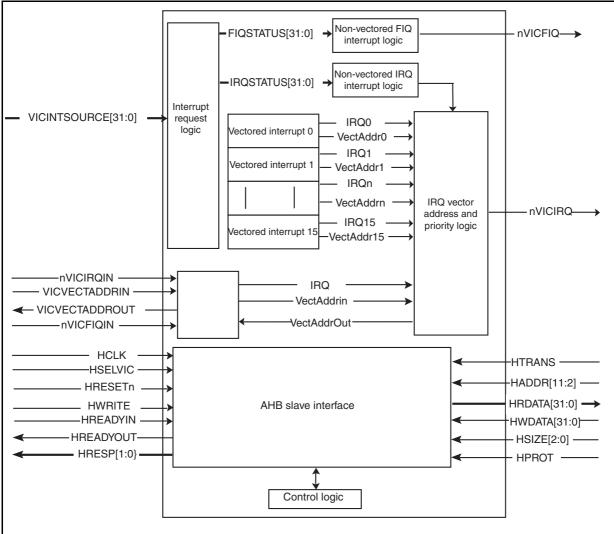

|   |        | 3.2.1     | Hardware overview                               |  |

|   |        | 3.2.2     | Software overview                               |  |

|   |        | 3.2.3     | VIC API : high level IRQ flow handlers in SPEAR |  |

|   |        | 3.2.4     | The internals of interrupt handling in ARM      |  |

|   |        | 3.2.5     | VIC usage                                       |  |

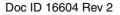

|   | 3.3    | Real tim  | e clock (RTC) driver                            |  |

|   |        | 3.3.1     | Hardware overview                               |  |

|   |        | 3.3.2     | Software overview                               |  |

|   |        | 3.3.3     | RTC driver usage                                |  |

|   |        | 3.3.4     | References                                      |  |

| 4 | Comn   | nunicati  | on device drivers 43                            |  |

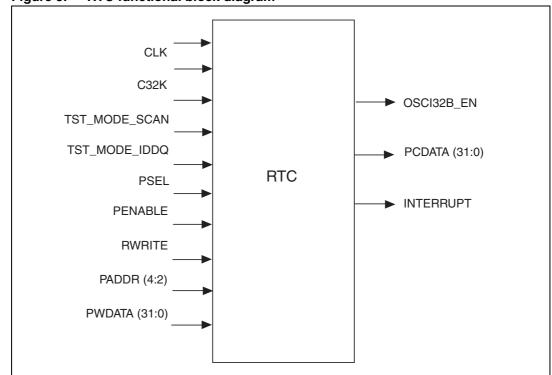

|   | 4.1    | GMAC E    | Ethernet driver                                 |  |

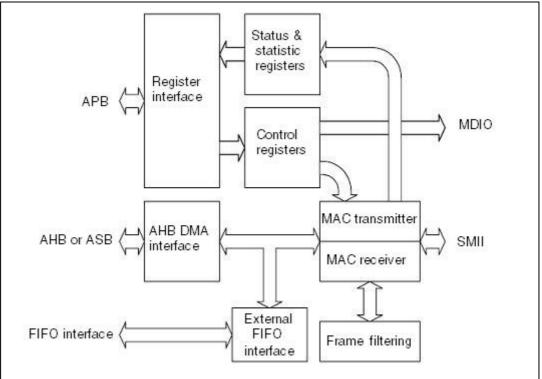

|   |        | 4.1.1     | Hardware overview                               |  |

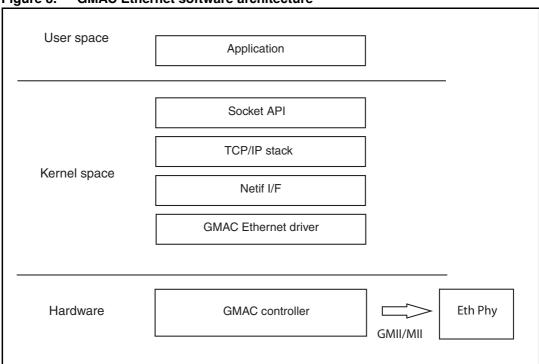

|   |        | 4.1.2     | Software overview                               |  |

|   |        | 4.1.3     | GMAC API                                        |  |

Doc ID 16604 Rev 2

|     | 4.1.4    | Concept of socket buffers 4                   | 9 |

|-----|----------|-----------------------------------------------|---|

|     | 4.1.5    | GMAC driver usage5                            | 0 |

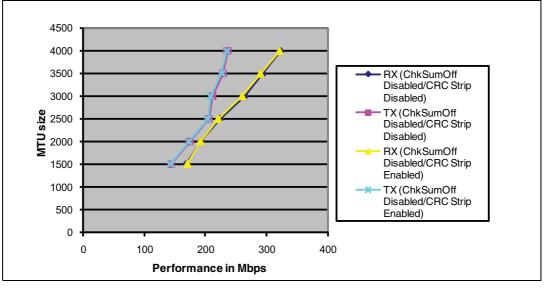

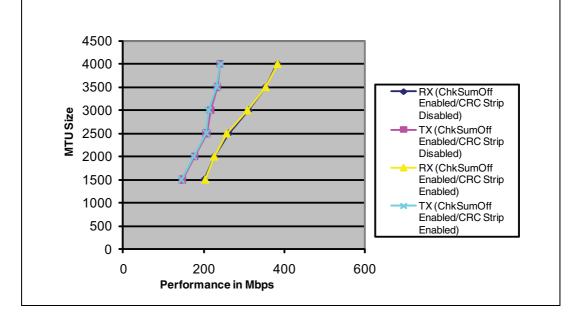

|     | 4.1.6    | GMAC driver performance5                      | 2 |

| 4.2 | MACB     | (MAC block) driver                            | 5 |

|     | 4.2.1    | Hardware overview5                            | 5 |

|     | 4.2.2    | Software overview                             | 7 |

|     | 4.2.3    | MACB driver interface                         | 7 |

|     | 4.2.4    | Socket buffer management5                     | 9 |

|     | 4.2.5    | Cache coherency                               | 9 |

|     | 4.2.6    | Packet reception6                             | 0 |

|     | 4.2.7    | Packet transmission6                          | 0 |

|     | 4.2.8    | MACB driver usage6                            | 0 |

|     | 4.2.9    | Kernel configuration options6                 | 0 |

| 4.3 | USB Ho   | ost6                                          | 1 |

|     | 4.3.1    | Hardware overview6                            | 1 |

|     | 4.3.2    | USB host API                                  | 2 |

|     | 4.3.3    | USB host usage                                | 2 |

|     | 4.3.4    | USB Host performance6                         | 6 |

|     | 4.3.5    | Kernel configuration options6                 | 7 |

| 4.4 | USB De   | evice                                         | 9 |

|     | 4.4.1    | Hardware overview6                            | 9 |

|     | 4.4.2    | Software overview                             | 0 |

|     | 4.4.3    | USBD driver interface with Linux gadget layer | 1 |

|     | 4.4.4    | Composite device interface7                   | 2 |

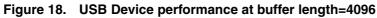

|     | 4.4.5    | USBD driver performance7                      | 6 |

|     | 4.4.6    | Configuration options7                        | 7 |

|     | 4.4.7    | References                                    | 8 |

| 4.5 | I2C driv | /er                                           | 8 |

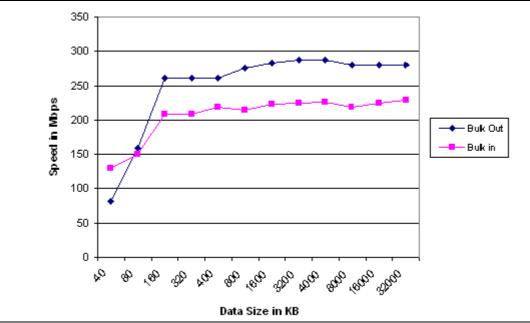

|     | 4.5.1    | Hardware overview7                            | 8 |

|     | 4.5.2    | Software overview                             | 9 |

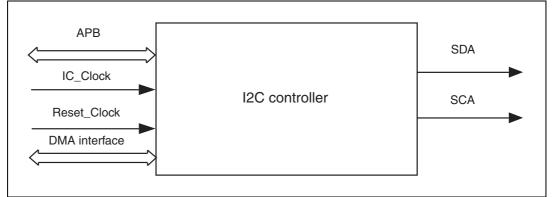

|     | 4.5.3    | I2C framework in linux                        | 0 |

|     | 4.5.4    | Adding a new I2C client driver 8              | 1 |

|     | 4.5.5    | I2C driver performance8                       | 4 |

|     | 4.5.6    | Known issues or limitations8                  | 5 |

|     | 4.5.7    | Configuration options                         | 6 |

|     | 4.5.8    | References                                    | 6 |

| 4.6  | SPI dri | ver                                        |

|------|---------|--------------------------------------------|

|      | 4.6.1   | Hardware overview                          |

|      | 4.6.2   | Software overview                          |

|      | 4.6.3   | SPI framework in Linux                     |

|      | 4.6.4   | Un-registering the driver92                |

|      | 4.6.5   | Known issues or limitations92              |

|      | 4.6.6   | SPI device driver performance              |

|      | 4.6.7   | Configuration options                      |

|      | 4.6.8   | References                                 |

| 4.7  | SDIO o  | driver                                     |

|      | 4.7.1   | Hardware overview93                        |

|      | 4.7.2   | Software overview94                        |

|      | 4.7.3   | SDIO/SD/MMC usage in Linux95               |

|      | 4.7.4   | SDIO host controller driver performance    |

|      | 4.7.5   | Configuration options                      |

|      | 4.7.6   | References                                 |

| 4.8  | UART    | driver                                     |

|      | 4.8.1   | Hardware overview                          |

|      | 4.8.2   | Software overview                          |

|      | 4.8.3   | TTY framework in Linux                     |

|      | 4.8.4   | Configuration options                      |

| 4.9  | CAN d   | river                                      |

|      | 4.9.1   | Hardware overview                          |

|      | 4.9.2   | Software overview                          |

|      | 4.9.3   | Socket-CAN framework in Linux107           |

|      | 4.9.4   | SPEAr CAN driver                           |

|      | 4.9.5   | User-land applications over the CAN driver |

|      | 4.9.6   | Netlink interface for the CAN driver110    |

|      | 4.9.7   | Kernel configuration options110            |

|      | 4.9.8   | References                                 |

| 4.10 | HDLC    | driver                                     |

|      | 4.10.1  | Hardware overview111                       |

|      | 4.10.2  | Software overview                          |

|      | 4.10.3  | SPEAr HDLC driver interface                |

|      | 4.10.4  | Driver parameters117                       |

|      | 4.10.5  | Assigning timeslots for TDM/E1 interface   |

57

|   |      | 4.10.6     | Application code                        |

|---|------|------------|-----------------------------------------|

|   |      | 4.10.7     | Test utilities                          |

|   |      | 4.10.8     | List HDLC channels                      |

|   |      | 4.10.9     | Raw data test                           |

|   |      | 4.10.10    | Configuration options                   |

|   |      | 4.10.11    | References                              |

| 5 | Non- | volatile   | memory device drivers 123               |

|   | 5.1  | NAND F     | Flash driver                            |

|   |      | 5.1.1      | Hardware overview                       |

|   |      | 5.1.2      | Software overview                       |

|   |      | 5.1.3      | NAND device driver overview             |

|   |      | 5.1.4      | NAND device usage                       |

|   |      | 5.1.5      | NAND Flash file system image creation   |

|   |      | 5.1.6      | NAND device driver performance          |

|   |      | 5.1.7      | Configuration options                   |

|   |      | 5.1.8      | References                              |

|   | 5.2  | EMI inte   | erface driver                           |

|   |      | 5.2.1      | Hardware overview                       |

|   |      | 5.2.2      | Software overview                       |

|   | 5.3  | Serial N   | IOR Flash driver                        |

|   |      | 5.3.1      | Hardware overview                       |

|   |      | 5.3.2      | Software overview                       |

|   |      | 5.3.3      | Serial NOR device driver overview       |

|   |      | 5.3.4      | NOR Flash file system image creation147 |

|   |      | 5.3.5      | Serial NOR device usage147              |

|   |      | 5.3.6      | Serial NOR device driver performance149 |

|   |      | 5.3.7      | Configuration options                   |

|   |      | 5.3.8      | References                              |

|   | 5.4  | USB ma     | ass storage support                     |

|   | 5.5  | I2C and    | I SPI memory device support 151         |

|   | 5.6  | SD/MM      | C memory support                        |

|   |      |            |                                         |

| 6 | Acce | elerator e | engine device drivers 152               |

|   | 6.1  | JPEG d     | river                                   |

|   |      | 6.1.1      | Hardware overview                       |

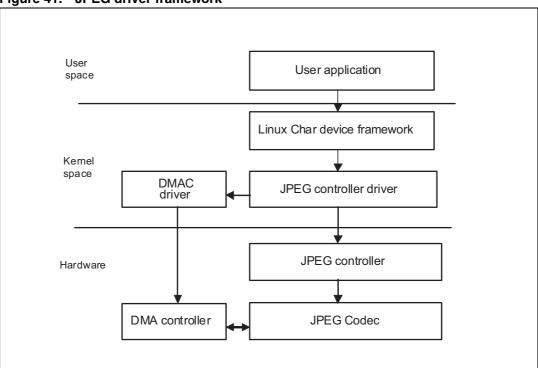

|   |       | 6.1.2    | Software overview              | 153 |

|---|-------|----------|--------------------------------|-----|

|   |       | 6.1.3    | JPEG device driver performance | 162 |

|   |       | 6.1.4    | References                     | 162 |

|   | 6.2   | General  | purpose DMA (DMAC) driver      | 162 |

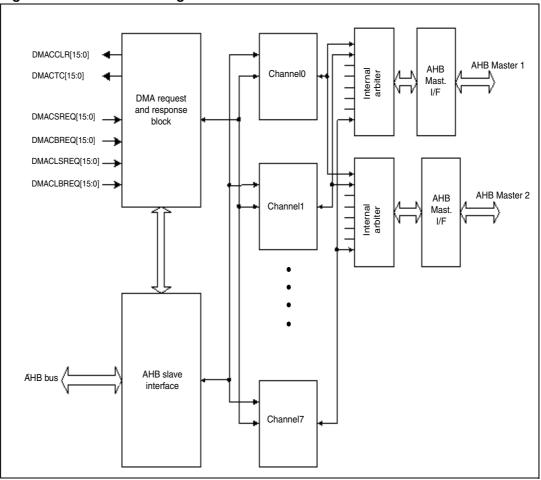

|   |       | 6.2.1    | Hardware overview              | 162 |

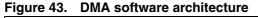

|   |       | 6.2.2    | Software overview              | 164 |

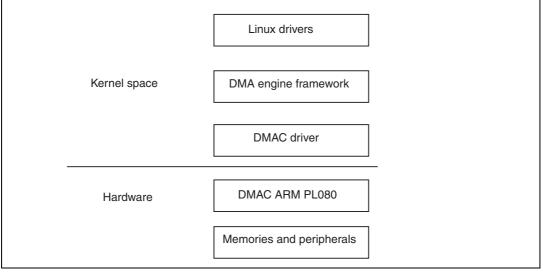

|   |       | 6.2.3    | DMA device driver performance  | 172 |

|   |       | 6.2.4    | Configuration options          | 173 |

|   |       | 6.2.5    | References                     | 173 |

| 7 | Huma  | n interf | ace device (HID) drivers 1     | 174 |

|   | 7.1   | Touchso  | reen driver                    | 174 |

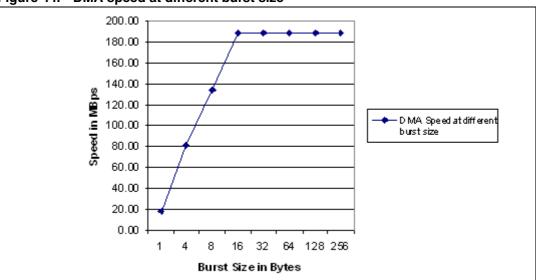

|   |       | 7.1.1    | Hardware overview              |     |

|   |       | 7.1.2    | Software overview              |     |

|   |       | 7.1.3    | Touchscreen driver overview    | 175 |

|   |       | 7.1.4    | Touchscreen usage              | 177 |

|   |       | 7.1.5    | References                     | 178 |

|   | 7.2   | Keypad   | driver                         | 178 |

|   |       | 7.2.1    | Hardware overview              | 178 |

|   |       | 7.2.2    | Software overview              | 179 |

|   |       | 7.2.3    | Customizing the keypad driver  | 181 |

|   |       | 7.2.4    | Keypad usage                   | 182 |

|   |       | 7.2.5    | Configuration options          | 183 |

|   | 7.3   | ADC dri  | ver                            | 183 |

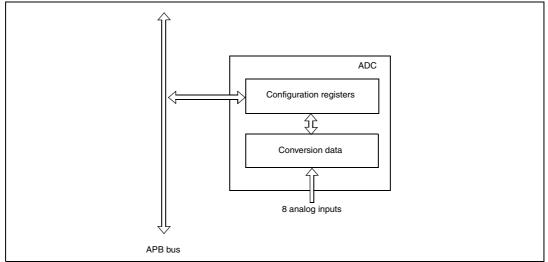

|   |       | 7.3.1    | Hardware overview              | 183 |

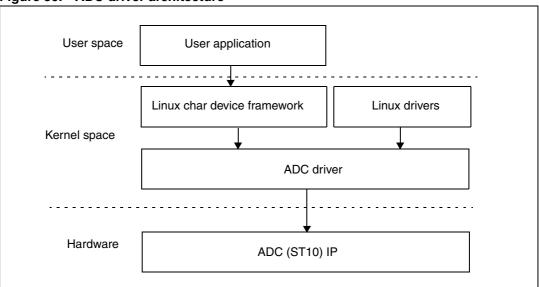

|   |       | 7.3.2    | Software overview              | 184 |

|   |       | 7.3.3    | ADC usage in Linux             | 185 |

|   |       | 7.3.4    | Known issues or limitations    | 190 |

|   |       | 7.3.5    | ADC device driver performance  | 190 |

|   |       | 7.3.6    | Configuration options          | 190 |

|   |       | 7.3.7    | References                     | 190 |

|   |       | 7.3.8    | LCD panel support              | 190 |

|   |       | 7.3.9    | USB HID Class Support          | 190 |

| 8 | Audio | /video d | drivers 1                      | 191 |

|   | 8.1   | LCD cor  | ntroller (CLCD) driver         | 191 |

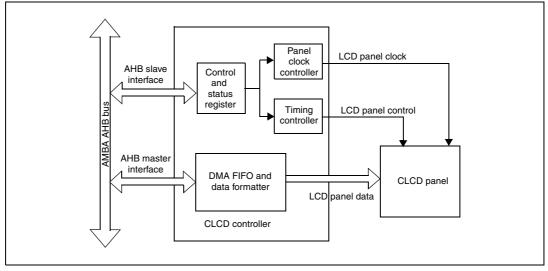

|   |       | 8.1.1    | Hardware overview              |     |

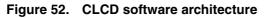

|    |      | 8.1.2   | Software overview                                       | 192   |

|----|------|---------|---------------------------------------------------------|-------|

|    |      | 8.1.3   | CLCD device driver interface with framebuffer layer     | 192   |

|    |      | 8.1.4   | How to support a new CLCD panel                         | 195   |

|    |      | 8.1.5   | CLCD driver usage                                       | 195   |

|    |      | 8.1.6   | Kernel configuration options                            | 197   |

|    |      | 8.1.7   | References                                              | 198   |

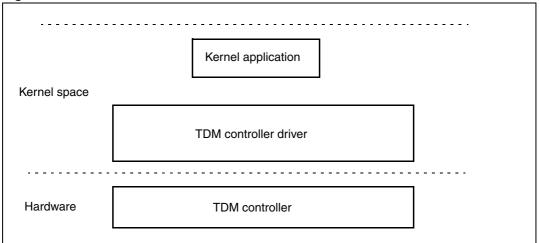

|    | 8.2  | TDM c   | lriver                                                  | 198   |

|    |      | 8.2.1   | Hardware overview                                       | 198   |

|    |      | 8.2.2   | Software overview                                       | 199   |

|    |      | 8.2.3   | TDM layer interface                                     | 200   |

|    |      | 8.2.4   | Configuration options                                   | 205   |

|    |      | 8.2.5   | References                                              | 205   |

|    | 8.3  | USB a   | udio device class support                               | 205   |

| 9  | Misc | ellaneo | ous device drivers                                      | 206   |

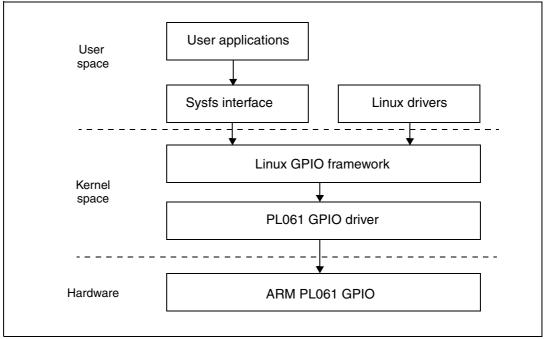

|    | 9.1  | Gener   | al purpose I/O (GPIO) driver                            | 206   |

|    |      | 9.1.1   | Hardware overview                                       | 206   |

|    |      | 9.1.2   | Software overview                                       | 208   |

|    |      | 9.1.3   | GPIO usage in user mode                                 | 209   |

|    |      | 9.1.4   | GPIO usage in kernel mode                               | 209   |

|    |      | 9.1.5   | GPIO in interrupt mode                                  | 210   |

|    |      | 9.1.6   | Configuration options                                   | 211   |

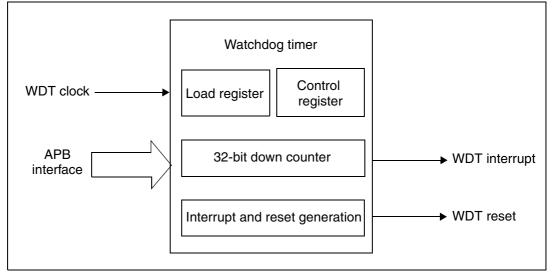

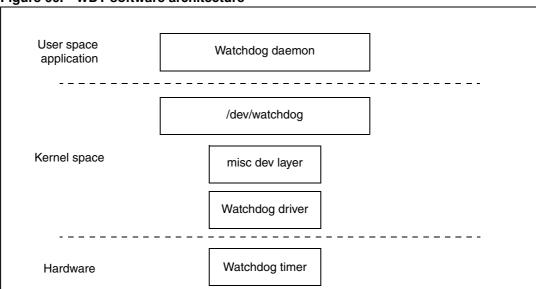

|    | 9.2  | Watch   | dog (WDT) driver                                        | 211   |

|    |      | 9.2.1   | Hardware overview                                       | 211   |

|    |      | 9.2.2   | Software overview                                       | 212   |

|    |      | 9.2.3   | Watchdog device driver interface with misc device layer | 213   |

|    |      | 9.2.4   | Watchdog driver usage                                   | 213   |

|    |      | 9.2.5   | Configuration options                                   | 215   |

|    |      | 9.2.6   | References                                              | 215   |

|    | 9.3  | Pulse   | width modulator (PWM) driver                            | 215   |

|    |      | 9.3.1   | Hardware overview                                       | 215   |

|    |      | 9.3.2   | Software overview                                       | 217   |

|    |      | 9.3.3   | PWM usage in Linux                                      | 217   |

|    |      | 9.3.4   | Configuration options                                   | 218   |

|    |      | 9.3.5   | References                                              | 219   |

| 10 | Pow  | er mana | agement section                                         | 220   |

| 57 |      |         | Doc ID 16604 Rev 2                                      | 7/245 |

| Doc ID | 16604 | Rev 2 |

|--------|-------|-------|

|--------|-------|-------|

|          | 10.1    | Hardwa    | re overview                         | 0 |

|----------|---------|-----------|-------------------------------------|---|

|          |         | 10.1.1    | Power management techniques         | 0 |

|          | 10.2    | Softwar   | e overview                          | 2 |

|          |         | 10.2.1    | Linux power management PM framework | 3 |

|          |         | 10.2.2    | Linux clock framework               | 3 |

|          |         | 10.2.3    | CPU frequency framework 225         | 5 |

|          | 10.3    | Power n   | nanagement API                      | 7 |

|          |         | 10.3.1    | PM framework API                    | 7 |

|          |         | 10.3.2    | Clock framework API                 | 8 |

|          |         | 10.3.3    | CPU freq framework API              | 1 |

|          | 10.4    | Usage a   | and performance                     | 3 |

|          |         | 10.4.1    | Usage: Linux PM framework           | 3 |

|          |         | 10.4.2    | Usage: clock framework              | 3 |

|          |         | 10.4.3    | Usage: CPUfreq user interface       | 5 |

|          |         | 10.4.4    | Performance                         | 8 |

|          | 10.5    | Configu   | ration options                      | C |

|          |         | 10.5.1    | Linux PM framework                  | 0 |

|          |         | 10.5.2    | Linux clock framework               | 0 |

|          |         | 10.5.3    | Linux CPU freq framework            | 1 |

| 11       | Flashi  | ing utili | ty section                          | 2 |

| Appendix | A Ac    | cronym    | s                                   | 3 |

| Revision | history | /         |                                     | 4 |

# List of tables

| Table 1.  | Informative U-Boot commands                         |      |

|-----------|-----------------------------------------------------|------|

| Table 2.  | Memory U-Boot commands                              | . 17 |

| Table 3.  | Persistent storage U-Boot commands (I2C, NOR, NAND) | . 18 |

| Table 4.  | Network U-Boot commands                             |      |

| Table 5.  | Image booting U-Boot commands                       | . 20 |

| Table 6.  | Environment variables U-Boot commands               | . 20 |

| Table 7.  | Serial i/f file loading U-Boot commands             | . 20 |

| Table 8.  | Miscellaneous U-Boot commands                       | . 21 |

| Table 9.  | LSP v2.3 device drivers                             | . 23 |

| Table 10. | GPTs available on SPEAr.                            | . 26 |

| Table 11. | Differences between SPEAr600 and SPEAr300           | . 32 |

| Table 12. | Format of interrupt source list                     | . 38 |

| Table 13. | RTC ioctl requests                                  | . 41 |

| Table 14. | RTC menuconfig kernel options                       | . 42 |

| Table 15. | SPEAr600 Ethernet evaluation results                | . 52 |

| Table 16. | Menuconfig options                                  | . 54 |

| Table 17. | Other options                                       | . 55 |

| Table 18. | Menuconfig options.                                 | . 60 |

| Table 19. | USB host configuration in SPEAr                     | . 61 |

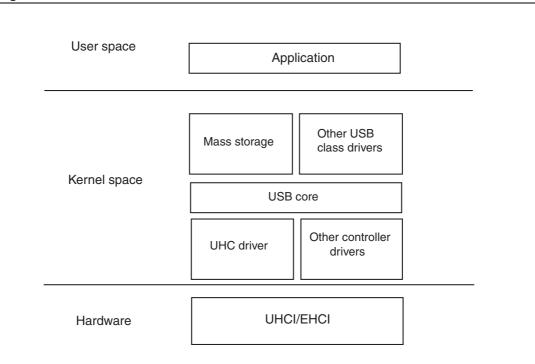

| Table 20. | USB Host device performance results                 | . 66 |

| Table 21. | USB host configurations                             | . 67 |

| Table 22. | Linux gadget endpoint APIs                          |      |

| Table 23. | USB device control APIs                             |      |

| Table 24. | USBD performance results                            |      |

| Table 25. | Linux kernel configuration                          |      |

| Table 26. | I2C at clock speed=100                              |      |

| Table 27. | I2C at clock speed=400                              |      |

| Table 28. | I2C configuration options                           |      |

| Table 29. | Section of active CSx signal by GPIO7 and GPIO6     |      |

| Table 30. | SPI driver configuration options                    |      |

| Table 31. | SDIO configuration options                          |      |

| Table 32. | IOCTL requests for serial ports                     |      |

| Table 33. | Control signal constants                            |      |

| Table 34. | UART menuconfig kernel options                      |      |

| Table 35. | CAN menuconfig kernel options                       |      |

| Table 36. | Menuconfig options.                                 |      |

| Table 37. | Results on SPEAr600                                 |      |

| Table 38. | Results on SPEAr600                                 |      |

| Table 39. | NAND Flash driver configuration options             |      |

| Table 40. | Supported transactions.                             |      |

| Table 41. | Results on SPEAr600                                 |      |

| Table 42. | Serial NOR menuconfig options                       |      |

| Table 43. | JPEG driver configuration options                   |      |

| Table 44. | DMA device performance results                      |      |

| Table 45. | DMA configuration options                           |      |

| Table 46. | Configuration options                               |      |

| Table 47. | PL GPIO keypad pins                                 |      |

| Table 48. | Keypad configuration options                        |      |

|           |                                                     |      |

# List of figures

| Figure 1.  | SPEAr booting stages                                                   | 13  |

|------------|------------------------------------------------------------------------|-----|

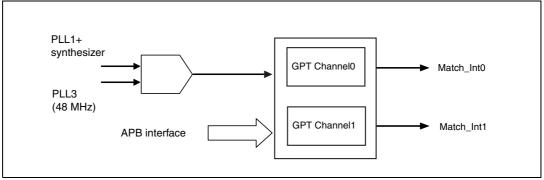

| Figure 2.  | GPT hardware interface                                                 |     |

| Figure 3.  | GPT software architecture                                              |     |

| Figure 4.  | VIC block diagram                                                      | 33  |

| Figure 5.  | RTC functional block diagram.                                          | 39  |

| Figure 6.  | RTC software system architecture                                       | 40  |

| Figure 7.  | GMAC block diagram                                                     |     |

| Figure 8.  | GMAC Ethernet software architecture                                    |     |

| Figure 9.  | Ethernet performance evaluation results (Checksum offloading disabled) |     |

| Figure 10. | Ethernet performance evaluation results (Checksum offloading enabled)  |     |

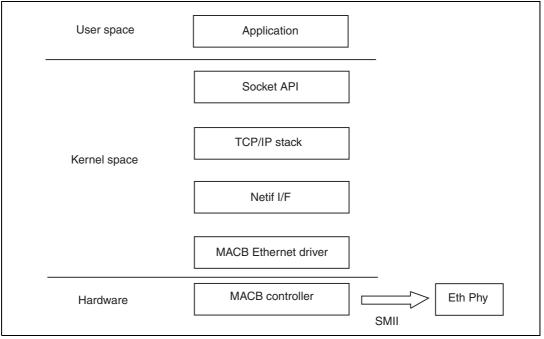

| Figure 11. | MACB diagram                                                           |     |

| Figure 12. | MACB software layers                                                   |     |

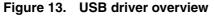

| Figure 13. | USB driver overview                                                    |     |

| Figure 14. | USB Host performance at buffer length=4096                             |     |

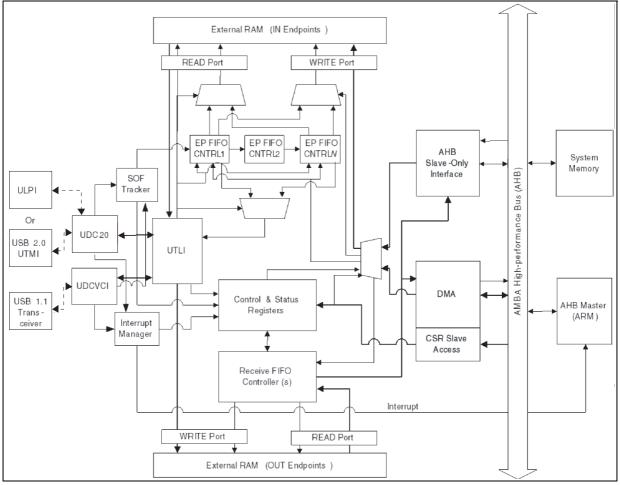

| Figure 15. | USBD interface                                                         |     |

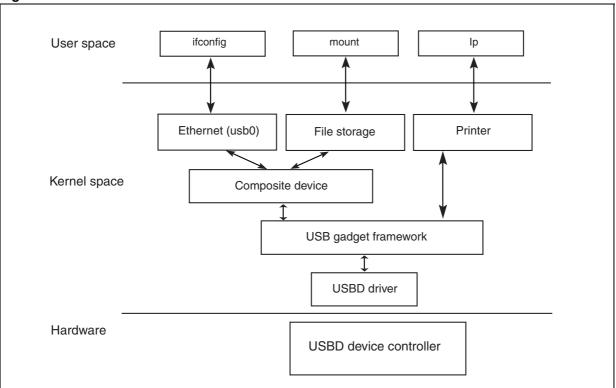

| Figure 16. | USBD software architecture                                             |     |

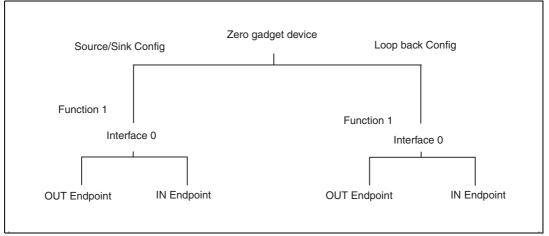

| Figure 17. | Zero gadget device                                                     |     |

| Figure 18. | USB Device performance at buffer length=4096                           |     |

| Figure 18. | I2C hardware architecture                                              |     |

|            | I2C framework architecture                                             |     |

| Figure 20. |                                                                        |     |

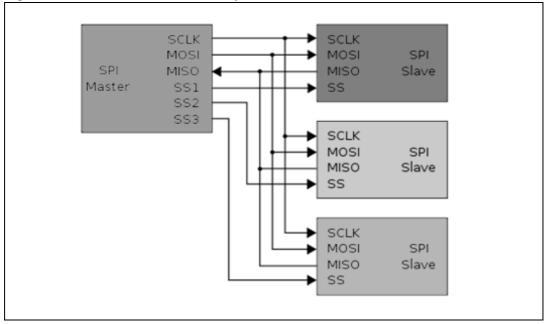

| Figure 21. | Master slave connectivity                                              |     |

| Figure 22. | SPI driver architecture                                                |     |

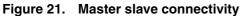

| Figure 23. | SDIO block diagram                                                     |     |

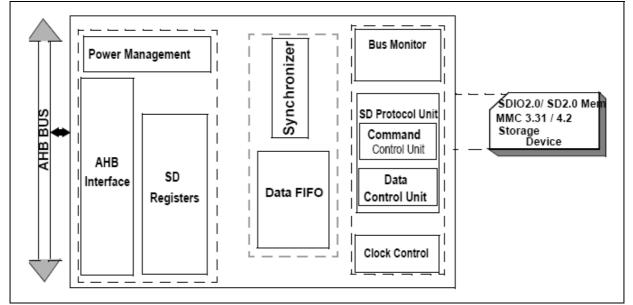

| Figure 24. | SD/SDIO/MMC Linux protocol stack.                                      |     |

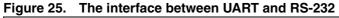

| Figure 25. | The interface between UART and RS-232                                  |     |

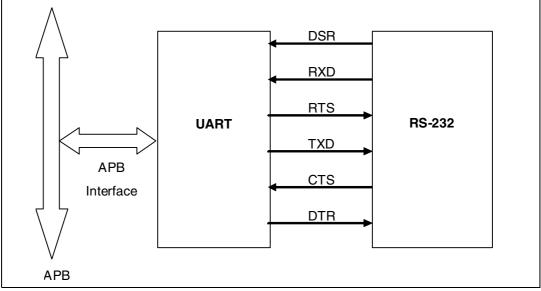

| Figure 26. | UART software system architecture                                      |     |

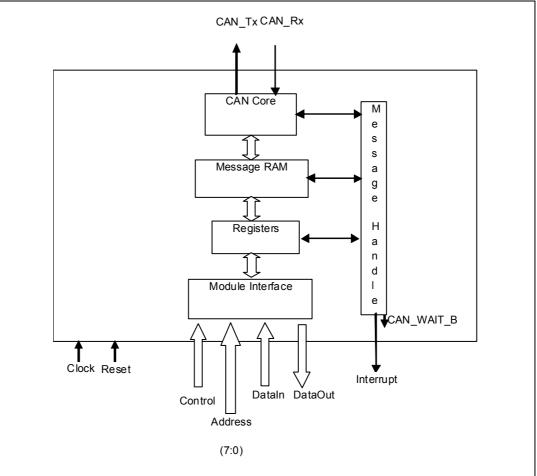

| Figure 27. | Block diagram of CAN IP                                                |     |

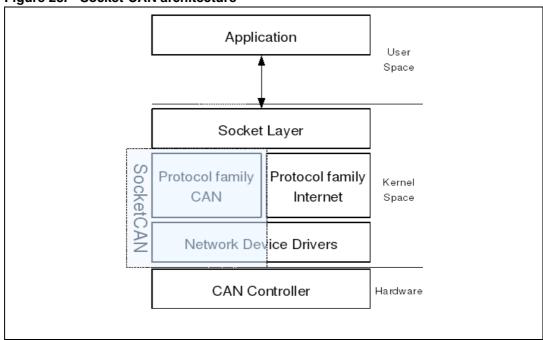

| Figure 28. | Socket-CAN architecture                                                |     |

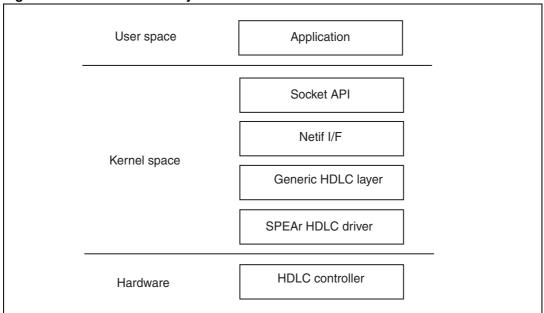

| Figure 29. | HDLC software system architecture                                      |     |

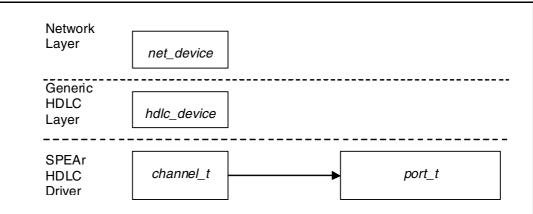

| Figure 30. | Data structure layers                                                  |     |

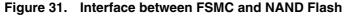

| Figure 31. | Interface between FSMC and NAND Flash                                  |     |

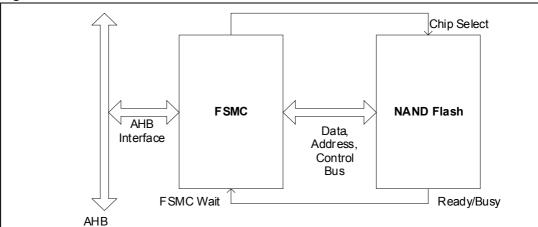

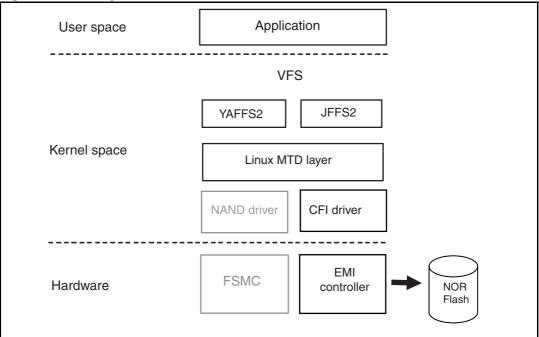

| Figure 32. | NAND software system architecture                                      | 124 |

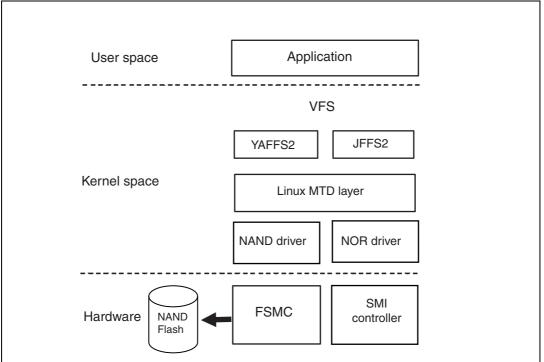

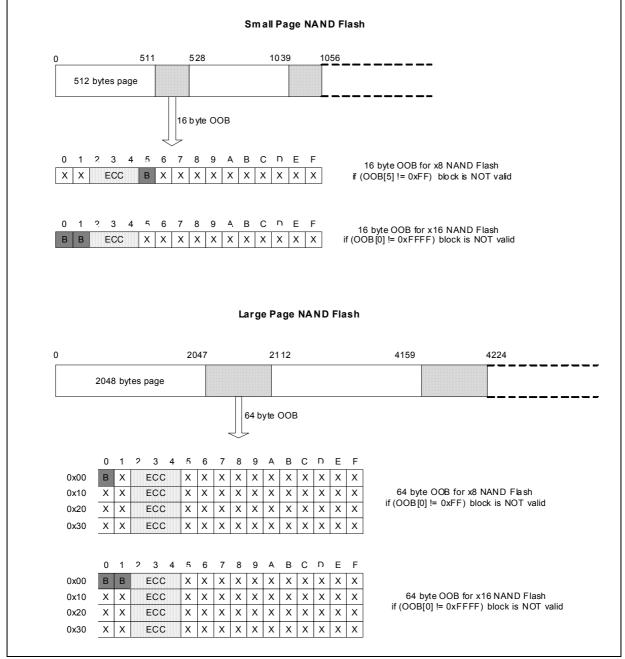

| Figure 33. | OOB layout for various size NAND Flash                                 | 129 |

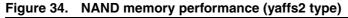

| Figure 34. | NAND memory performance (yaffs2 type)                                  | 136 |

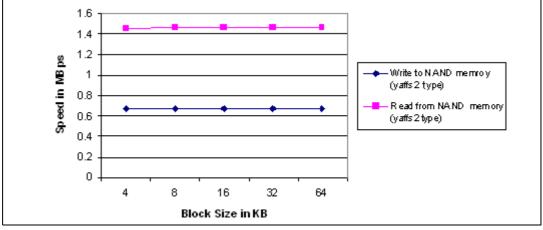

| Figure 35. | NAND memory performance (jffs2 type)                                   | 137 |

| Figure 36. | EMI system software architecture                                       | 140 |

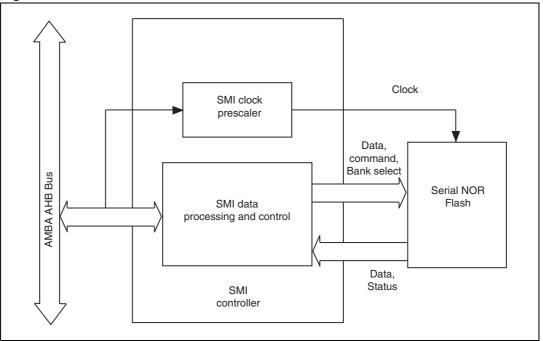

| Figure 37. | The interface between NOR Flash and SMI controller                     | 144 |

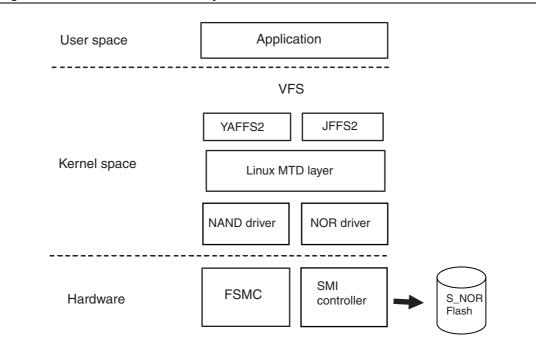

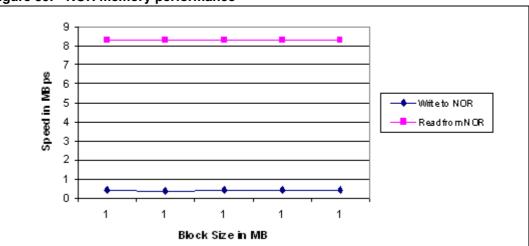

| Figure 38. | NOR Flash software system architecture                                 | 145 |

| Figure 39. | NOR memory performance                                                 |     |

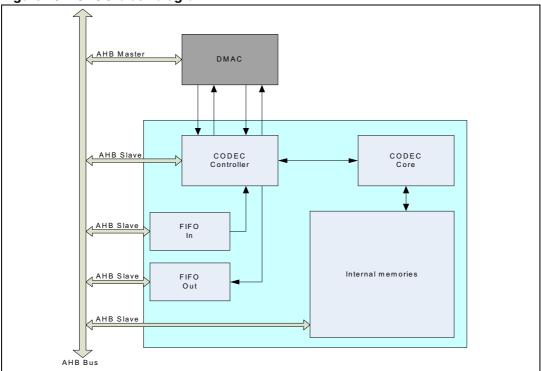

| Figure 40. | JPGC block diagram                                                     |     |

| Figure 41. | JPEG driver framework                                                  |     |

| Figure 42. | DMAC block diagram                                                     |     |

| Figure 43. | DMA software architecture                                              |     |

| Figure 44. | DMA speed at different burst size                                      |     |

| Figure 45. | Interfacing between CLCD panel and SPEAr                               |     |

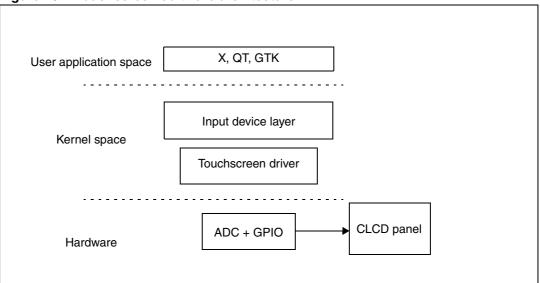

| Figure 46. | Touchscreen software architecture.                                     |     |

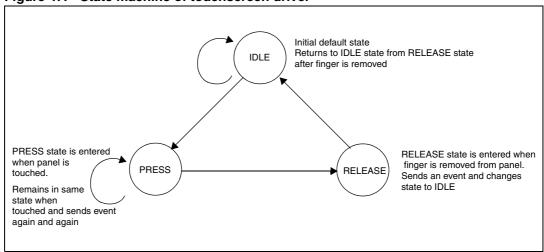

| Figure 47. | State machine of touchscreen driver                                    |     |

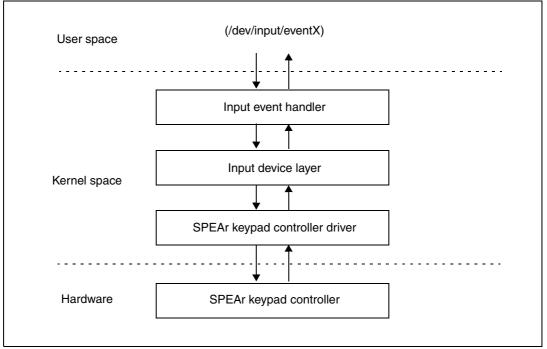

| Figure 48. | Keypad driver architecture overview.                                   |     |

|            |                                                                        |     |

| ADC block diagram.                                      | . 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

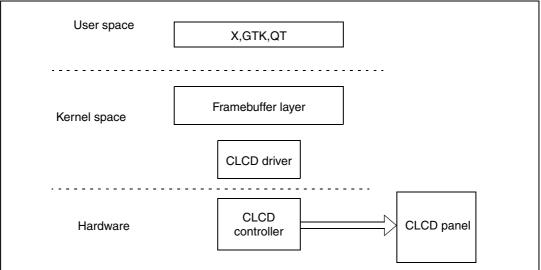

| Block diagram of CLCD controller                        | . 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLCD software architecture                              | . 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

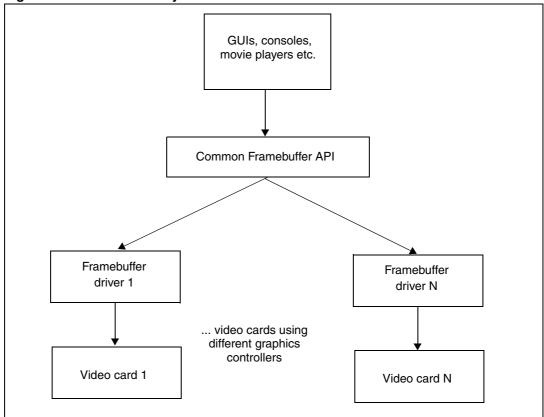

| Framebuffer layer of Linux                              | . 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

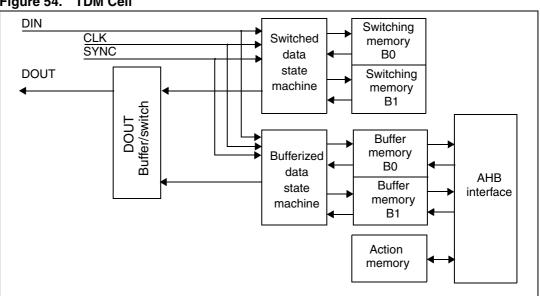

| TDM Cell                                                | . 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

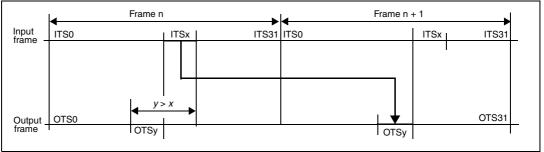

| TDM waveforms                                           | . 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDM driver architecture                                 | . 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

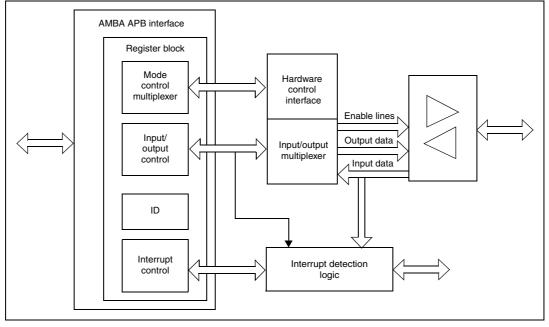

| GPIO block diagram                                      | . 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO driver architecture                                | . 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WDT interface                                           | . 212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WDT software architecture                               | . 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

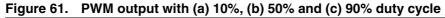

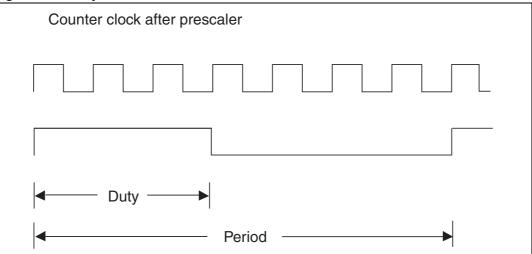

| PWM output with (a) 10%, (b) 50% and (c) 90% duty cycle | . 216                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Duty and Period                                         | . 217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

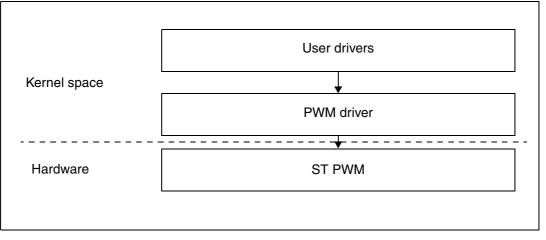

| PWM driver architecture                                 | . 217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

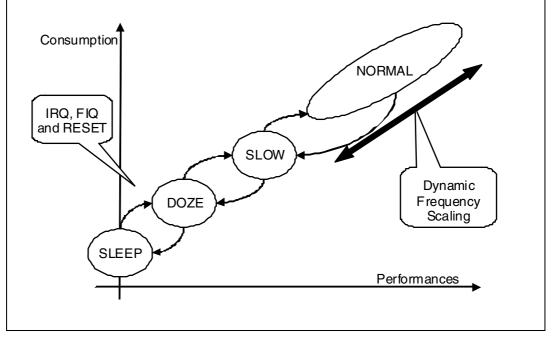

| System control state machine                            | . 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

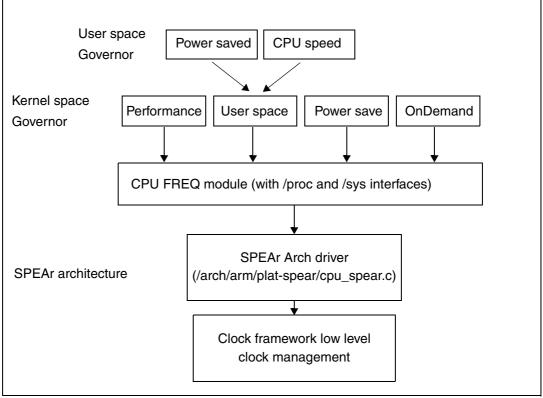

| CPU freq kernel architectural blocks                    | . 225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

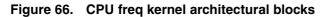

| Linux PM framework                                      | . 227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

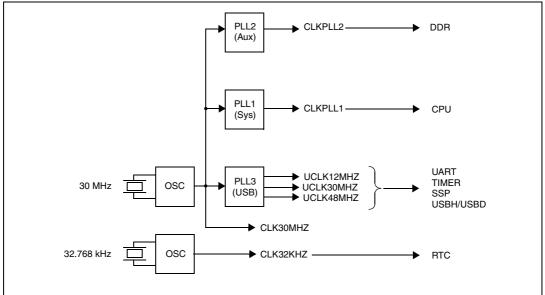

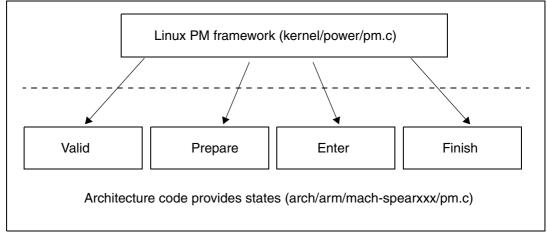

| Clock framework architecture                            | . 229                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

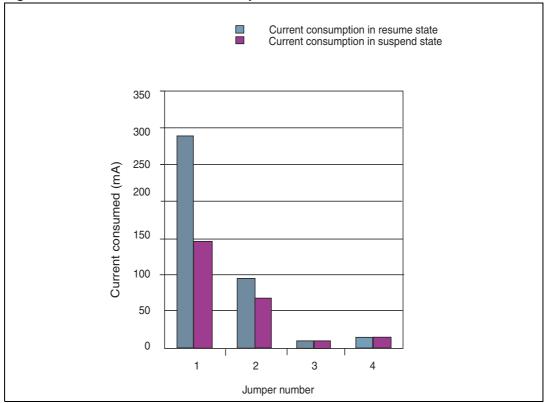

| SPEAr600 current consumption chart                      | . 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

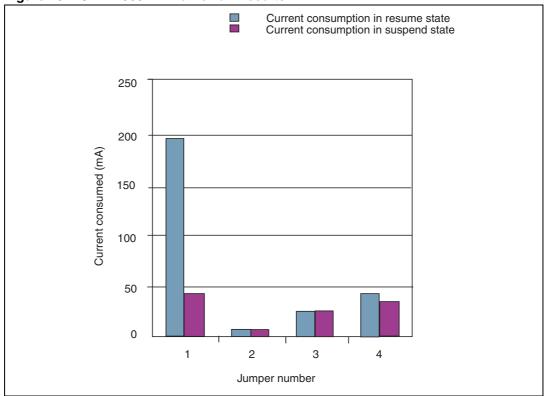

| SPEAr300 PM framework results                           | . 240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                         | ADC block diagram.<br>ADC driver architecture .<br>Block diagram of CLCD controller .<br>CLCD software architecture .<br>Framebuffer layer of Linux .<br>TDM Cell .<br>TDM waveforms .<br>TDM driver architecture .<br>GPIO block diagram .<br>GPIO block diagram .<br>GPIO driver architecture .<br>WDT interface .<br>WDT software architecture .<br>PWM output with (a) 10%, (b) 50% and (c) 90% duty cycle .<br>Duty and Period .<br>PWM driver architecture .<br>System control state machine .<br>SPEAr clock tree .<br>CPU freq kernel architecture .<br>SPEAr 600 current consumption chart .<br>SPEAr300 PM framework results . |

# **1** Boot loader overview

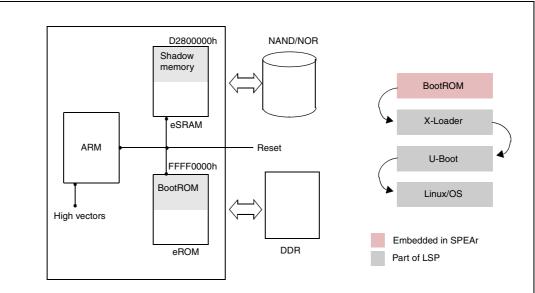

The SPEAr boot process is divided into four different stages. On power-on the BootROM hard coded in the silicon (eROM) starts (first stage). Its role is to locate XLoader and transfer the control to it. The BootROM is embedded in the silicon and is not part of the LSP.

The following sections describe the features offered by the components which are not embedded in the silicon (XLoader and U-Boot) because they are usually board dependent and need to be customized by the user. These components are part of LSP v2.3.

For a detailed description, please refer to the corresponding SPEAr datasheet and user manual.

Figure 1. SPEAr booting stages

# 1.1 XLoader

XLoader is a small firmware loaded during the second stage of the boot phase by the BootROM.

The main steps performed by XLoader in LSP v2.3 are:

- Initializing the DDR and PLLs at 333 MHz

- Passing of board information (DDR size etc.) to U-Boot

- Loading the U-Boot from NAND, NOR depending on boot type selection and transferring the control to it.

The XLoader coming with the LSP v2.3 is licensed under GPLv2 and distributed in full source code. This distributed XLoader version runs on the SPEAr hardware development kits. You have to customize Xloader to run it on a different PCB, especially the MPMC

settings required for different DDR memory hardware and routing. Please refer to one of the following application notes for more information on MPMC configuration:

- AN3100, Configuring the SPEAr3xx multi-port memory controller (MPMC) for external DDR SDRAM

- AN3132, Configuring the SPEAr600 multi-port memory controller (MPMC) for external DDR SDRAM.

# 1.1.1 Building XLoader

To build XLoader, you need to use the STLinux toolchain and run the following commands:

```

/* Build XLoader for SPEAr600 target with DDR@333MHz for size 128MB*/

# make SOC=SPR600 DDRFREQ=333 DDRSIZE=128M

/* Build XLoader for SPEAr300 target with DDR@333MHz for size 128MB*/

# make SOC=SPR300 DDRFREQ=333 DDRSIZE=128M

/* Build XLoader which could be used as a firmware for initializing

* DDR with USB Flashing utility

*/

# make SOC=SPR600 DDRFREQ=166 DDRSIZE=128M CONSOLE=USB

/* Build XLoader for all platform and all types (normal XLoader

* and Flashing utility firmware

*/

# ./makeall

```

The XLoader source can be compiled with various options, which are listed below:

- make SOC=SPR300: This option generates XLoader for the requested platform. Other platform options can be SPR600, SPR310 and SPR320.

- make DDRFREQ=333: This option generates XLoader binary image with DDR driver that supports 333 MHz operation. To generate XLoader for DDR @166 MHZ pass DDRFREQ=166. This option is available for SPEAr3XX and SPEAr600

- make DDRSIZE=128M: This option generates XLoader for DDR size of 128 MB. An other possible parameter can be 64 M to generate 64 MB XLoader.

- make CONSOLE=USB: This option generates XLoader which is used as a firmware to initialize DDR in USB flashing utility.

- make DDRFREQ=333 DDRCONF=ASYNC: This option generates XLoader to configure DDR @333 MHz asynchronoulsy, for example the DDR is driven through the clock from PLL2 rather than PLL1 (synchronous operation). This option only works for DDR @333 MHz. This XLoader can be used with some features of Linux Power Management (like CPU-Freq) which currently guarantees only the system stability with asynchronous DDR operation.

# 1.2 U-Boot

Das U-Boot is an open source boot monitor available for a wide range of embedded processors architectures. A boot monitor is a small piece of software that executes after powering up an embedded system. It can be used to achieve the following objectives:

- Monitor the system for develop/debug purpose

- Boot an OS

Das U-Boot starts from the second sector of Serial NOR Flash, from where it is loaded in RAM by XLoader.

Note: In case of NAND it starts from the fifth sector.

Das U-Boot coming with the LSP v2.3 is licensed under GPLv2 and it is distributed in full source code. This distributed U-Boot version runs on the SPEAr hardware development kits.

# 1.2.1 U-Boot overview

The U-Boot bootloader is based on U-Boot-1.3.1 release. This U-Boot source supports the complete SPEAr embedded MPU family (SPEAr600, SPEAr300, SPEAr310 and SPEAr320). The U-Boot is loaded into DDR2 from NOR (parallel/serial) or NAND memory device and executed from DDR2. It initializes the following IPs or has the drivers for the following IPs.

- UART

- I2C

- Ethernet

- Serial NOR through SMI

- NAND device through FSMC

- Parallel NOR (only in SPEAr310)

- USB Device

## 1.2.2 Features

U-Boot for SPEAr devices supports the following features:

- Provides a first level debug environment for on-board testing

- Supports erasing/writing to NAND/NOR memory devices

- Supports uploading binary images through Ethernet or Serial port

- Supports booting the OS (Linux, VxWorks etc)

- Acts as a firmware for flashing utilities. It supports USB TTY driver.

# 1.2.3 Building U-Boot

To build U-Boot for both serial NOR and NAND Flash, you need to use the STLinux toolchain and run the following commands:

```

/* Build U-Boot for SPEAr600 target */

# make spear600_config

Generating include/autoconf.mk

Configuring for spear600 board...

# make

/* Build U-Boot for SPEAr300 target */

# make spear300_config

Generating include/autoconf.mk

```

Configuring for spear300 board... # make /\* Build U-Boot for SPEAr310 target \*/

```

# make spear310_config

Generating include/autoconf.mk

Configuring for spear310 board...

```

```

# make

/* Build U-Boot for SPEAr320 target */

# make spear320_config

Generating include/autoconf.mk

Configuring for spear320 board...

# make

```

The U-Boot source can be compiled with various options, which are listed below:

- make CONSOLE=USB: This option generates firmware binary image (containing TTY over USB driver) to be downloaded for the operation of the Flashing Utility (refer to the Section 11: Flashing utility section). This option is available for SPEAr3xx and SPEAr600.

- make ENV=NAND: This option generates U-Boot/firmware image which saves environment variables in NAND device. This option is available for SPEAr3xx and SPEAr600.

- make FLASH=PNOR: This option generates an image that supports parallel NOR in place of serial NOR Flash drivers. It is applicable only for SPEAr310.

# 1.2.4 U-Boot commands

You can display the complete list of U-Boot commands using the 'help' command.

```

spear600> help

?

- alias for 'help'

autoscr - run script from memory

base - print or set address offset

bdinfo - print Board Info structure

- boot default, for example, run 'bootcmd'

boot

- boot default, for example, run 'bootcmd'

bootd

bootm

- boot application image from memory

bootp - boot image via network using BootP/TFTP protocol

- Perform CDP network configuration

cdp

cmp

- memory compare

coninfo - print console devices and information

- memory copy

ср

crc32

- checksum calculation

- invoke DHCP client to obtain IP/boot params

dhcp

echo

- echo args to console

erase

- erase FLASH memory

flinfo - print FLASH memory information

- start application at address 'addr'

αo

help

- print online help

i2c

- I2C sub-system

iminfo - print header information for application image

- list all images found in flash

imls

itest - return true/false on integer compare

loadb

- load binary file over serial line (kermit mode)

loads

- load S-Record file over serial line

- load binary file over serial line (ymodem mode)

loadv

loop

- infinite loop on address range

md

- memory display

- memory modify (auto-incrementing)

mm

- simple RAM test

mtest

- memory write (fill)

mw

- NAND sub-system

nand

nboot - boot from NAND device

nfs

- boot image via network using NFS protocol

nm

- memory modify (constant address)

```

| 1 0        | send ICMP ECHO_REQUEST to network host print environment variables |

|------------|--------------------------------------------------------------------|

| protect -  | enable or disable FLASH write protection                           |

| rarpboot-  | boot image via network using RARP/TFTP protocol                    |

| reset -    | Perform RESET of the CPU                                           |

| run -      | run commands in an environment variable                            |

| saveenv -  | save environment variables to persistent storage                   |

| saves -    | save S-Record file over serial line                                |

| setenv -   | set environment variables                                          |

| setfreq -  | change ddr/cpu frequency                                           |

| sleep -    | delay execution for some time                                      |

| tftpboot-  | boot image via network using TFTP protocol                         |

| version -  | print monitor version                                              |

| writemac - | - write mac address in I2C memory                                  |

Commands can be grouped into the following categories, according to their function:

### Informative commands

This group of commands is used to get runtime information concerning the system itself. For example, using the 'bdinfo' command, you can retrieve the XLoader image revision.

| Command | Behavior                                                                                                                                                                             | Example                                                                                                                                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bdinfo  | Print board info structure<br>Along with other things, this structure<br>also contains<br>– Frequency at which DDR is operating<br>– DDR type (DDR2/DDRMOBILE)<br>– XLoader revision | <pre>spear60&gt; bdinfo arch_number = 0x000008BC env_t = 0x0000000 boot_params = 0x0000000 DRAM bank = 0x0000000 -&gt; start = 0x0000000 -&gt; size = 0x08000000 DDR Freq = 333 DDR Type = DDR2 ethaddr = 55:66:77:88:99:00 ip_addr = 192.168.1.10 baudrate = 115200 bps XLoader Rev = XLoader-SPEAr600</pre> |

| help    | Print online help                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                               |

| version | Print monitor version                                                                                                                                                                |                                                                                                                                                                                                                                                                                                               |

Table 1. Informative U-Boot commands

### Memory commands

U-Boot offers the possibility to interact with the memory subsystem (RAM, ROM, Flash, ...) using a set of basic commands to move data to/from memory, compare memory locations, change memory locations and test memory.

| Table 2. | Memory | U-Boot commands |

|----------|--------|-----------------|

|----------|--------|-----------------|

| Command | Behavior                                        | Example        |

|---------|-------------------------------------------------|----------------|

| base    | Print or set address offset for memory commands | base 0x1300000 |

| md      | Memory display                                  | md 0x1300000   |

| Mm      | Memory modify (auto-incrementing)               | mm 0x1300000   |

| Command | Behavior                             | Example                                                                                                         |

|---------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| mtest   | Simple RAM test                      | mtest 0x1600000 0x1610000 0xff                                                                                  |

| Mw      | Memory write fill                    | mw.l 0x1600000 0x55aa55aa 0x100                                                                                 |

| Nm      | Memory modify (constant address)     | nm 0x1600000<br>01600000: 00000000 ? abcdabcd<br>01600000: abcdabcd ? 12345678<br>01600000: 12345678 ? 87654321 |

| стр     | Memory compare                       | cmp.b 0x1300000 0x1600000<br>0x200000                                                                           |

| Ср      | Memory copy                          | ср.ь 0x1300000 0x1600000<br>0x300000                                                                            |

| Itest   | Return true/false on integer compare |                                                                                                                 |

| Іоор    | Infinite loop on address range       | loop 0x1300000 0x10000                                                                                          |

Table 2.

Memory U-Boot commands (continued)

## Persistent storage commands

This section describes the U-Boot commands used to access non-volatile storage.

| Command | Behavior                                       | Example                                                                                                                                                                                                                            |

|---------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| erase   | Erase Flash memory                             | erase 0xf8000000 +0x10000<br>erase 1:0-3                                                                                                                                                                                           |

| flinfo  | Print Flash memory information                 |                                                                                                                                                                                                                                    |

| i2c     | I2C subsystem commands                         | i2c md 0x50 0x0<br>0000: 14 15 16 17 18 19 1a 1b 1c<br>1d 1e 1f 20 21 22 23<br>!"#                                                                                                                                                 |

| iminfo  | Print header information for application image | <pre>iminfo 0xf8000000 ## Checking Image at f8000000 Image Name: XLoader Image Type: ARM Linux Kernel Image (uncompressed) Data Size: 4472 Bytes = 4.4 kB Load Address: d2800b00 Entry Point: d2800b00 Verifying Checksum OK</pre> |

| imls    | List all images found in NAND/NOR<br>Flash     |                                                                                                                                                                                                                                    |

| nand    | NAND command subsystem                         | nand read.jffs2 0x1300000 0x0<br>0x10000                                                                                                                                                                                           |

| nboot   | Boot from NAND device                          | <pre>nboot.jffs2 0x1300000 0 0x60000 for the image to boot automatically, an environment variable "autostart" is to be set to "yes"</pre>                                                                                          |

Table 3.

Persistent storage U-Boot commands (I2C, NOR, NAND)

| Command  | Behavior                                                                                                                                                                                                    | Example                               |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| cmp      | Memory compare                                                                                                                                                                                              | cmp.b 0x1300000 0x1600000<br>0x200000 |

| ср       | Memory copy                                                                                                                                                                                                 | ср.b 0x1300000 0x1600000<br>0x300000  |

| writemac | Write MAC address in I2C memory<br>This command writes 0x55 and 0xAA<br>as magic number(to say that MAC id is<br>present here) at offset 0 and 1 in the<br>chip and stores the MAC address from<br>offset 2 | writemac 00:99:88:77:66:55            |

| protect  | Enable or disable Flash write protection                                                                                                                                                                    | protect off 1:0-5                     |

## Table 3. Persistent storage U-Boot commands (I2C, NOR, NAND) (continued)

# Network commands

| Table 4. Network U-Boot commands |                                                                                                                                                                                                             |                            |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Command                          | Behavior                                                                                                                                                                                                    | Example                    |

| bootp                            | Boot image via network using<br>BootP/TFTP protocol                                                                                                                                                         | bootp 0x1600000 uImage     |

| cdp                              | Perform CDP network configuration                                                                                                                                                                           |                            |

| dhcp                             | Invoke DHCP client to obtain IP/boot parameters                                                                                                                                                             |                            |

| Nfs                              | Boot image via network using NFS protocol                                                                                                                                                                   |                            |

| ping                             | Send ICMP echo request to network<br>host                                                                                                                                                                   | ping 192.168.1.1           |

| tftpboot                         | Boot image via network using TFTP<br>protocol                                                                                                                                                               | tftpboot 0x1300000 uImage  |

| rarpboot                         | Boot image via network using<br>RARP/TFTP protocol                                                                                                                                                          |                            |

| writemac                         | Write MAC address in I2C memory<br>This command writes 0x55 and 0xAA<br>as magic number(to say that MAC id is<br>present here) at offset 0 and 1 in the<br>chip and stores the MAC address from<br>offset 2 | writemac 00:99:88:77:66:55 |

# Image booting commands

| Table 5. | Image booting U-Boot commands |

|----------|-------------------------------|

|----------|-------------------------------|

| Command        | Behavior                                | Example                                |

|----------------|-----------------------------------------|----------------------------------------|

| Autoscr        |                                         | autoscr 0x1600000                      |

| 71010301       |                                         | ## Executing script at 01300000        |

| Boot           | Boot default, for example 'run bootcmd' |                                        |

| Bootd          | Boot default, for example 'run bootcmd' |                                        |

|                |                                         | go 0x1300000                           |

| Go Start appli | Start application at address 'addr'     | ## Starting application at 0x013000000 |

| Bootm          | Boot application image from memory      | bootm 0x1600000                        |

## Environment variable commands

### Table 6. Environment variables U-Boot commands

| Command  | Behavior                                         | Example                                             |

|----------|--------------------------------------------------|-----------------------------------------------------|

| echo     | Echo args to console                             | echo abcd<br>abcd<br>echo \$(bootdelay)<br>1        |

| printenv | Print environment variables                      |                                                     |

| run      | Run commands in an environment variable          | echo \$(bootcmd)<br>bootm 0xf8050000<br>run bootcmd |

| saveenv  | Save environment variables to persistent storage |                                                     |

| setenv   | Set environment variables                        |                                                     |

### Serial i/f commands

## Table 7. Serial i/f file loading U-Boot commands

| Command | Behavior                                           | Example         |

|---------|----------------------------------------------------|-----------------|

| coninfo | Print console devices ad information               | Coninfo         |

| loads   | Load S-record file over serial line                | loads 0x1300000 |

| loady   | Load binary file over serial line<br>(ymodem mode) | loady 0x1300000 |

| loadb   | Load binary file over serial line (kermit mode)    | loadb 0x1300000 |

| saves   | Save S-Record file over serial line                |                 |

## Miscellaneous commands

| Command | Behavior                                                                                                                                                               | Example                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset   | Resets the CPU                                                                                                                                                         |                                                                                                                                                                                                          |

| crc32   | Crc32 checksum calculation                                                                                                                                             | crc32 0x1300000 0x10000                                                                                                                                                                                  |

| echo    | Echo args to console                                                                                                                                                   | echo abcd<br>abcd<br>echo \$(bootdelay)<br>1                                                                                                                                                             |

| setfreq | Change ddr/cpu frequency<br>This command actually assumes that<br>CPU is running on PLL1 and DDR on<br>PLL2. So, effectively, this command<br>changes PLL1/2 frequency | setfreq cpu 300<br>CPU frequency changed to 300<br>(This changes the PLL1 frequency<br>to 300 MHz)<br>setfreq ddr 300<br>DDR frequency changed to 300<br>(This changes the PLL1 frequency<br>to 300 MHz) |

| sleep   | Delay execution for some time                                                                                                                                          |                                                                                                                                                                                                          |

### Table 8. Miscellaneous U-Boot commands

# 1.2.5 Booting Linux with U-Boot

This section describes how to configure U-Boot in order to achieve different booting schemes. For example, in some environments it might be required to have a completely standalone board, while during development phase it is recommended to boot from network and to mount RootFS through NFS.

The Linux kernel accepts a command line that can be used to pass arguments to the kernel and to overwrite statically built-in values. In this way the you can change parameters without the need to rebuild the kernel. Please refer to the Linux kernel source tree file 'Linux/Documentation/kernel-parameters.txt' for a complete listing of all the supported kernel arguments.

Das U-Boot stores the argument list in the environment variable bootargs. The syntax is a sequence of items in the form key=value, where key is a well known argument defined by the kernel. The following list contains the most common arguments:

• mem=nn

This argument forces the usage of a specific amount of memory. This can be the total size of the available memory or just a subset of it. Linux will make use of this specific amount, leaving the rest to different purposes (like a 2nd OS).

setenv bootargs "mem=128M ..."

console=

Output console device and options.

setenv bootargs "console=ttyS0 ..."

• initrd=

This argument specifies the location of the initial ramdisk (if a ramdisk is used).

setenv bootargs "initrd=0x00800040,7M ..."

init=

This argument runs a specified binary (ex: /bin/sh) instead of /sbin/init as init process.

setenv bootargs "init=/bin/sh ..."

- root=

- rootdelay=

- rootfstype=

- nfsroot=

These arguments provide information about how the root file system must be mounted.

```

/* NFS mount */

setenv bootargs "root=/dev/nfs nfsroot=192.168.1.1:/home/spear600/rootfs ..."

/* MTD mount (NAND/NOR flash) */

"root=/dev/mtdblock3 rootfstype=jffs2 ..."

/* RAMDisk mount */

setenv bootargs "root=/dev/ram0 initrd=0x00800040,7M ..."

/* USB flash mount */

setenv bootargs "root=/dev/sda1 rootdelay=5 ..."

```

"ip=<client-ip>:<server-ip>:<gw-ip>:<netmask>:<hostname>:<device>:<autoconf>

This argument shows how the IP address is determined.

```

setenv bootargs

"ip=192.168.1.13:192.168.1.1:192.168.1.1:255.255.255.0:spear600:eth0:off ..."

```

#### mtdparts=

This argument overwrites the default MTD Flash partitioning.

```

/* mtdparts=<mtddef>[;<mtddef]

* <mtddef> := <mtd-id>:<partdef>[,<partdef>]

* <partdef> := <size>[@offset][<name>][ro][lk]

* <mtd-id> := unique name used in mapping driver/device (mtd->name)

* <size> := standard linux memsize OR "-" to denote all remaining space

* <name> := '(' NAME ')'

*/

```

setenv bootargs "mtdparts=SMI-NOR0:2M(PARTITION-1),3M(PARTITION-2)... "

# 2 Linux OS and device driver general information

Linux coming with the LSP v2.3, which is based on kernel version 2.6.27, is licensed under GPLv2 and distributed in full source code.

LSP v2.3 supports the following features of Linux:

- Patch for YAFFS file system support over NAND

- Support for high resolution timer

- All drivers integrated into standard Linux device model

LSP v2.3 incorporates the following SPEAr specific set of drivers:

| Section name                       | Driver name                              | SPEAr MPU    |

|------------------------------------|------------------------------------------|--------------|

| Platform section                   | General purpose timer (GPT) driver       | All          |

| Platform section                   | Vector interrupt controller (VIC) driver | All          |

| Platform section                   | Real time clock (RTC) driver             | All          |

| Communication device drivers       | GMAC Ethernet driver                     | All          |

| Communication device drivers       | MACB (MAC block) driver                  | SP310, SP320 |

| Communication device drivers       | USB Host                                 | All          |

| Communication device drivers       | USB Device                               | All          |

| Communication device drivers       | I2C driver                               | All          |

| Communication device drivers       | SPI driver                               | All          |

| Communication device drivers       | SDIO driver                              | SP300, SP320 |

| Communication device drivers       | UART driver                              | All          |

| Communication device drivers       | CAN driver                               | SP320        |

| Communication device drivers       | HDLC driver                              | SP310        |

| Non-volatile memory device drivers | NAND Flash driver                        | All          |

| Non-volatile memory device drivers | EMI interface driver                     | All          |

| Non-volatile memory device drivers | Serial NOR Flash driver                  | All          |

| Non-volatile memory device drivers | USB mass storage support                 | All          |

| Non-volatile memory device drivers | I2C and SPI memory device support        | All          |

| Non-volatile memory device drivers | SD/MMC memory support                    | SP300        |

| Accelerator engine device drivers  | JPEG driver                              | All          |

Table 9. LSP v2.3 device drivers

| Section name                            | Driver name                        | SPEAr MPU   |

|-----------------------------------------|------------------------------------|-------------|

| Accelerator engine device drivers       | General purpose DMA (DMAC) driver  | All         |

| Human interface device (HID)<br>drivers | Touchscreen driver                 | All         |