VIPower MO-5T: high-side switches for 24V systems

# Introduction

The aim of this document is to give the design engineer a comprehensive "tool kit" to better understand the behavior of VIPower high side switches, allowing easier design and saving time and money.

This document expands on the existing VIPower user manual UM1556 rev.1 covering high side switches suited to 12 V (passenger car) automotive systems, by focusing on the new family of VIPower components for 24 V (truck) applications.

The drivers concerned derive from existing state-of-the-art M0-5 technology, but cover the even harsher environmental conditions found in truck applications.

Not only is the battery voltage doubled (which goes hand in hand with the increased ISO pulse levels), but the stray inductance of the wire harness is also significantly higher compared to passenger cars. The temperature range is the same as for passenger cars, but the required lifetime of the electronics is significantly higher due to the longer average life time of a truck.

The wires on a truck with a trailer can be as long as 30–40 meters, from the rear lights of the trailer to the ECU, located at the front of the truck. Due to the larger number of bulbs driven by the high side switch in a typical truck application, the typical load current is in the same range or even higher than in 12 V systems, despite the higher battery voltage.

The High Side Drivers in 24 V systems are therefore faced with high currents in combination with a high level of stray inductance during turn-off, as experienced in short circuit conditions of the load. This causes a high level of stress at that condition, necessitating new solutions to achieve short circuit robustness at the same or even higher levels than those achieved for current 12 V systems.

This document explains the function of the VIPower drivers for 24 V systems that cover the identified requirement profile.

| 1 | New  | eatures of 24 V drivers 8                                              |  |  |  |  |

|---|------|------------------------------------------------------------------------|--|--|--|--|

|   | 1.1  | Programmable latch-off functionality                                   |  |  |  |  |

|   | 1.2  | Programmable stand-by mode 10                                          |  |  |  |  |

| 2 | Gen  | ral items                                                              |  |  |  |  |

|   | 2.1  | Application schematic (monolithic and hybrid analogue HSD)1            |  |  |  |  |

|   | 2.2  | Reverse battery protection 12                                          |  |  |  |  |

|   |      | 2.2.1 Reverse battery protection of monolithic HSDs                    |  |  |  |  |

|   |      | 2.2.2 Reverse battery protection of hybrid HSDs                        |  |  |  |  |

|   | 2.3  | Microcontroller protection 20                                          |  |  |  |  |

| 3 | Ana  | gue current sense 21                                                   |  |  |  |  |

|   | 3.1  | Introduction                                                           |  |  |  |  |

|   | 3.2  | Principle of operation                                                 |  |  |  |  |

|   | 3.3  | Indication of power limitation and overtemperature                     |  |  |  |  |

|   | 3.4  | Current sense resistor calculation                                     |  |  |  |  |

|   | 3.5  | Diagnostics                                                            |  |  |  |  |

|   |      | 3.5.1 Diagnostics with paralleled loads                                |  |  |  |  |

|   |      | 3.5.2 Diagnostics with different load options                          |  |  |  |  |

|   |      | 3.5.3 K-factor calibration method                                      |  |  |  |  |

|   |      | 3.5.4 Open load detection in off-state                                 |  |  |  |  |

|   |      | 3.5.5 Diagnostic summary                                               |  |  |  |  |

| 4 | Swit | hing inductive loads                                                   |  |  |  |  |

|   | 4.1  | Turn-on phase behavior                                                 |  |  |  |  |

|   | 4.2  | Turn-off phase behavior                                                |  |  |  |  |

|   |      | 4.2.1 Calculation of energy dissipated in the HSD                      |  |  |  |  |

|   |      | 4.2.2 Calculation example                                              |  |  |  |  |

|   | 4.3  | Proper HSD selection                                                   |  |  |  |  |

|   |      | 4.3.1 Example of VND5T100AJ driving relays                             |  |  |  |  |

|   | 4.4  | External clamping selection 48                                         |  |  |  |  |

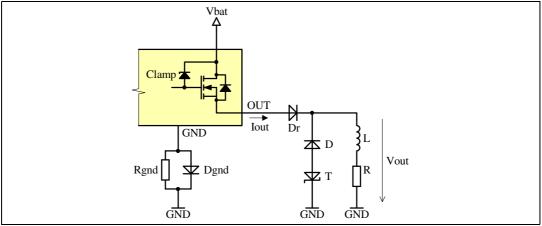

|   |      | 4.4.1 Clamping circuitry examples                                      |  |  |  |  |

|   |      | 4.4.2 Component selection guide for external transil-diode clamping 50 |  |  |  |  |

|   |      |                                                                        |  |  |  |  |

|   |                               | 4.4.3     | Example of VND5T035AJ for DC motor driving with external clamp 54             |  |  |  |

|---|-------------------------------|-----------|-------------------------------------------------------------------------------|--|--|--|

| 5 | Parall                        | eling of  | HSDs 61                                                                       |  |  |  |

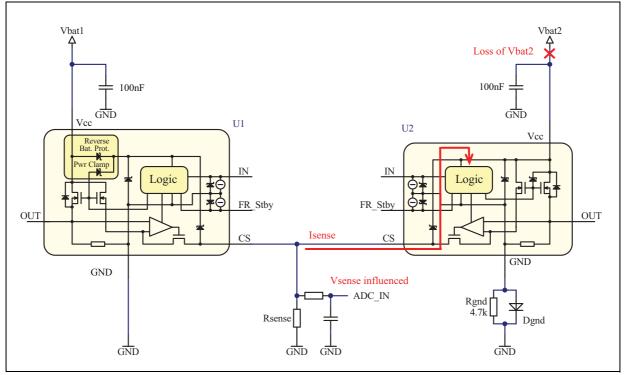

|   | 5.1                           | Paralleli | ng of FR_Stby (fault reset/standby) or IN (input)                             |  |  |  |

|   |                               | 5.1.1     | Monolithic HSDs supplied from different supply lines61                        |  |  |  |

|   |                               | 5.1.2     | Hybrid HSDs supplied from different supply lines                              |  |  |  |

|   |                               | 5.1.3     | Mix of monolithic and hybrid HSDs64                                           |  |  |  |

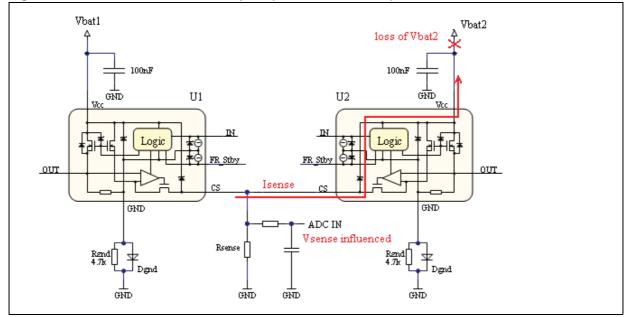

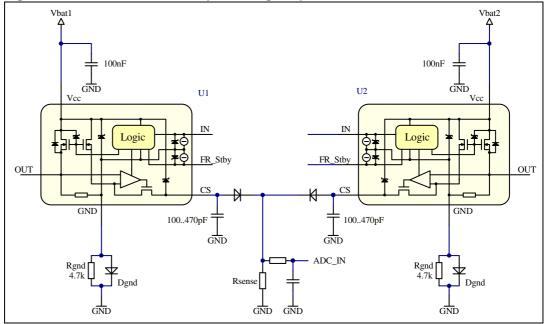

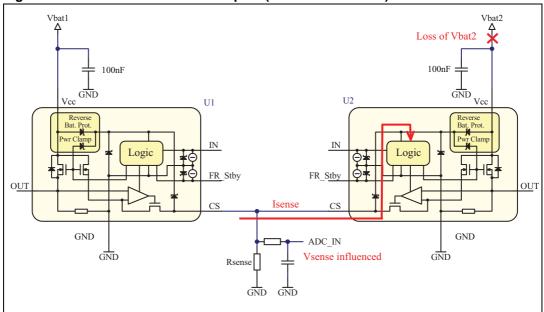

|   | 5.2                           | Paralleli | ng of CS pins (current sense) 65                                              |  |  |  |

|   |                               | 5.2.1     | Monolithic HSDs supplied from different supply lines                          |  |  |  |

|   |                               | 5.2.2     | Hybrid HSDs supplied from different supply lines67                            |  |  |  |

|   |                               | 5.2.3     | Mix of monolithic and hybrid HSDs supplied from different supply lines $\ 68$ |  |  |  |

|   | 5.3                           | Paralleli | ng of outputs                                                                 |  |  |  |

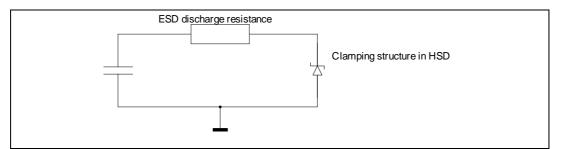

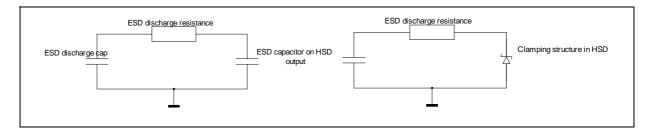

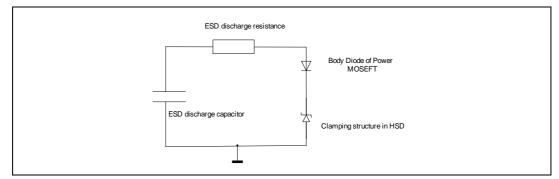

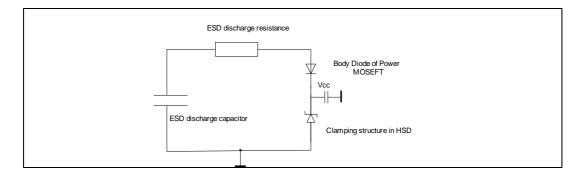

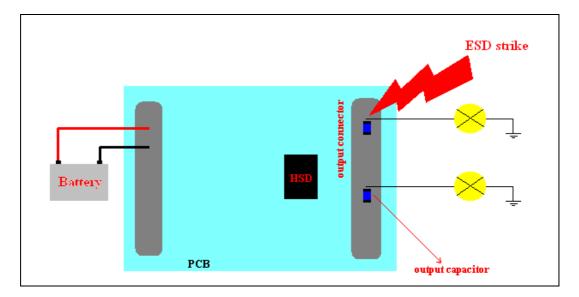

| 6 | ESD p                         | orotecti  | on                                                                            |  |  |  |

|   | 6.1                           | ESD pro   | otection of HSD – calculations                                                |  |  |  |

|   | 6.2                           | •         | otection – ECU level (layout consideration)                                   |  |  |  |

| 7 | Pobu                          | ot docio  | ın                                                                            |  |  |  |

| 1 |                               | -         |                                                                               |  |  |  |

|   | 7.1                           | Design    | suggestions for HSDs and relays on the same PCB                               |  |  |  |

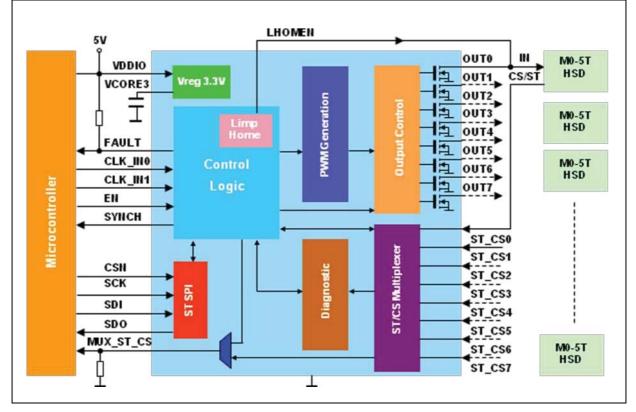

| 8 | Opera                         | ation wi  | th AMICO                                                                      |  |  |  |

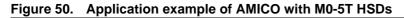

|   | 8.1                           | Introduc  | tion on AMICO                                                                 |  |  |  |

|   | 8.2                           | Control   | and diagnostic function                                                       |  |  |  |

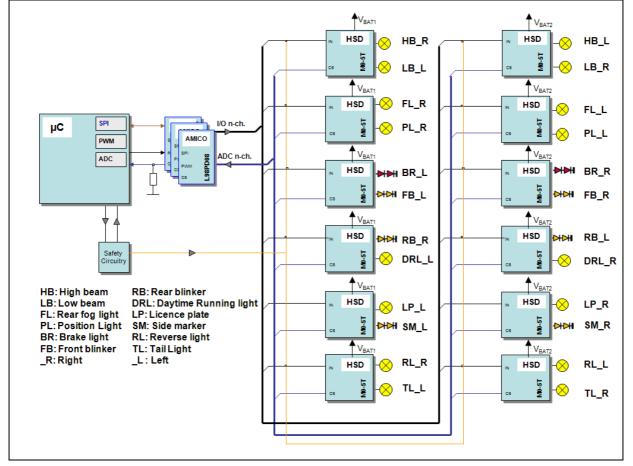

|   |                               | 8.2.1     | PWM control                                                                   |  |  |  |

|   |                               | 8.2.2     | HSD control in normal conditions                                              |  |  |  |

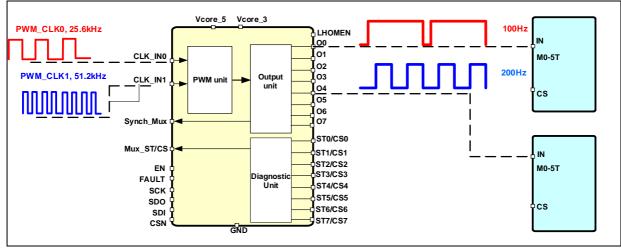

|   |                               | 8.2.3     | HSD control in limp home mode                                                 |  |  |  |

|   |                               | 8.2.4     | Diagnostic principle of the HSDs by the AMICO $\ldots \ldots \ldots 80$       |  |  |  |

|   | 8.3                           | Load co   | mpatibility                                                                   |  |  |  |

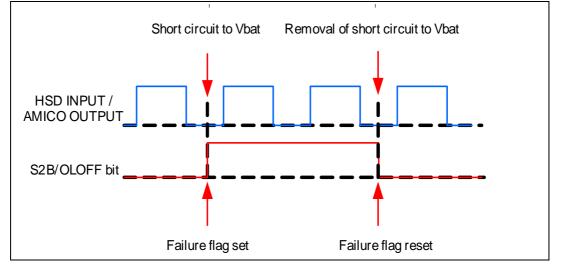

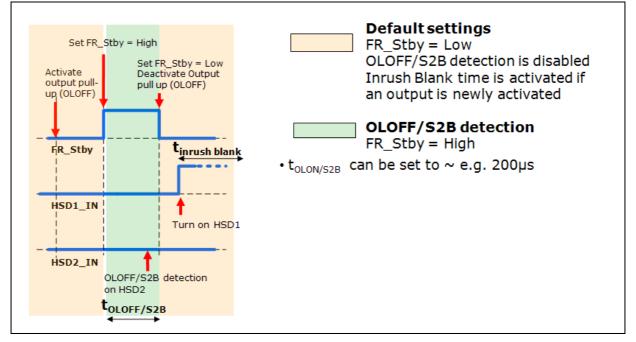

|   |                               | 8.3.1     | Inrush blanking time                                                          |  |  |  |

|   |                               | 8.3.2     | Overload and open load detection                                              |  |  |  |

|   | 8.4                           | Combin    | ing inrush blanking time and diagnostic of open load in off-state 89          |  |  |  |

|   |                               | 8.4.1     | Description of the principle                                                  |  |  |  |

|   | 8.5                           | Direct c  | urrent sense reading                                                          |  |  |  |

|   | 8.6                           | Impact of | on the accuracy of the current sense reading                                  |  |  |  |

|   | 8.7 Functional safety aspects |           |                                                                               |  |  |  |

|   |                               | 8.7.1     | Limp home mode                                                                |  |  |  |

|   |                               |           |                                                                               |  |  |  |

|               | 8.7.2    | Timeout Watchdog97                                        |

|---------------|----------|-----------------------------------------------------------|

|               | 8.7.3    | Functional safety considerations through ST SPI           |

|               | 8.7.4    | Full flexibility of the output stages and supply rails    |

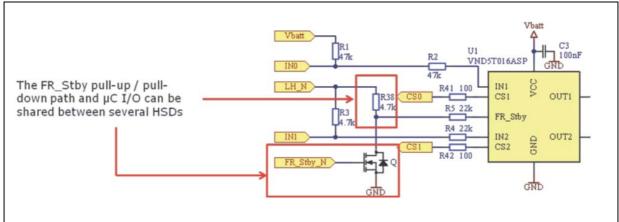

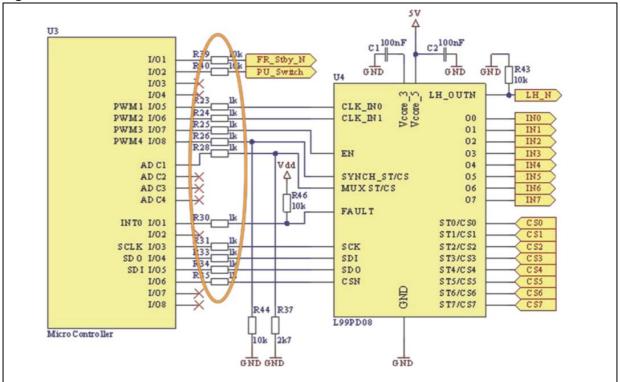

| 8.8           | Hardwa   | re guidelines                                             |

|               | 8.8.1    | Interface microcontroller/AMICO98                         |

|               | 8.8.2    | Interface HSD/AMICO                                       |

|               | 8.8.3    | Reverse battery protection                                |

|               | 8.8.4    | Pull-up/pull-down and decoupling capacitors for AMICO 107 |

| Appendix A    | Referenc | e documents                                               |

| Revision hist | ory      |                                                           |

# List of tables

| Table 1.  | Diagnostic truth table                                                          |

|-----------|---------------------------------------------------------------------------------|

| Table 2.  | Reverse battery protection (of monolithic HSDs only) – comparison               |

| Table 3.  | Paralleling bulbs-overview                                                      |

| Table 4.  | Vsense measurement                                                              |

| Table 5.  | CS pin levels in off-state                                                      |

| Table 6.  | Diagnostics-overview                                                            |

| Table 7.  | External clamping circuitry examples(1/2) 49                                    |

| Table 8.  | External clamping circuitry examples(2/2) 50                                    |

| Table 9.  | Typical load currents and HSDs' K-factors                                       |

| Table 10. | Amico's typical on-board open load and overload thresholds                      |

| Table 11. | Amico's typical on-board open load and overload thresholds                      |

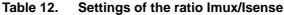

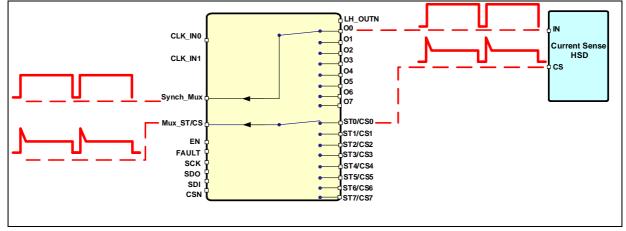

| Table 12. | Settings of the ratio Imux/Isense                                               |

| Table 13. | Specification of the current sense ratio of the VND5T100AJ95                    |

| Table 14. | Specification of AMICO's Imux/Isense ratio                                      |

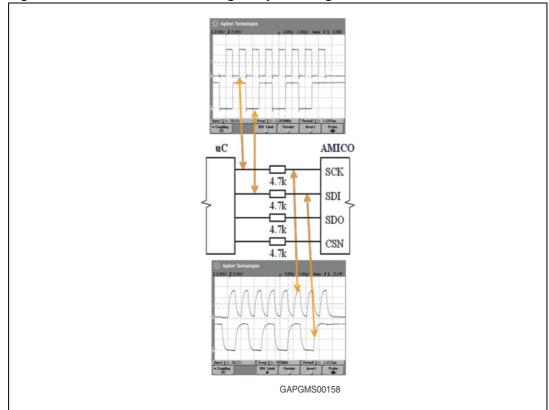

| Table 15. | Recommended max. SPI clock frequency as a function of the series resistance 100 |

| Table 16. | Document revision history                                                       |

|           |                                                                                 |

# List of figures

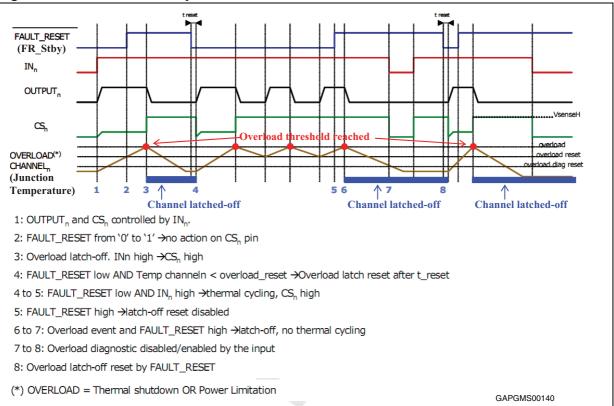

| Figure 1.  | Latch functionality – behavior in overload condition                                          | 9    |

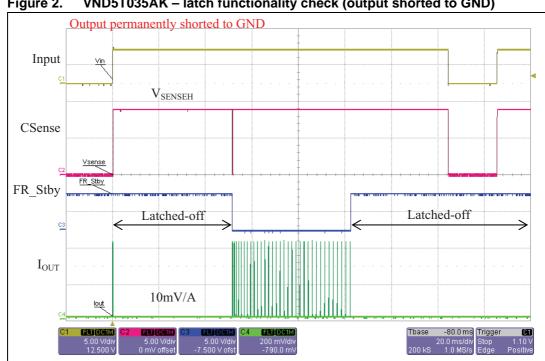

|------------|-----------------------------------------------------------------------------------------------|------|

| Figure 2.  | VND5T035AK – latch functionality check (output shorted to GND)                                | 9    |

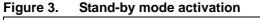

| Figure 3.  | Stand-by mode activation                                                                      | 10   |

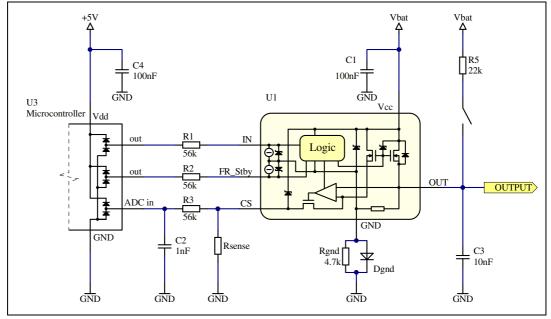

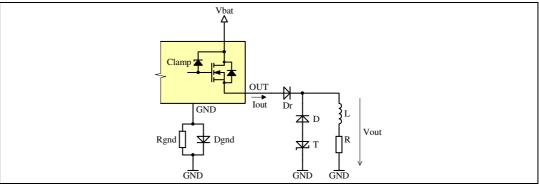

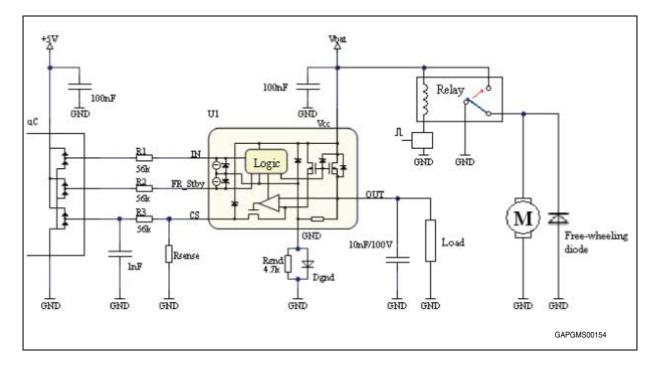

| Figure 4.  | Monolithic analogue HSD-application schematic                                                 |      |

| Figure 5.  | Hybrid analogue HSD-application schematic.                                                    |      |

| Figure 6.  | Voltage levels during reverse battery using diode-resistor protection                         |      |

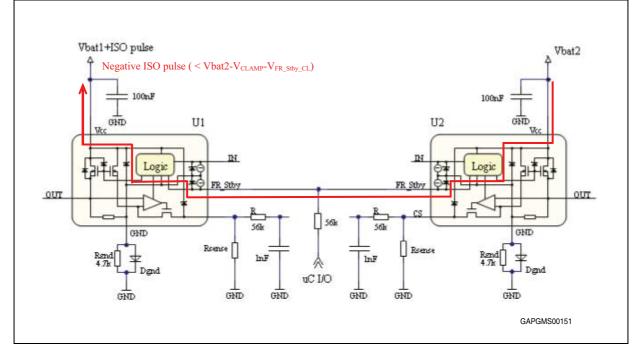

| Figure 7.  | Positive ISO pulse                                                                            |      |

| Figure 8.  | Negative ISO pulse                                                                            |      |

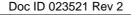

| Figure 9.  | Negative GND shift (T <sub>DEMAG</sub> > t <sub>stby</sub> )                                  |      |

| Figure 10. | Measurement example – $T_{DEMAG} > t_{stby}$ ( $R_{GND} = 6.8$ k, relay 880 mH/280 $\Omega$ ) | . 16 |

| Figure 11. | Voltage levels during reverse battery – MOSFET protection                                     |      |

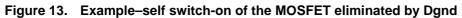

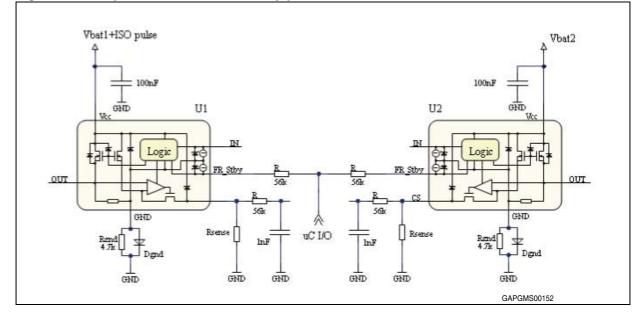

| Figure 12. | Hybrid HSD – reverse battery protection with self switch-on of the MOSFET                     |      |

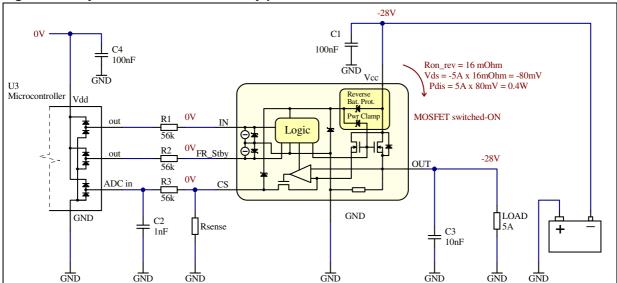

| Figure 13. | Example-self switch-on of the MOSFET eliminated by Dgnd                                       |      |

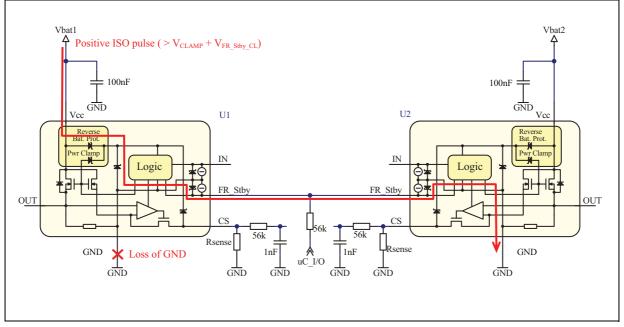

| Figure 14. | ISO-pulse transfer to I/O pin                                                                 |      |

| Figure 15. | 24 V high-side driver with analogue current sense-block diagram.                              |      |

| Figure 16. | Analog current sense simplified block diagram                                                 |      |

| Figure 17. | $V_{\text{SENSE}}$ vs I <sub>OUT</sub>                                                        |      |

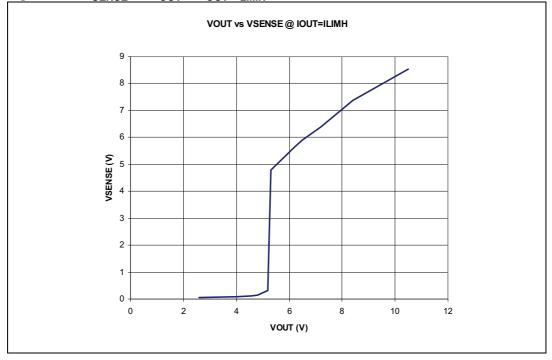

| Figure 18. | V <sub>SENSE</sub> vs V <sub>OUT</sub> @ I <sub>OUT</sub> =I <sub>LIMH</sub>                  | 21   |

| Figure 19. | Example–overload (350 m $\Omega$ to GND)                                                      |      |

| Figure 20. | Example-bard short to GND.                                                                    |      |

| Figure 20. | Current sense resistor                                                                        |      |

| -          |                                                                                               |      |

| Figure 22. | Switchable current sense resistor–example                                                     |      |

| Figure 23. |                                                                                               |      |

| Figure 24. | Analogue HSD-open load detection in off-state                                                 |      |

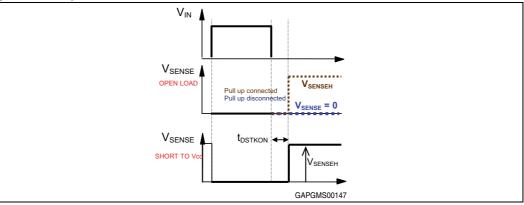

| Figure 25. | Open load/short to Vcc condition                                                              |      |

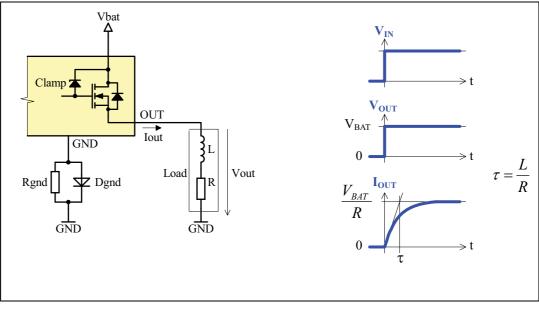

| Figure 26. | Inductive load – HSD turn-on phase.                                                           |      |

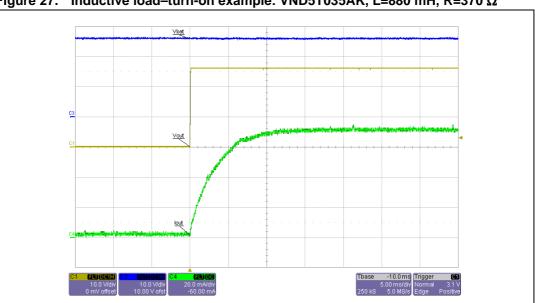

| Figure 27. | Inductive load-turn-on example: VND5T035AK, L=880 mH, R=370 $\Omega$                          |      |

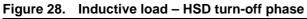

| Figure 28. | Inductive load – HSD turn-off phase.                                                          |      |

| Figure 29. | Inductive load - Turn off example: VND5T035AK, L=880 mH, R=370 $\Omega$                       |      |

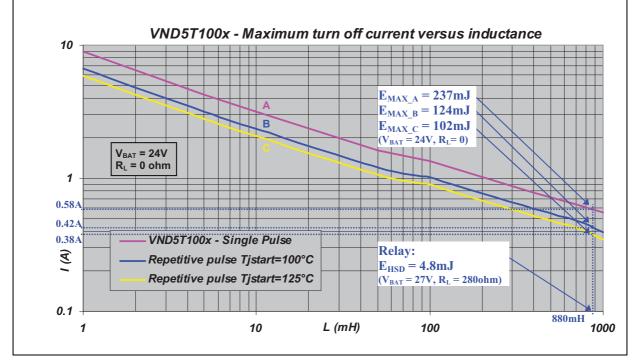

| Figure 30. | Maximum turn-off current versus inductance–VND5T100AJ datasheet                               |      |

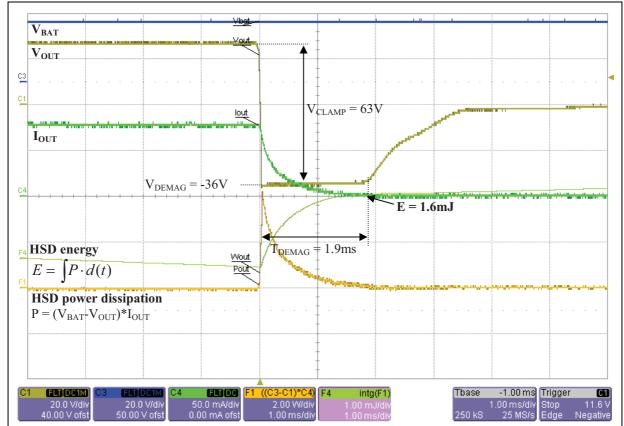

| Figure 31. | Demagnetization energy measurement–VND5T100AJ, relay 880 mH.                                  |      |

| Figure 32. | External clamping – transil and diode                                                         |      |

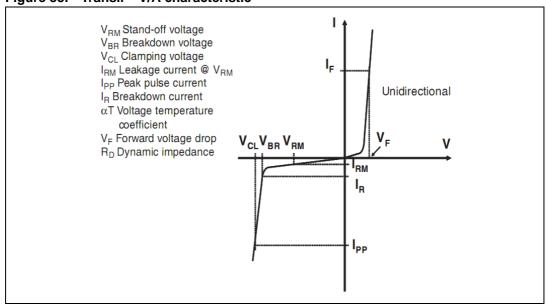

| Figure 33. | Transil – V/A characteristic.                                                                 |      |

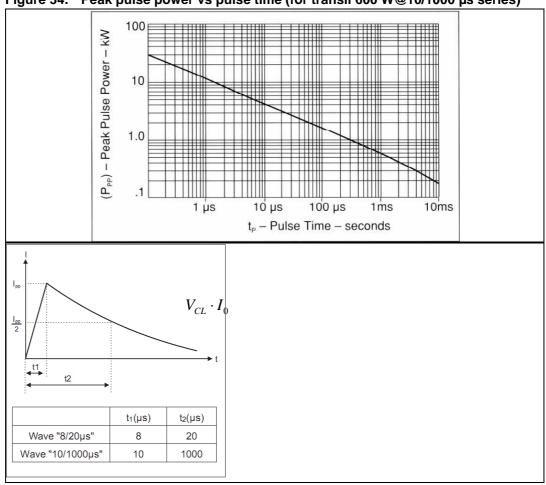

| Figure 34. | Peak pulse power vs pulse time (for transil 600 W@10/1000 µs series)                          |      |

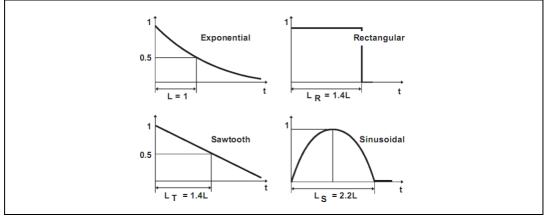

| Figure 35. | Equivalent pulses giving the same power dissipation.                                          |      |

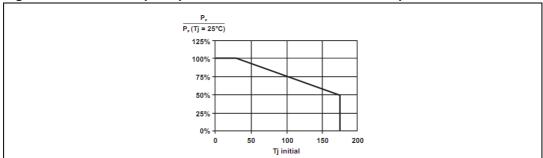

| Figure 36. | Maximum peak power as function of the initial temperature of the transil                      |      |

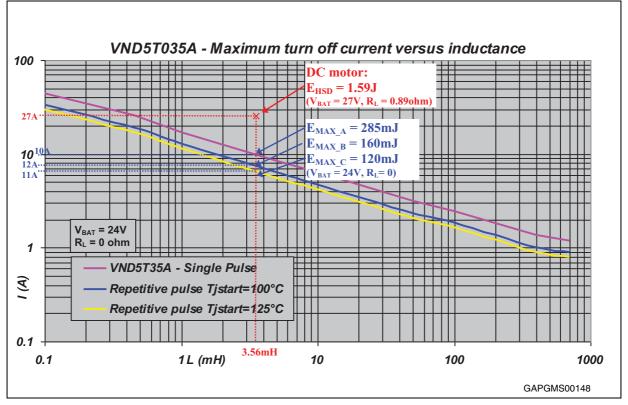

| Figure 37. | Maximum turn-off current versus inductance – VND5T035AJ datasheet                             |      |

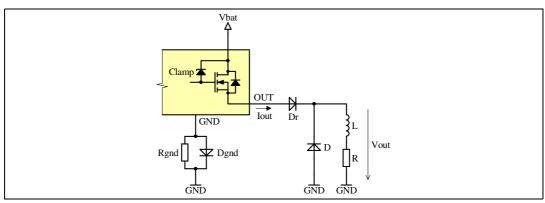

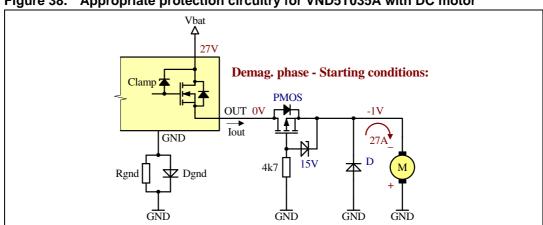

| Figure 38. | Appropriate protection circuitry for VND5T035A with DC motor                                  |      |

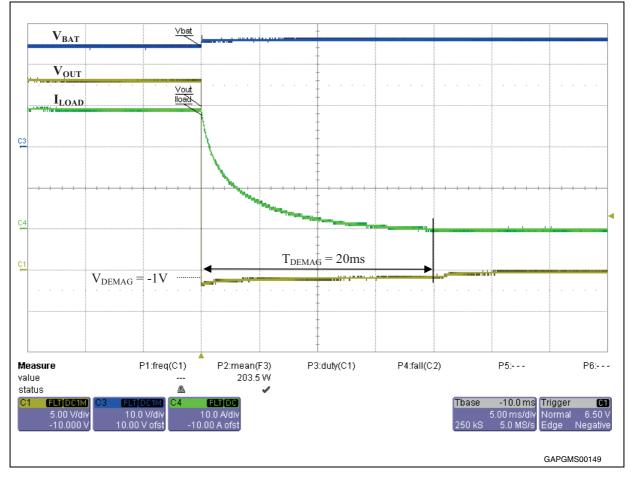

| Figure 39. | Single demagnetization in stall condition – VND5T035AK, Freewheeling diode                    |      |

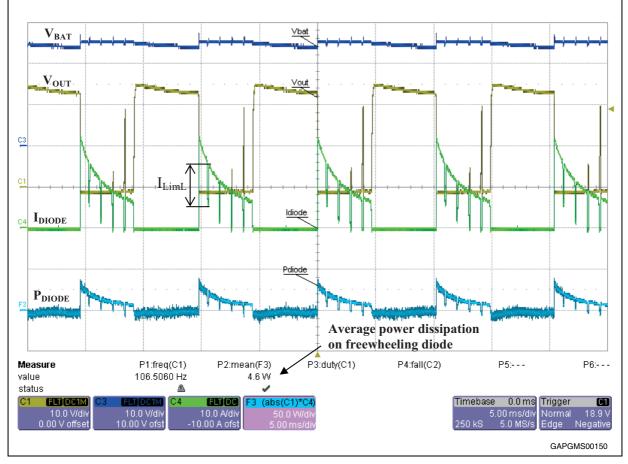

| Figure 40. | Repetitive demagnetization in stall condition – VND5T035AK, Freewheeling diode                |      |

| Figure 41. | Direct connection of FR_Stby pins (not recommended)                                           |      |

| Figure 42. | Proper connection of FR_Stby pins                                                             |      |

| Figure 43. | Direct connection of FR_Stby pins (not recommended)                                           |      |

| Figure 44. | Direct connection of FR_Stby pins (not recommended)                                           |      |

| Figure 45. | Direct connection of CS pins (not recommended)                                                | 65   |

| Figure 46. | Robust solution for paralleling CS pins                                                       |      |

| Figure 47. | Direct connection of CS pins (not recommended)                                                | 67   |

| Figure 48. | Direct connection of CS pins (not recommended)                                                | 68   |

| Figure 49.    | Block diagram of the L99PD08/AMICO                                                                   |

|---------------|------------------------------------------------------------------------------------------------------|

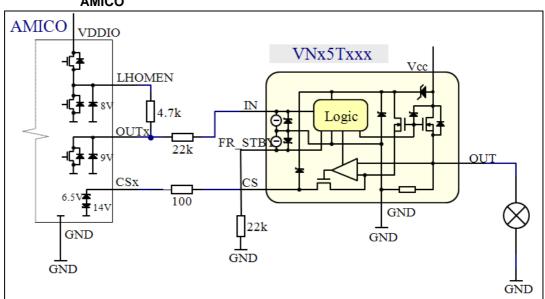

| Figure 50.    | Application example of AMICO with M0-5T HSDs                                                         |

| Figure 51.    | Generation of PWM signals by the AMICO78                                                             |

| Figure 52.    | Behaviour of the LHOMEN signal78                                                                     |

| Figure 53.    | Control of the HSDs' inputs                                                                          |

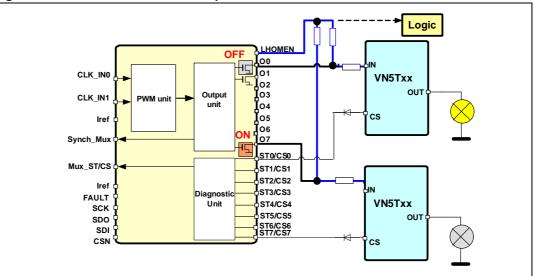

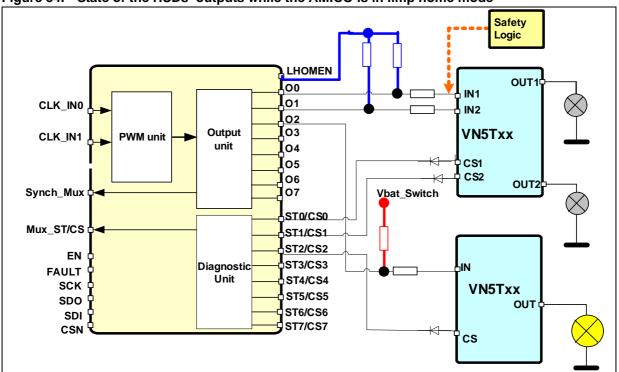

| Figure 54.    | State of the HSDs' outputs while the AMICO is in limp home mode                                      |

| Figure 55.    | Simplified diagram on the on-board diagnostic                                                        |

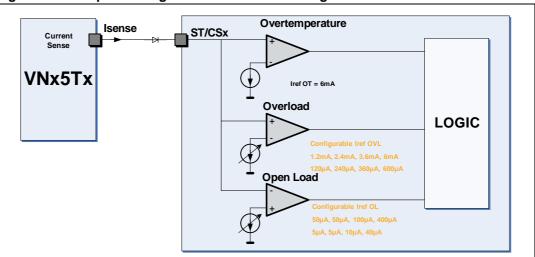

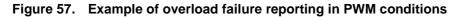

| Figure 56.    | Example of overload failure reporting in PWM operation                                               |

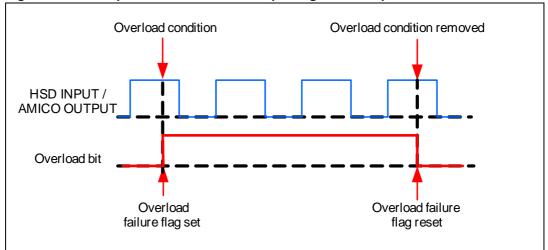

| Figure 57.    | Example of overload failure reporting in PWM conditions                                              |

| Figure 58.    | Inrush blanking time                                                                                 |

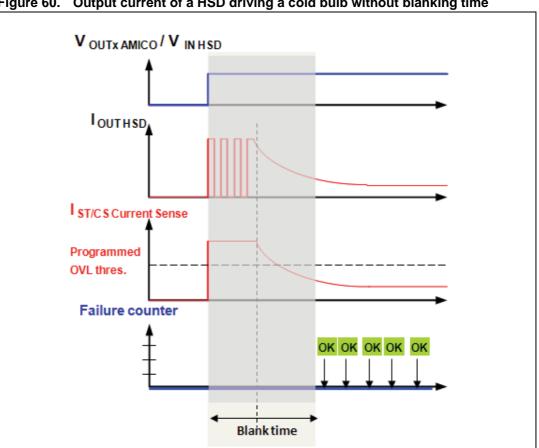

| Figure 59.    | HSD output current if the duration of the power limitation is longer than the inrush blanking        |

| rigule 59.    | time                                                                                                 |

| <b>E</b> :    |                                                                                                      |

| Figure 60.    | Output current of a HSD driving a cold bulb without blanking time                                    |

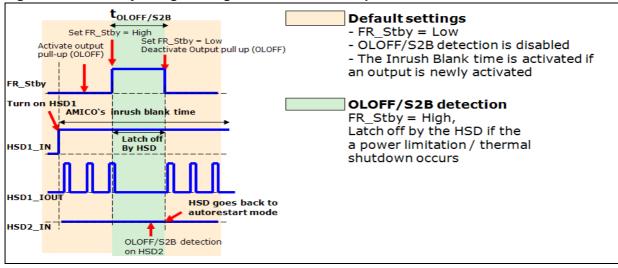

| Figure 61.    | Dynamic control of the FR_Stby pin                                                                   |

| Figure 62.    | No new activation while Fr_Stby is High90                                                            |

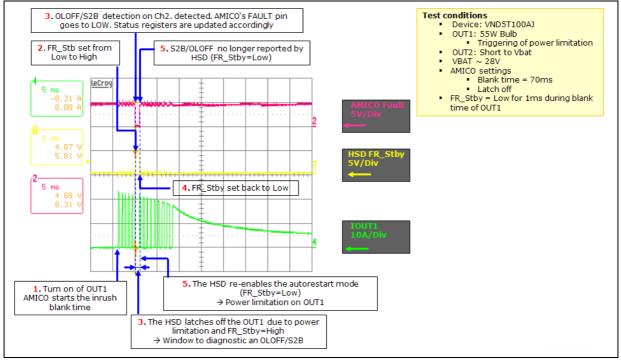

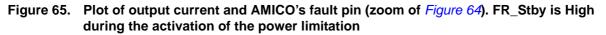

| Figure 63.    | FR_Stby is High during the activation of the power limitation                                        |

| Figure 64.    | Plot of output current and AMICO's fault pin. FR_Stby is high during the activation of the pow       |

|               | er limitation                                                                                        |

| Figure 65.    | Plot of output current and AMICO's fault pin (zoom of <i>Figure 64</i> ). FR_Stby is High during the |

| -             | activation of the power limitation                                                                   |

| Figure 66.    | Principle of the direct current sense reading                                                        |

| Figure 67.    | Behaviour of the Synch_Mux signal94                                                                  |

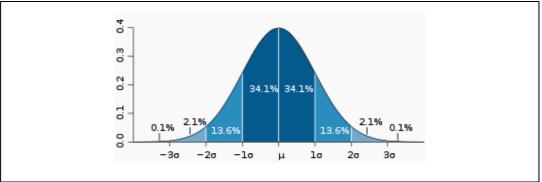

| Figure 68.    | Probability density function of a gaussian distribution                                              |

| Figure 69.    | Recommendations for series resistors between the AMICO and the microcontroller 99                    |

| Figure 70.    | Distortion of the SPI signal by a too high series resistor                                           |

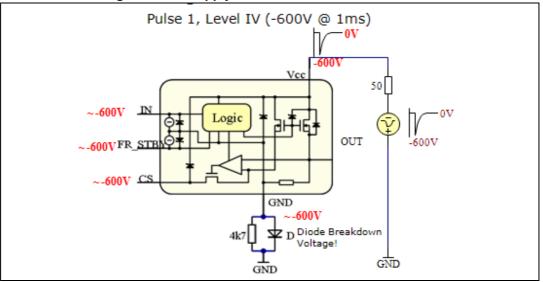

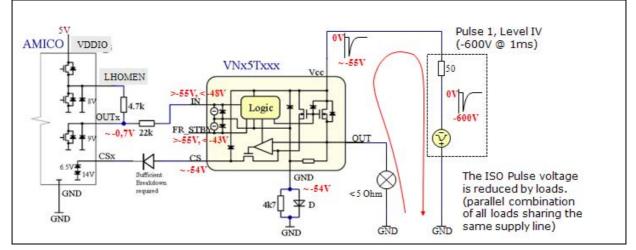

| Figure 71.    | Effect of an ISO pulse 1 on Vcc, if no load is connected to any HSD sharing the same supply          |

| rigato / I.   |                                                                                                      |

| Figure 72.    | Effect of an ISO pulse 1 on Vcc with at least one connected load to one of the outputs of the        |

| riguie 72.    | HSDs, sharing the same supply line                                                                   |

| Figure 73.    | Positive ISO pulses on the supply of monolithic devices are not transferred to IN, FR_Stby           |

| Figure 75.    |                                                                                                      |

| <b>-</b> :    | and CS pins                                                                                          |

| Figure 74.    | Recommended external components between a monolithic HSD and the AMICO 102                           |

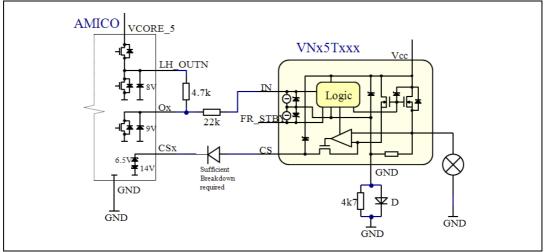

| Figure 75.    | Negative ISO pulses on the supply of the hybrid HSD are not transferred to IN, FR_Stby or            |

|               | CS pins                                                                                              |

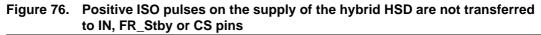

| Figure 76.    | Positive ISO pulses on the supply of the hybrid HSD are not transferred to IN, FR_Stby or CS         |

|               | pins                                                                                                 |

| Figure 77.    | Recommended external components between a hybrid HSD and an AMICO 104                                |

| Figure 78.    | Verification of the correct activation of a monolithic HSD, despite the voltage drop across the      |

| -             | series resistor                                                                                      |

| Figure 79.    | Recommended external components between a monolithic HSD and the AMICO to with                       |

| 0             | stand a reverse battery condition                                                                    |

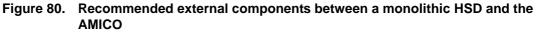

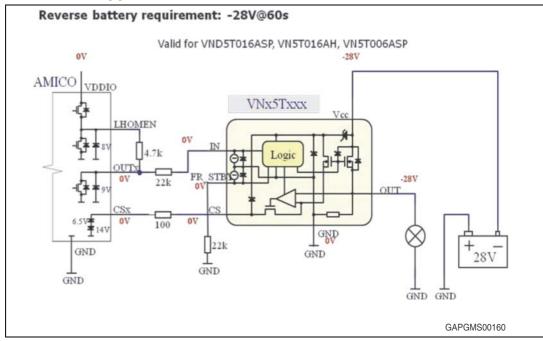

| Figure 80.    | Recommended external components between a monolithic HSD and the AMICO 107                           |

| Figure 81.    | Recommendations for pull-up resistors, pull-down resistors and decoupling capacitors . 108           |

| i igui c o i. | recommendations for pair up resistors, pair down resistors and decoupling capacitors . Too           |

# 1 New features of 24 V drivers

In addition to the established family of M0-5*Enhanced* drivers, STMicroelectronics has introduced a new set of drivers for 24 V applications. On top of the M0-5*Enhanced* functions and protection mechanisms are the following additional features:

- Programmable Latch-off functionality (INx pin(s) high):

- FR\_Stby pin = low or left open: The drivers behave like M0-5*Enhanced* devices (autorestart in case of overload or thermal shutdown).

- FR\_Stby pin = high: The drivers latch-off in case of overload or thermal shutdown. In order to unlatch the channel(s), a low level pulse on FR\_Stby pin is required for minimum duration of t<sub>RESET</sub>.

- Programmable stand-by mode (INx pins(s) low):

- FR\_Stby pin=low or left open:

- A permanent low level on both the INx and fault reset standby pin disables all outputs and sets the devices in standby mode (open load diagnostic in off-state is disabled).

- FR\_Stby pin=high: The drivers behave like M0-5*Enhanced* devices (open load diagnostic in off-state enabled).

# 1.1 **Programmable latch-off functionality**

The latch-off functionality is available when the FR\_Stby pin (logic input) is set high. This pin is common for all device channels.

In case of an overload, the related channel is automatically latched-off at the first intervention of either power limitation or thermal shutdown. The latch condition is indicated by  $V_{\text{SENSEH}}$  level on the related current sense pin (only if the input pin is set high).

All latched channels can be restarted by setting the FR\_Stby pin low for a minimum time of  $t_{RESET}$  (> 24 µs).

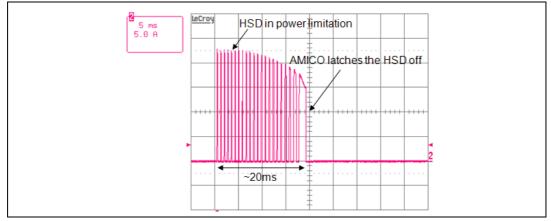

A graphical explanation of the latch-off functionality can be seen in *Figure 1* and *Figure 2*.

5

Latch functionality - behavior in overload condition Figure 1.

VND5T035AK - latch functionality check (output shorted to GND) Figure 2.

Doc ID 023521 Rev 2

The Stand-by mode is available when the FR\_Stby pin and all INx pins are set low (or left open). In this condition, the supply current drops down to 2  $\mu$ A (typically) with a typical delay of t<sub>stby</sub> = 500  $\mu$ s (see *Figure 3*). The open load diagnostic in off-state is disabled since the FR\_Stby pin is pulled low (or left open).

The device exits Stand-by mode when any FR\_Stby pin or INx pin is set high. When the FR\_Stby pin is high, the open load diagnostic in off-state is available. Thus the CS pin(s) provides  $V_{SENSEH}$  in case of  $V_{OUT} > V_{OL}$  (same behaviour as M0-5*Enhanced* devices).

| Conditions                            | Fault reset<br>standby | Input | Output   | Sense                       |

|---------------------------------------|------------------------|-------|----------|-----------------------------|

| Standby                               | L                      | L     | L        | 0                           |

| Normal aparation                      | Х                      | L     | L        | 0                           |

| Normal operation                      | Х                      | Н     | Н        | Nominal                     |

| Quarland                              | Х                      | L     | L        | 0                           |

| Overload                              | Х                      | Н     | Н        | >Nominal                    |

|                                       | Х                      | L     | L        | 0                           |

| Overtemperature/<br>short to ground   | L                      | Н     | Cycling  | V <sub>SENSEH</sub>         |

| Short to ground                       | Н                      | Н     | Latched  | V <sub>SENSEH</sub>         |

| Undervoltage                          | Х                      | Х     | L        | 0                           |

|                                       | L                      | L     | Н        | 0                           |

| Short to V <sub>BAT</sub>             | Н                      | L     | н        | V <sub>SENSEH</sub>         |

|                                       | Х                      | Н     | н        | <nominal< td=""></nominal<> |

| 0 1 1 1 1 1 1                         | L                      | L     | Н        | 0                           |

| Open load off-state<br>(with pull-up) | Н                      | L     | н        | V <sub>SENSEH</sub>         |

| (with pull-up)                        | Х                      | Н     | н        | 0                           |

| Negative output voltage clamp         | Х                      | L     | Negative | 0                           |

Table 1.Diagnostic truth table

# 2 General items

# 2.1 Application schematic (monolithic and hybrid analogue HSD)

In comparison with the established M0-5*Enhanced* drivers (12 V), there is a new FR\_Stby pin (there is no CS\_DIS pin) used for fault reset and mode selection (autorestart/latch-off, standby/open load in off-state).

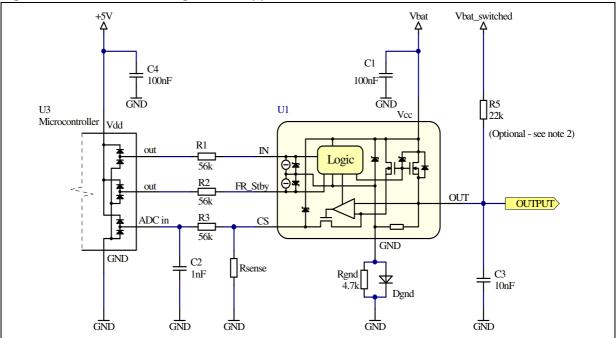

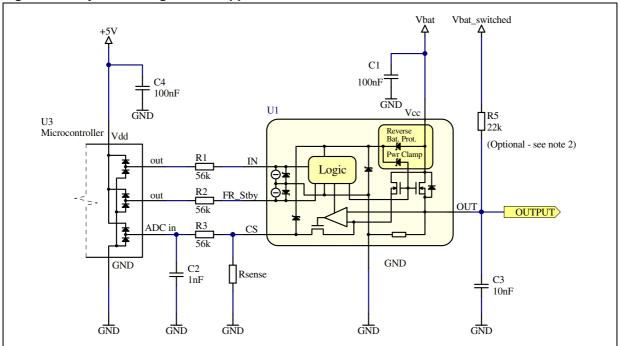

Figure 4. Monolithic analogue HSD–application schematic

Figure 5. Hybrid analogue HSD-application schematic

- If latch functionality or open load detection in off-state is not required, the FR\_Stby pin should be left open or connected to ground through a resistor (~56 k). Direct connection to ground is not safe (ISO pulses clamped through FR\_Stby pin can damage the device).

ISO pulses referred to ISO 7637 2: 2004(E).

- ISO pulses referred to ISO 7637-2: 2004(E)

- 2. Pull-up R5 is optional (open load detection in off-state)

# 2.2 Reverse battery protection

#### 2.2.1 Reverse battery protection of monolithic HSDs

The reverse battery protection is applied to the GND terminal of the driver. There are several possible solutions: diode, resistor plus diode or MOSFET circuitry. As there is a relatively low current in the GND path, no high power components are needed. However, this protection circuit still must be able to handle the clamped ISO pulse current as well as the ISO pulse voltage. We also have to consider the fact that this simple "ground" circuitry doesn't provide any protection of the connected load. If a reverse battery condition occurs, the load is supplied in reverse polarity through the internal body diode of the HSD and the power dissipation on the HSD can become critical (depending on connected load and thermal connection of the HSD). The typical voltage drop on the internal body diode is about 0.7 V. The resulting power dissipation  $P_D = 0.7 I_{LOAD}$  [W].

#### Reverse battery protection using diode plus resistor

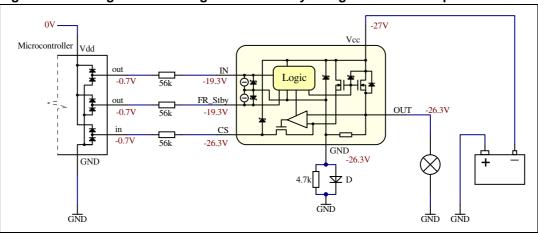

Figure 6. Voltage levels during reverse battery using diode-resistor protection

A diode at the GND terminal prevents a short circuit through the internal substrate diode of the HSD during a reverse battery condition.

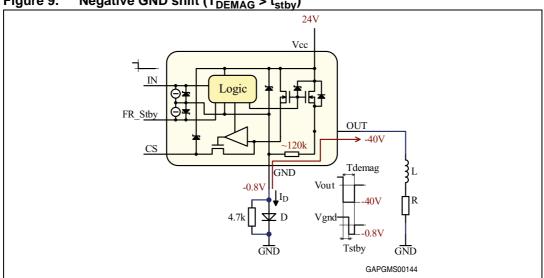

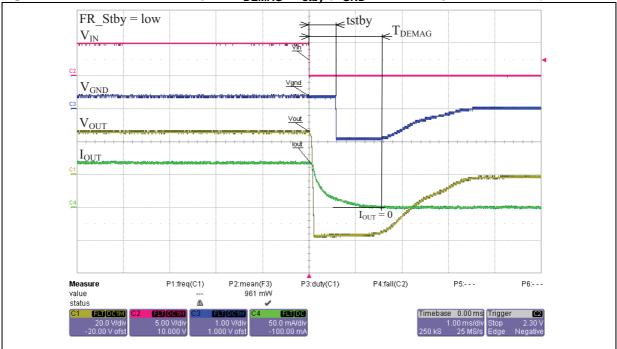

A resistor (max. 4.7 kΩ) connected in parallel to the diode is recommended (not mandatory) in case the device drives a high inductance load with a demagnetization time longer than t<sub>stby</sub>. The purpose of this resistor is to suppress a negative voltage on the GND pin during standby mode if the demagnetization phase is still ongoing. Without this resistor, the low supply current in standby mode (2 µA typically) allows the GND pin to be pulled negative by the demagnetization voltage on the output (~ -40 V) via an internal pull-down resistor (~120 kΩ, not specified) on the output (see *Figure 9*, *Figure 10*). If the negative ground shift exceeds the input high level threshold (V<sub>IH</sub> = 2,1 V min.), the device leaves standby mode and tends to turn on. The GND pin is immediately pulled high (~600 mV) by the increased supply current so that standby mode is activated again after t<sub>stby</sub> delay. As a result, we may see short negative peaks on the GND pin with a period of t<sub>stby</sub> during the whole demagnetization phase. These peaks are not long enough to activate the HSD output, which means the device works safely even without the GND resistor. However, this resistor is still recommended in order to suppress the described parasitic oscillations (if T<sub>DEMAG</sub> > t<sub>stby</sub>).

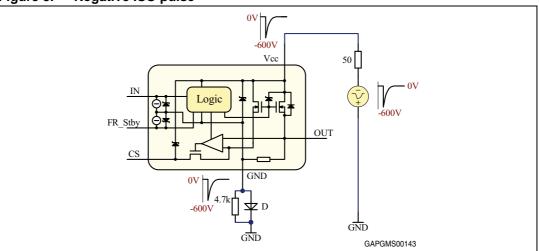

This ground network can be safely shared amongst several different HSDs. The presence of the ground network produces a shift (~ 600 mV) in the input threshold. This shift does not vary if more than one HSD share the same diode/resistor. A diode at the GND terminal allows the High-Side Driver to clamp positive ISO pulses above 64 V (the typical clamping voltage of the HSD). Negative ISO pulses still pass GND and logic terminals. The diode should withstand clamped ISO currents in case of positive ISO pulses and reverse voltages in case of negative ISO pulses.

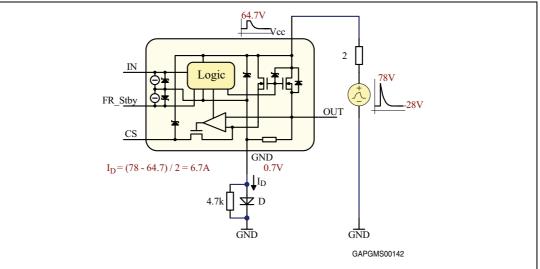

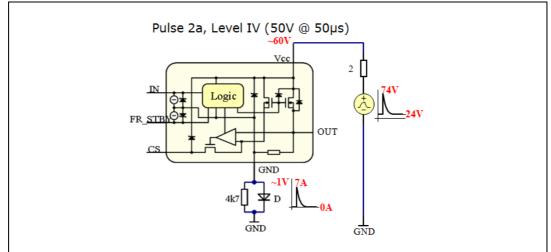

Dimensioning of the diode<sup>(a)</sup> :

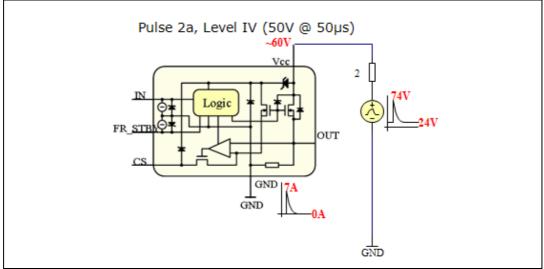

The most severe positive ISO pulse to consider is test pulse 2 at level IV (50 V@50  $\mu$ s). This voltage is considered on top of the nominal supply voltage of 28 V – so the total voltage is 78 V. The VIPower has a clamping voltage of typ. 64 V (min. 58 V/max. 70 V). For a typical device, the remaining voltage is 78 V - 64 V - 0.7 V = 13.3 V. The ISO pulse generator interior resistance is given with 2  $\Omega$ . Hence, the resulting peak current through the diode is 6.7 A for a duration of 50  $\mu$ s.

Figure 7. Positive ISO pulse

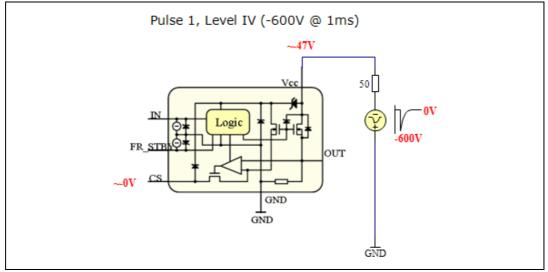

The most severe negative ISO pulse we have to consider is test pulse 1 at level IV (-600 V@1 ms). This pulse is directly transferred to the GND pin via the internal clamping. Hence, the maximum peak reverse voltage of the diode should be at least 600 V.

Note: The diode works in avalanche mode if the pulse level is above the rated reverse voltage.

a. Result: Max. peak forward current: 6.7 A @ 50 µs Max. reverse voltage: -600 V

Figure 8. Negative ISO pulse

- Note: As seen from the above explanation, the HSD with a diode protection at the GND pin doesn't clamp negative ISO pulses on the supply line. Therefore an appropriate serial protection resistor should be used between the  $\mu$ C and HSD. The resistor value should be calculated according to the maximum injected current to the I/O pin of the used microcontroller.

- Note: Diode parameters can be lower if an external clamping circuitry is used (e.g., the HSD module is supplied from a protected power supply line).

Dimensioning of the resistor <sup>(b)</sup>:

The GND resistor is recommended in case of a high inductivity load. To determine whether the resistor is needed, we need to know the demagnetization time ( $T_{DEMAG}$ ). The resistor is recommended if  $T_{DEMAG}$  is higher than the standby delay time ( $t_{stbv}$ ).

A minimum  $t_{\text{stby}}$  value of 120  $\mu s$  (as specified in the datasheet) is considered in this comparison.

Resistance:4.7 k (or lower)

Voltage capability:min. 600 V (ISO pulse 1 at level IV)

Power dissipation (reverse batt.):min. 167 mW (4.7 k) => Package 1206

b. Summary - dimensioning of the resistor:

Resistor recommended if:  $T_{DEMAG} > t_{stby}$

Figure 9. Negative GND shift (T<sub>DEMAG</sub> > t<sub>stby</sub>)

T<sub>DEMAG</sub> can be determined either by measurement (Figure 10) or calculation using Equation 1 and Equation 2.

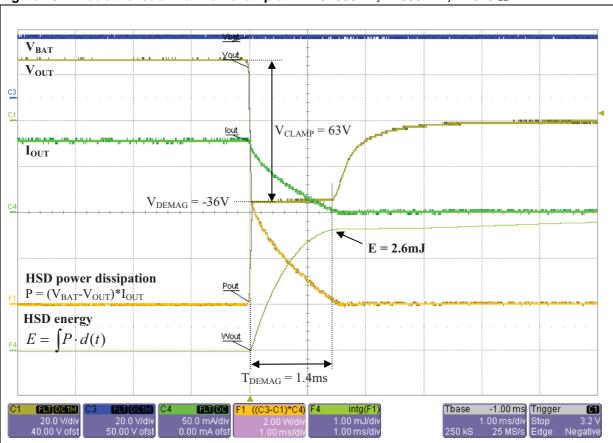

Figure 10. Measurement example –  $T_{DEMAG} > t_{stby}$  (R<sub>GND</sub> = 6.8 k, relay 880 mH/280  $\Omega$ )

The value of the resistor should be low enough to ensure that the negative voltage at the GND pin is suppressed as much as necessary to keep the device off. This means the  $\rm V_{GND}$ should be kept above -2.1 V (assuming  $V_{IN}$  = 0 V, minimum input high level voltage  $V_{IH}$  = 2.1 V). Assuming the value of the internal pull-down at the output (R<sub>OUT</sub>) of 120 k $\Omega$ and neglecting the device standby current, the maximum value of the GND resistor is given by a simple resistor divider calculation:

Doc ID 023521 Rev 2

$$R_{GND} < R_{OUT} \cdot \frac{V_{GND}}{V_{DEMAG} - V_{GND}} = 120k \cdot \frac{-2.1V}{-40V + 2.1V} = 6.6k$$

$\rightarrow$  considering a certain safety margin, a maximum 4.7 k $\Omega$  value is recommended

The minimum resistor value is determined by the maximum DC reverse ground pin current of the HSD in a reverse battery condition:

$$R_{GND} \ge \frac{V_{BAT(reverse)}}{I_{GND}(reverse)_{max}} = \frac{28V}{200mA} = 140ohm$$

In order to keep the power dissipation on the resistor during a reverse battery condition as low as possible, it is better to select the resistor value close to the maximum value (4.7 k $\Omega$ ).

$$P_D = \frac{V_{BAT(reverse)}^2}{R_{GND}} = \frac{28V^2}{4.7k} = 0.167W$$

$\rightarrow$  Package 1206

(Power rating of 1206 is 0.25 W@70 °C)

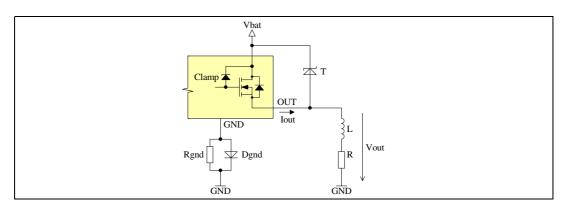

#### Reverse battery protection using MOSFET

#### Figure 11. Voltage levels during reverse battery – MOSFET protection

The HSD is protected by a MOSFET which is switched-off during a reverse battery condition. This MOSFET circuitry also provides full ISO pulse clamping at supply line and causes no ground level shift. A capacitor between gate and source keeps the gate charged even during negative ISO pulses. The time constant given by RC values should be longer than 1 ms (duration of the negative ISO7637 pulse 1).

| Protection type<br>(monolithic HSD) | +                                                                                               | -                                                                                                                                                                                                                                                                        |

|-------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1) Diode                            | Fixed voltage drop.<br>Positive ISO-pulse clamping<br>(>64 V).<br>Any type of load.             | Negative ISO-pulse transfer to<br>input and diagnostics pin (serial<br>protection resistors necessary).<br>Possibility of parasitic<br>oscillations on the GND pin<br>during turn-off of the high<br>inductivity load<br>(when T <sub>DEMAG</sub> > t <sub>stby</sub> ). |

| 2) Resistor and Diode               | Fixed voltage drop<br>Positive ISO-pulse clamping<br>(>64V).<br>Any type of load.               | Negative ISO-pulse transfer to<br>input and diagnostics pin (serial<br>protection resistors necessary).                                                                                                                                                                  |

| 3) MOSFET                           | Any type of load.<br>No voltage drop.<br>No ISO-pulse transfer to input<br>and diagnostics pin. | Higher cost (more external components needed).                                                                                                                                                                                                                           |

Table 2. Reverse battery protection (of monolithic HSDs only) – comparison

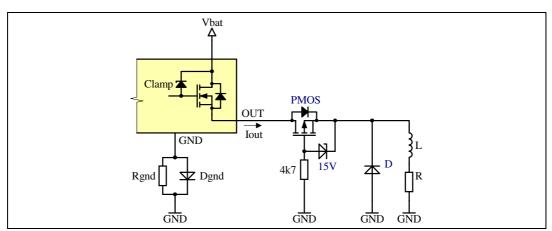

#### 2.2.2 Reverse battery protection of hybrid HSDs

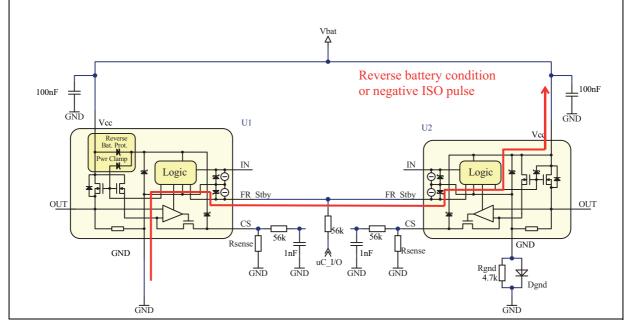

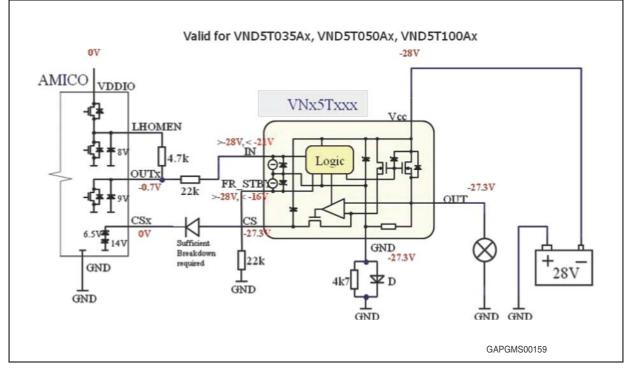

In contrast to monolithic devices, all hybrid VIPower HSDs do not need any external components to protect the internal logic in case of a reverse battery condition. The protection is provided by internal structures (see "Reverse Battery Protection" in *Figure 12*).

Also, due to the fact that the output MOSFET automatically turns on in reverse battery mode and thus provides the same low ohmic path as in regular operation conditions, no additional power dissipation has to be considered.

Furthermore, if for example, a diode is connected to the GND of a hybrid HSD the output MOSFET is unable to turn on and thus the unique feature of the driver is disabled (see *Figure 13*).

Figure 12. Hybrid HSD – reverse battery protection with self switch-on of the MOSFET

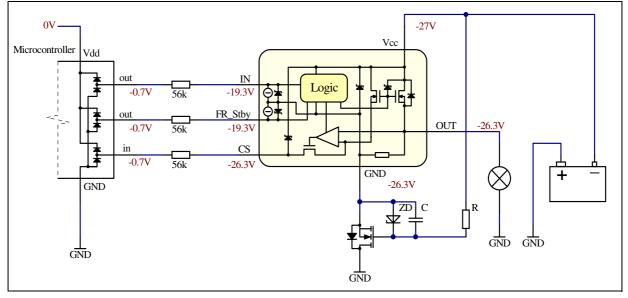

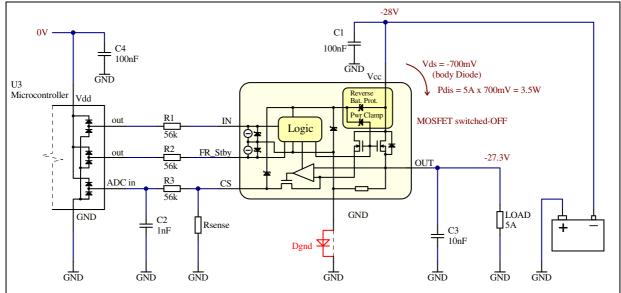

# 2.3 Microcontroller protection

If ISO pulses or a reverse battery condition appears, the HSD control pins can be pulled to dangerous voltage levels due to the internal HSD structure and ground protection network (as seen in *Section 2.2: Reverse battery protection*).

Figure 14. ISO-pulse transfer to I/O pin

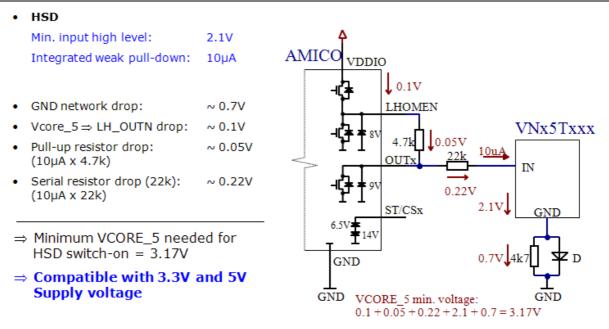

Therefore, each microcontroller I/O pin connected to a HSD must be protected by a serial resistor to limit the injected current. The value of  $R_{PROT}$  must be high enough to ensure that the injected current is always below the latch-up limit of the microcontroller I/O. We should also consider the voltage drop on  $R_{PROT}$  because the current required by the HSD input is typically 10  $\mu$ A. The following condition must be fulfilled:

$$\frac{V_{PEAK}}{I_{(\mu C)LATCHUP}} \le R_{PROT} \le \frac{V_{OH} - (V_{IH} + V_{GND})}{I_{IH}}$$

Example:

$$\frac{600V}{20mA} \le R_{PROT} \le \frac{4.5V - (2.1V + 0.6V)}{10\mu A}$$

$$30k\Omega \le R_{PROT} \le 180k\Omega$$

Recommended R<sub>PROT</sub> value is 56 k $\Omega$  (safe value for most automotive microcontrollers).

# 3 Analogue current sense

# 3.1 Introduction

With the introduction of the VIPower M0-5 technology, important improvements have been introduced in the analog current sense operation.

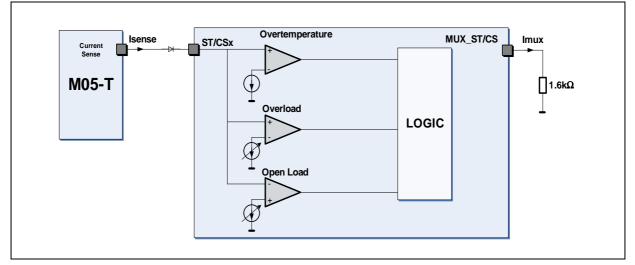

The block diagram of a M0-5 high-side driver with analog current sense is shown in *Figure 16*.

As with the previous generations, the current sense block has a double function:

- Current mirror of the load current in normal operation, delivering a current proportional to the load current according to a known ratio named K;

- Diagnostics flag in fault conditions, delivering a fixed voltage with a certain current capability in case of overload and open load in off-state condition.

The current delivered by the current sense circuit can be easily converted to a voltage by means of an external sense resistor, thus allowing continuous load monitoring and fault condition detection.

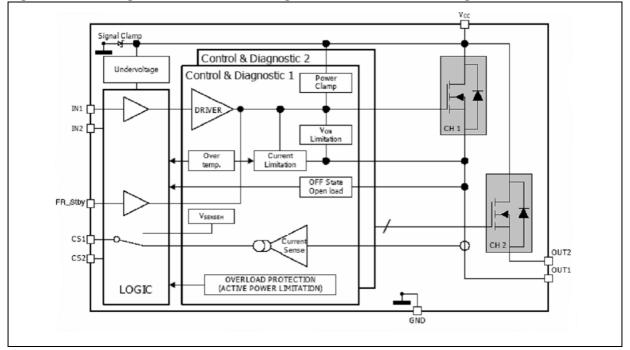

Figure 15. 24 V high-side driver with analogue current sense-block diagram

# 3.2 Principle of operation

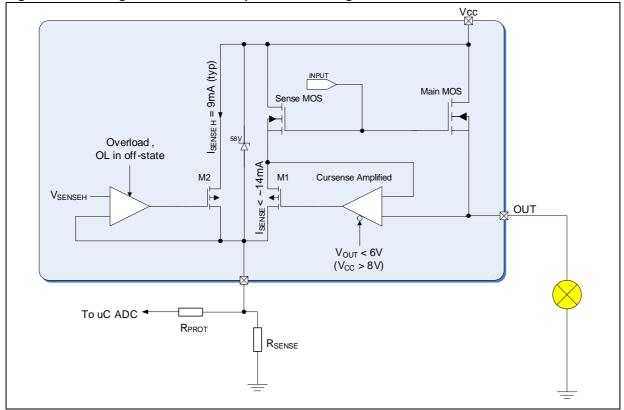

The simplified block diagram of the analog current sense is illustrated in Figure 16.

Figure 16. Analog current sense simplified block diagram

The SenseMOS is a scaled down copy of the MainMOS according to a defined geometric ratio, driven by the same gate control circuit as the MainMOS.

The current flowing through the MainMOS is mirrored by the SenseMOS.

The current delivered by the current sense pin is regulated by the current sense amplifier through the P channel MOSFET M1 so that:

$$V_{DS\_Main} = V_{DS\_Sense} \rightarrow R_{ds\_sense} \cdot I_{sense} = R_{DS\_Main} \cdot I_{out}$$

and consequently

$$V_{sense} = R_{sense} \cdot I_{out} / K$$

where

$$K \propto R_{ds \_sense} / R_{DS \_Main}$$

encloses the geometric ratio, the current sense amplifier offset and various process parameter spreads.

Care must be taken in order to ensure the  $I_{sense}$  is proportional to  $I_{OUT}$ . Indeed, the maximum drop across the  $R_{SENSE}$  is internally limited to approx. 8.5 V as specified in the

Doc ID 023521 Rev 2

datasheet by the parameter V<sub>SENSE</sub> "maximum analog sense output voltage" (5 V minimum @ 8 V< Vcc < 36 V; -40 °C < Tj < 150 °C).

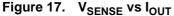

#### Example 1 – V<sub>SENSE</sub> saturation (8.5 V typ.):

VND5T035AK with R<sub>SENSE</sub> selected in order to have V<sub>SENSE</sub>=2 V @ lout = 3 A

Considering (for sake of simplicity) K<sub>2</sub> @ 3 A = 2870 (typical value)  $\rightarrow$  I<sub>SENSE</sub> = ~1 mA  $\rightarrow$  R<sub>SENSE</sub> = ~1.9 k

Assuming a typical V<sub>SENSE</sub> saturation of 8.5 V  $\rightarrow$  maximum I<sub>SENSE</sub> = 4.5 mA to maintain linearity  $\rightarrow$  maximum I<sub>OUT</sub> = 12.8 A.

In other words, with the selected  $R_{SENSE}$  any load current higher than 12.8 A produces the same  $V_{SENSE}$  (see *Figure 17*).

On the other hand, care must be taken to prevent the P channel MOSFET M1 from saturation, causing the  $I_{SENSE}$  to again be disproportional with  $I_{OUT}$ . This normally happens when the maximum current that M1 is able to supply is reached (~14 mA).

This value is consistent with the current sense operating range and current limitation value.

Example 2 – I<sub>SENSE</sub> saturation (~14 mA):

VND5T035AK with R<sub>SENSE</sub> selected in order to have V<sub>SENSE</sub>=1.5 V @ lout = 10 A Considering (for sake of simplicity) K<sub>3</sub> @ 10 A = 2895 (typical value)  $\rightarrow$

$I_{SENSE} = 3.45 \text{ mA} \rightarrow R_{SENSE} = 430 \Omega$

Assuming a typical I<sub>SENSE</sub> saturation of 14 mA and K to remain approx. 2895 for  $I_{OUT} > 10$  A, the maximum load current which can be detected is

$$I_{OUT} = I_{SENSE MAX} \cdot K \cong 40.5A$$

This value is compatible with the typical ILimH.

With the selected  $R_{SENSE}$ , the maximum  $V_{SENSE}$  which can be developed to maintain linearity is approx. 6.02 V.

However, the current sense operation for load current approaching the current limitation is neither guaranteed nor predictable. Indeed, because of the intervention of the current limiter, the output voltage can drop significantly: up to approximately 0 V in the extreme case of a hard short circuit.

As the whole circuit is referred to  $V_{\text{OUT}}$ , ambiguous and unreliable current values can derive from the CS under such conditions.

In order to bring the CS into a well defined state, a dedicated internal circuit shuts down the current sense when  $V_{OUT}$  drops below a certain threshold (6 V typ, see *Figure 18*).

Figure 18. V<sub>SENSE</sub> vs V<sub>OUT</sub> @ I<sub>OUT</sub>=I<sub>LIMH</sub>

Once again, this value is consistent with the current sense operating range and current limitation value.

#### Example: VND5T035AK

At the edge of the current limitation  $I_{OUT}$  =  $I_{LimH}$  = 30 A the maximum drop on the output MOSFET is

$$V_{DS} = R_{DS MAX} \cdot I_{LimH} \cong 70 mOhm \cdot 30A = 2.1V$$

Therefore, at Vcc = 8 V,  $V_{OUT}$  is still sufficient to ensure correct CS function up to the current limited region.

In conclusion, in normal operation the current sense works properly within the described border conditions. For a given device, the  $I_{SENSE}$  is a single value monotonic function of the  $I_{OUT}$  until the maximum  $V_{SENSE}$  (1<sup>st</sup> example) or the current sense saturation (2<sup>nd</sup> example) are reached, i.e. there's no chance of having the same  $I_{SENSE}$  for different  $I_{OUT}$  within the given range.

Doc ID 023521 Rev 2

# 3.3 Indication of power limitation and overtemperature

The principle:

in case of *Power Limitation*/overtemperature, the fault is indicated by the CS pin which is switched to a "current limited" voltage source.

Indeed, with reference to *Figure 16*, whenever a *Power Limitation*/overtemperature condition is reached, the M2 switch on the left side is activated.

The P channel MOSFET M2 is controlled in such a way as to develop 8.5 V typ (V<sub>SENSEH</sub> in the datasheet) across the external sense resistor.

In any case, the current sourced by the CS in this condition is limited to 9 mA typ ( $I_{SENSEH}$  in the datasheet). In order to allow the current sense pin to develop  $V_{SENSEH}$  of 5 V minimum, the sense resistor value must not be below a certain value as shown in the following example:

**Example**: VND5T035AK calculation of minimum sense resistor for  $V_{SENSEH} > 5 V$

Considering a typical I<sub>SENSEH</sub> =9 mA  $\rightarrow$  R<sub>SENSE MIN</sub> = 556  $\Omega$

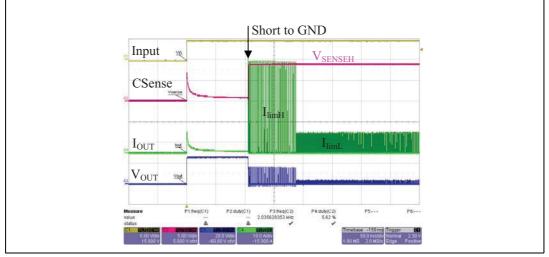

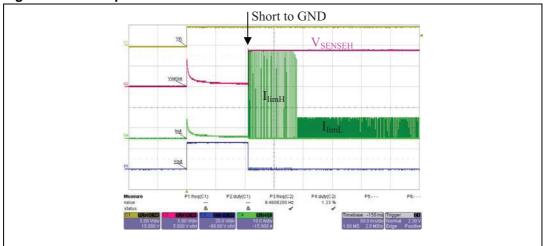

The typical behavior of a 24 V driver in case of overload or hard short circuit is shown in the following figures (FR\_Stby set low = autorestart mode):

Figure 20. Example-hard short to GND

- Diagnostics reacts as soon as *Power Limitation* is reached without waiting for thermal shut down (see *Figure 19*)

- No ambiguity of diagnostics between open load and overload

- Fast and secure detection of short circuit/overload also for intermittent loads (for example turn-indicator lamps or loads driven with PWM)

- Intermittent short circuit detection covered as well

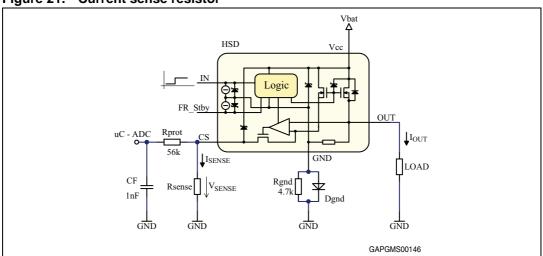

## 3.4 Current sense resistor calculation

The 24 V HSDs integrate a current sense which under normal circumstances provides a voltage across an external shunt resistor ( $R_{SENSE}$ ), which is proportional to the load current with an N/n ratio (so-called K-Factor, specified in the datasheet):

$$V_{SENSE} = R_{SENSE} \cdot I_{SENSE} = R_{SENSE} \frac{I_{OUT}}{K} \quad [V]$$

This allows monitoring of the current which flows through the load and the detection of fault conditions, such as open load, overload, short-circuit to GND leading to a thermal shutdown. In case of a thermal shutdown or *Power Limitation*, the CS pin is switched to a voltage source  $V_{SENSEH}$  ( $V_{SENSEH} = 8.5 V$  typ,  $I_{SENSEHtyp} = 9$  mA) for as long as the device remains in the thermal shutdown (*Power Limitation*) mode.

The current sense voltage is usually connected through a 56 k $\Omega$  protection resistor to the ADC input of the  $\mu$ C. For the V\_{SENSEH} level, the voltage is limited by the  $\mu$ C internal ESD protection (~5.6 V) while the ADC shows maximum value (0xFF in case of 8-bit resolution). The capacitor CF is used to improve the accuracy of the V\_{SENSE} measurement. This capacitor acts as a low impedance voltage source for the ADC input during the sampling phase. Together with a 56 k $\Omega$  serial resistor, it creates a low pass filter (with cutoff frequency of ~3 kHz) for potential HF noise on the CS line (especially if a long wire is routed to the  $\mu$ C). This capacitor should be connected close to the  $\mu$ C.

The R<sub>SENSE</sub> value definition example:

Let's consider the VND5T035AK (35 m $\Omega$ ) with a nominal load current I<sub>N</sub> = 3 A@V<sub>SENSE</sub> = 2 V and typ K<sub>2</sub> = 2870 (datasheet):

$$R_{SENSE} = K \cdot \frac{V_{SENSE}}{I_{OUT}} = 2870 \cdot \frac{2}{3} = 1.9k\Omega$$

# 3.5 Diagnostics

#### 3.5.1 Diagnostics with paralleled loads

A HSD with current sensing allows the detection of individual bulb failures when in a parallel arrangement. However, if we consider the bulb wattage spread, the HSD K-factor tolerance, the variation of bulb currents vs.  $V_{BAT}$  and ADC resolution, it is clear that accurate failure determination can be difficult in some cases. For example, if there are larger and smaller bulbs paralleled, the detection limit for the lowest power bulb is lost in the tolerances.

|                    | r arancing bails over view |                                                       |  |

|--------------------|----------------------------|-------------------------------------------------------|--|

|                    | 5+5 W                      |                                                       |  |

| 21+21 W<br>27+27 W |                            | OK without calibration                                |  |

|                    |                            |                                                       |  |

|                    | 21+21+5 W                  | Calibration and V <sub>BAT</sub> monitoring necessary |  |

Table 3.Paralleling bulbs-overview

In order to achieve a better current sense accuracy one or both of the strategies listed below can be adopted:

- 1. Current sense calibration (K-factor measurement) of each HSD

- 2.  $V_{BAT}$  measurement  $\Rightarrow$  bulb current compensation by appropriate software

## 3.5.2 Diagnostics with different load options

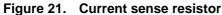

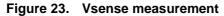

In some cases the requirement profile asks for alternative loads driven with one and the same high-side driver. This can be a bulb lamp with the alternative of an LED (- cluster). In this case the driver:

- Has to handle the high inrush current of the bulb load

- Must provide sufficiently low power dissipation during continuous operation

- Must not indicate an open load in case an LED (-cluster) is applied instead of a bulb.

In the case of different load options (bulb/LED), there is the possibility to use two different (switchable) sense resistors in order to use the current sense band in the appropriate range matching the different load currents.

An example of a current sense resistor switching circuit can be seen in the *Figure 22*. The measured scale can be extended by  $R_{sense1}$  switched in parallel to  $R_{sense2}$  by MOSFET Q1.

#### Figure 22. Switchable current sense resistor-example

### 3.5.3 K-factor calibration method

In order to reduce the Vsense spread, it is possible to reduce the K spread and eliminate the Rsense variation by adding a simple test (calibration test) at the end of the module production line.

How the calibration works:

"To calibrate" on a specific device soldered in a module signifies measuring the K ratio at a given output current by a V<sub>SENSE</sub> reading. Since the relation of  $I_{OUT} = I_{SENSE} \times K$  is known, it is straightforward to calculate the K ratio. However, even if the K ratio measured at a single point eliminates the parametric spread, it doesn't eliminate the V<sub>SENSE</sub> variation due to the K variation produced by the output current variation.

This variation can be eliminated according to the following considerations:

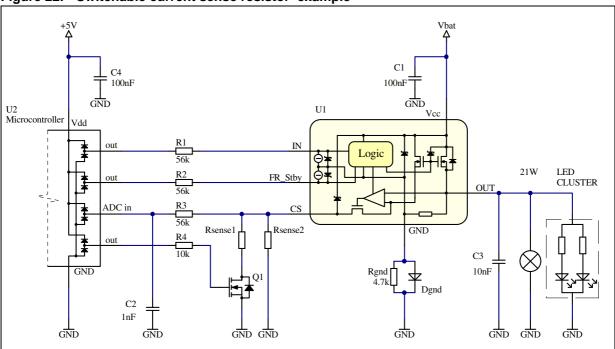

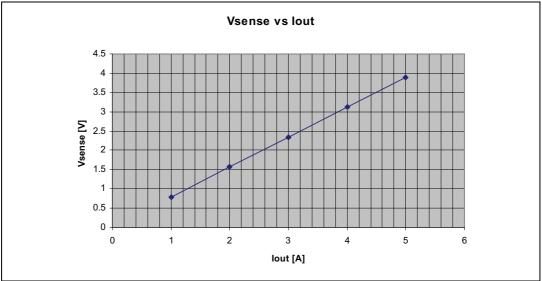

*Table 4* and *Figure 23* show a V<sub>SENSE</sub> measurement on a random VND5T035AK with  $R_{SENSE} = 2.2 \text{ k}\Omega$ .

| lout[A] | Vsense[V] |

|---------|-----------|

| 1       | 0.783     |

| 2       | 1.563     |

| 3       | 2.344     |

| 4       | 3.115     |

| 5       | 3.898     |

Table 4.Vsense measurement

The trend is almost linear in the application range so we can approximate the Vsense trend with the following equation:

$Vsense=m^*lout+a$  (1)

Where *m* [ohm] is the rectangular coefficient and *a* is a constant.

The output current can be calculated by inverting this equation:

lout = M\*Vsense + b

(2)

Instead of  $I_{OUT} = I_{SENSE} \times K$ , once M [S] and b are known, it is possible to evaluate the  $I_{OUT}$  with a high accuracy, leaving only the spread due to temperature variation.

The current sense fluctuation due to temperature variation is expressed in the datasheet with the parameter dK/K.

How to calculate M and b:

To calculate M and b two simple measurements performed at the end of the production line are required. Chose two reference output currents ( $I_{ref1}$  and  $I_{ref2}$ ) and measure the respective  $V_{SENSE1}$  and  $V_{SENSE2}$ . These four values must then be stored in an EEPROM in order to let the  $\mu$ C use this information to calculate K and b using the simple formulas reported below.

(3)

(4)

Since we defined lout =  $M^*V$ sense + b it is also true that:

Iref1 = M\*Vsense1+b

and

Iref2 = M\*Vsense2+b

Solving these two equations we get the following relations:

M = (Iref1-Iref2)/(Vsense1-Vsense2)

b = (Iref2\*Vsense1 -Iref1\*Vsense2)/(Vsense1-Vsense2)

Example for the chosen device:

Setting Iref1 = 2 A and Iref2 = 4 A according to Table 4 we get Vsense1 = 1.563 V and Vsense2 = 3.115 V then

M=1.289 [S]

b= -0.014 [A]

lout is then:

lout = 1.289\*Vsense - 0.014

(5)

After calibration, the current sense variation is still influenced by the device temperature. Equation (5) is still affected by an error proportional to the sense current thermal drift.

This drift is reported in the datasheet as dK/K. The drift decreases when increasing the output current. For example, in the VND5T035AK datasheet, the drift is +/-15 % at 2 A and it decreases down to +/-5 % when the output current is 10 A.

#### 3.5.4 Open load detection in off-state

- Available if FR\_Stby pin is set high

- Indicated by V<sub>SENSEH</sub> on CS pin

- External pull-up on the output needed

- Possibility to distinguish between open load in off-state and short to V<sub>BAT</sub> using switchable pull-up resistor.

#### Figure 24. Analogue HSD-open load detection in off-state

| Condition    | Pull up | CS                  | FR_Stby |

|--------------|---------|---------------------|---------|

|              | Yes     | 0                   | L       |

| Openleed     | Tes     | V <sub>senseH</sub> | Н       |

| Open load    | No      | 0                   | L       |

|              | NO      | 0                   | Н       |

|              | Yes     | 0                   | L       |

| Short to Vcc |         | V <sub>senseH</sub> | Н       |

|              |         | 0                   | L       |

|              |         | V <sub>senseH</sub> | н       |

|              | Yes     | 0                   | L       |

| Nominal      |         | 0                   | Н       |

|              |         | 0                   | L       |

|              | No      | 0                   | Н       |

Table 5. CS pin levels in off-state

#### Figure 25. Open load/short to Vcc condition

## 3.5.5 Diagnostic summary

*Table 6* summarizes all failure conditions, the V<sub>SENSE</sub> signal behavior and recommendations for diagnostics sampling.

| Fault condition                | Signal                | Value                               |                                                                                            |                                                                                                                       |  |

|--------------------------------|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                                | V <sub>IN</sub>       | L                                   |                                                                                            | Н                                                                                                                     |  |

|                                | FR_Stby               | L or H                              |                                                                                            | L or H                                                                                                                |  |

|                                | V <sub>SENSE</sub>    | 0 V                                 | 0 V                                                                                        |                                                                                                                       |  |

| Open load<br>(without pull-up) | Notes                 |                                     |                                                                                            | Current sense delay<br>response time from<br>rising edge of IN pin<br>must be considered<br>(t <sub>DSENSE2H</sub> ). |  |

|                                | Waveforms<br>Sampling |                                     |                                                                                            | ł<br>!<br>!<br>!                                                                                                      |  |

|                                | V <sub>IN</sub>       | L                                   |                                                                                            | Н                                                                                                                     |  |

|                                | FR_Stby               | L H                                 |                                                                                            | L or H                                                                                                                |  |

|                                | V <sub>SENSE</sub>    | 0 V V <sub>SENSEH</sub>             |                                                                                            | 0 V                                                                                                                   |  |

| Open load<br>(with pull-up)    | Notes                 | Diagnostic in off-state<br>disabled | Delay time from<br>falling edge of IN pin<br>must be considered<br>(t <sub>DSTKON</sub> ). | Current sense delay<br>response time from<br>rising edge of IN pin<br>must be considered<br>(t <sub>DSENSE2H</sub> ). |  |

|                                | Waveforms<br>Sampling | VIN VSENSE                          |                                                                                            | V <sub>OUT</sub> > V <sub>OL</sub>                                                                                    |  |

## Table 6.Diagnostics-overview

| Fault condition                                               | Signal                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Value                                                                                      |                                                                                                                       |  |

|---------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Short circuit to V <sub>BAT</sub>                             | V <sub>IN</sub>       | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                            | Н                                                                                                                     |  |

|                                                               | FR_Stby               | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Н                                                                                          | L or H                                                                                                                |  |

|                                                               | V <sub>SENSE</sub>    | 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>SENSEH</sub>                                                                        | < Nominal                                                                                                             |  |

|                                                               | Notes                 | Diagnostic in off-state<br>disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Delay time from<br>falling edge of IN pin<br>must be considered<br>(t <sub>DSTKON</sub> ). | Current sense delay<br>response time from<br>rising edge of IN pin<br>must be considered<br>(t <sub>DSENSE2H</sub> ). |  |

|                                                               | Waveforms<br>Sampling | VIN <pre> VIN </pre> VIN  V |                                                                                            | Vout > Vol<br>Vsenseh                                                                                                 |  |

| Power limitation or<br>over temperature<br>(Autorestart mode) | V <sub>IN</sub>       | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                            | Н                                                                                                                     |  |

|                                                               | FR_Stby               | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                            | L                                                                                                                     |  |

|                                                               | V <sub>SENSE</sub>    | 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                            | V <sub>SENSEH</sub>                                                                                                   |  |

|                                                               | Notes                 | Diagnostic in off-state disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                            | Current sense delay<br>response time from<br>rising edge of IN pin<br>must be considered<br>(t <sub>DSENSE2H</sub> ). |  |

|                                                               | Waveforms<br>Sampling | V <sub>IN</sub><br>I <sub>LimH</sub><br>I <sub>OUT</sub><br>V <sub>SENSEH</sub><br>V <sub>SENSEH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                            |                                                                                                                       |  |

| Fault condition                                         | Signal                | Value                                                        |                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------------------------------------------|-----------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                         | V <sub>IN</sub>       | L                                                            | Н                                                                                                                                                                                                                                                                                                                                              |  |

| Power limitation or<br>over temperature<br>(Latch mode) | FR_Stby               | н                                                            | Н                                                                                                                                                                                                                                                                                                                                              |  |