# RM0361 Reference manual

Generic Timer Module specification revision 1.5.5.1

#### Introduction

This document is the specification for the Generic Timer Module (GTM).

This manual is a reference document for the SPC572Lx and SPC574Kx devices which are built on Power Architecture<sup>®</sup> technology.

### Contents

| 1 | Prefa | ace      |                                               |

|---|-------|----------|-----------------------------------------------|

|   | 1.1   | Overviev | w                                             |

|   | 1.2   | Docume   | ent structure                                 |

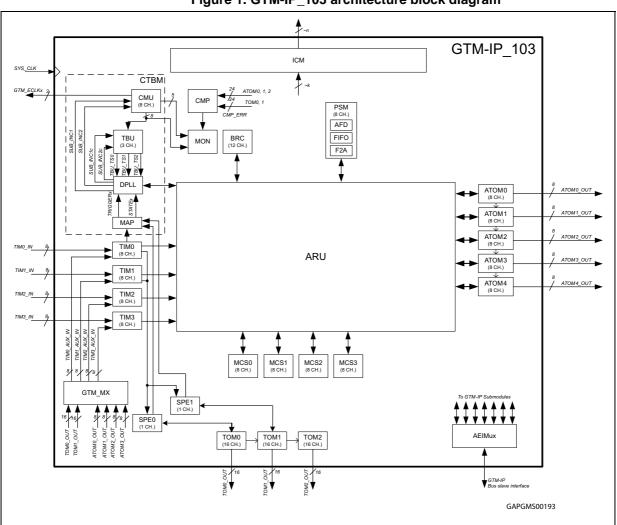

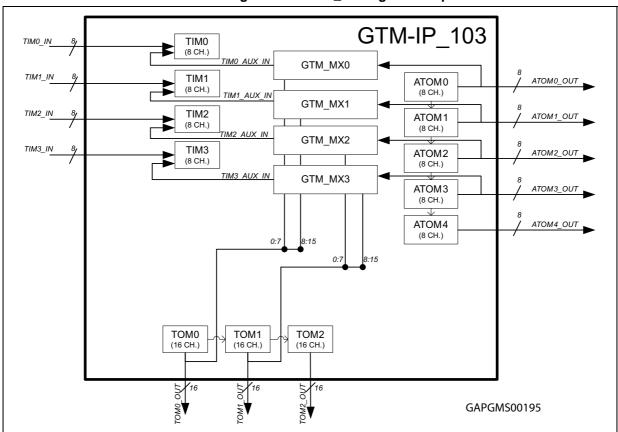

| 2 | GTM   | architec | ture                                          |

|   | 2.1   | Overviev | w                                             |

|   | 2.2   | GTM-IP   | interfaces                                    |

|   |       | 2.2.1    | GTM-IP generic bus interface (AEI)            |

|   |       | 2.2.2    | GTM-IP multi-master and multi-tasking support |

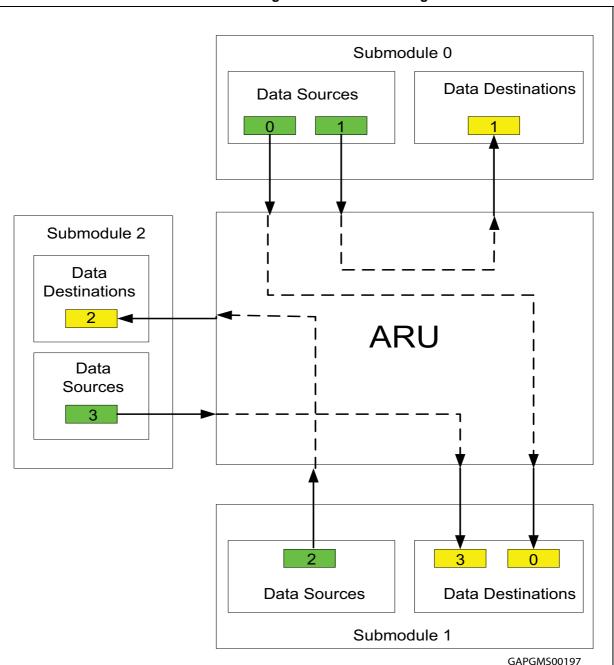

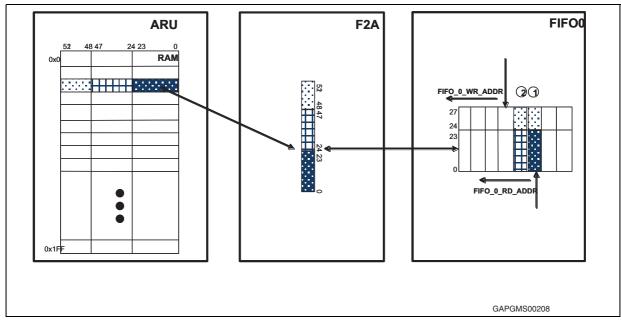

|   | 2.3   | ARU rou  | uting concept                                 |

|   |       | 2.3.1    | Principle of data routing using ARU           |

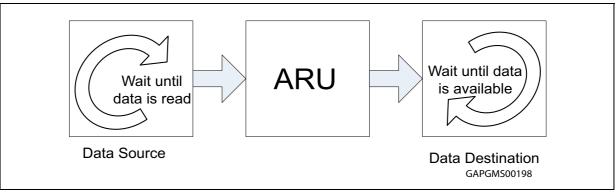

|   |       | 2.3.2    | ARU round trip time                           |

|   |       | 2.3.3    | ARU blocking mechanism                        |

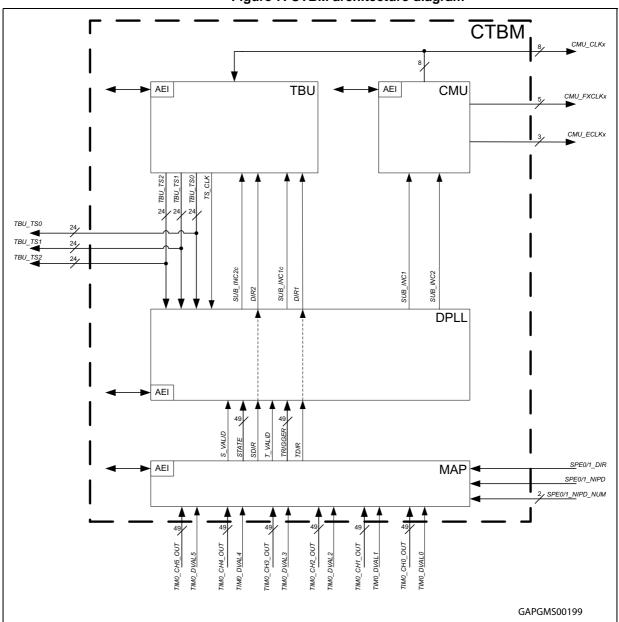

|   | 2.4   | GTM-IP   | Clock and Time Base Management (CTBM) 42      |

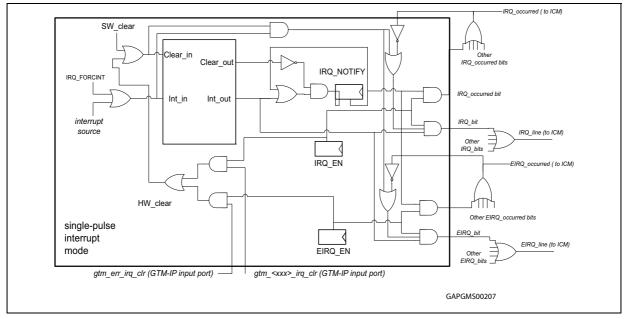

|   | 2.5   | GTM-IP   | interrupt concept                             |

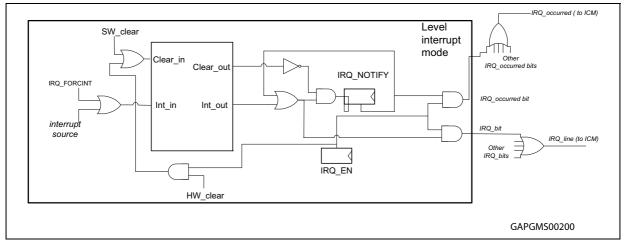

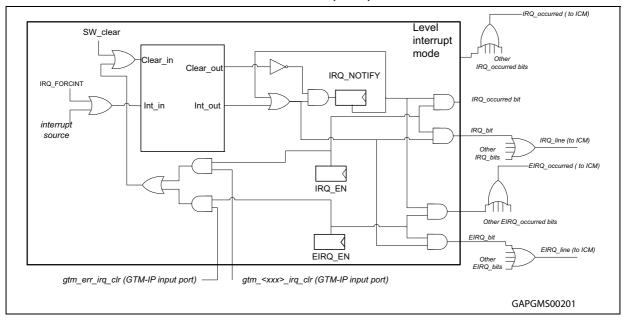

|   |       | 2.5.1    | Level interrupt mode                          |

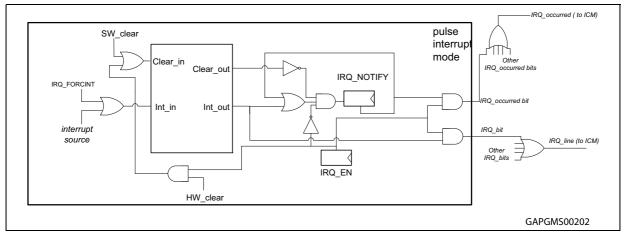

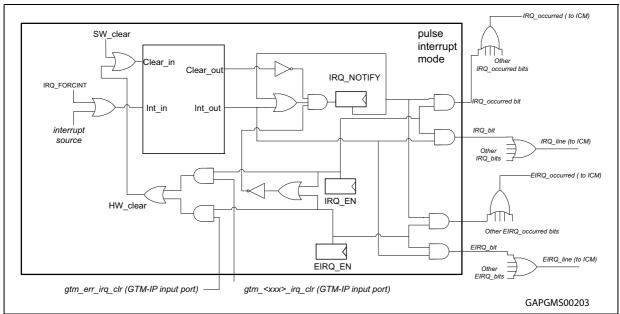

|   |       | 2.5.2    | Pulse interrupt mode                          |

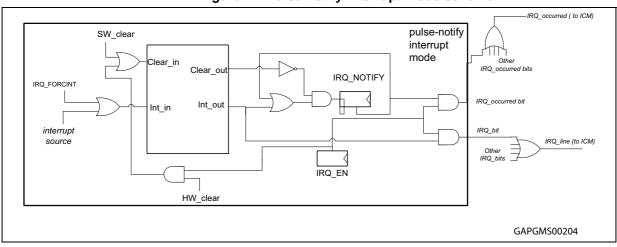

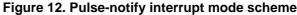

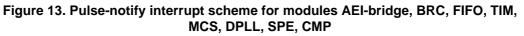

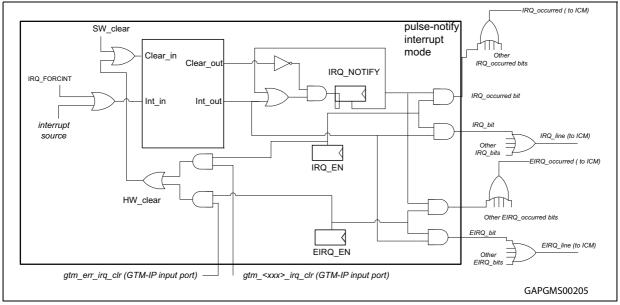

|   |       | 2.5.3    | Pulse-notify interrupt mode                   |

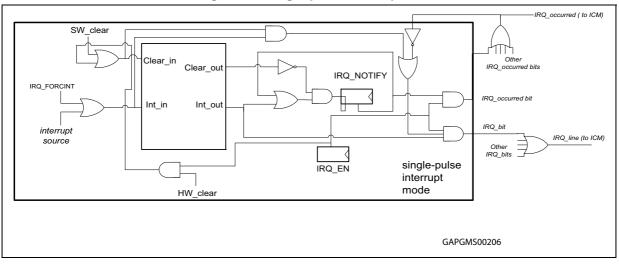

|   |       | 2.5.4    | Single-pulse interrupt mode                   |

|   |       | 2.5.5    | GTM-IP interrupt concentration method         |

|   | 2.6   | GTM-IP   | software debugger support 52                  |

|   | 2.7   | GTM-IP   | programming conventions                       |

|   | 2.8   | GTM-IP   | TOP-level configuration registers overview    |

|   | 2.9   | GTM-IP   | TOP-level configuration registers description |

|   |       | 2.9.1    | Register GTM_REV                              |

|   |       | 2.9.2    | Register GTM_RST                              |

|   |       | 2.9.3    | Register GTM_CTRL                             |

|   |       | 2.9.4    | Register GTM_AEI_ADDR_XPT                     |

|   |       | 2.9.5    | Register GTM_IRQ_NOTIFY                       |

|   |       | 2.9.6    | Register GTM_IRQ_EN                           |

|   |       | 2.9.7    | Register GTM_IRQ_FORCINT                      |

|   |       | 2.9.8    | Register GTM_IRQ_MODE60                       |

|   |       | 2.9.9    | Register GTM_BRIDGE_MODE60                    |

|   |       | 2.9.10  | Register GTM_BRIDGE_PTR1                                       | . 62 |

|---|-------|---------|----------------------------------------------------------------|------|

|   |       | 2.9.11  | Register GTM_BRIDGE_PTR2                                       | . 62 |

|   |       | 2.9.12  | Register GTM_EIRQ_EN                                           | . 63 |

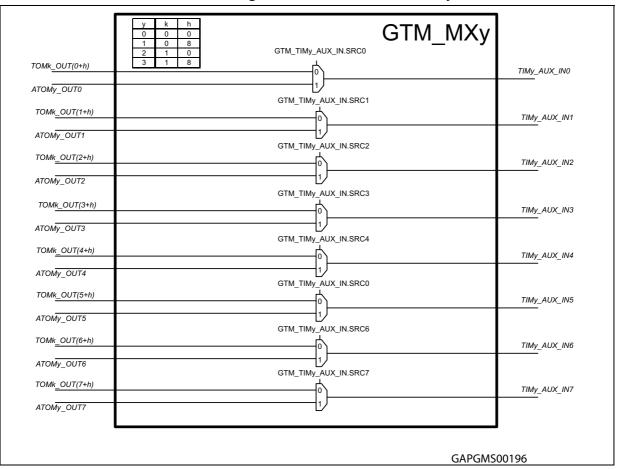

|   |       | 2.9.13  | Register GTM_TIM[i]_AUX_IN_SRC (i= 0 n)                        | . 64 |

| 3 | Adva  | nced Ro | outing Unit (ARU)                                              | 65   |

|   | 3.1   | Overvie | w                                                              | 65   |

|   | 3.2   | Special | data sources                                                   | 65   |

|   | 3.3   | ARU ac  | cess via AEI                                                   | 65   |

|   |       | 3.3.1   | Default ARU access                                             | . 65 |

|   |       | 3.3.2   | Debug access                                                   | . 66 |

|   | 3.4   | ARU int | errupt signals                                                 | 66   |

|   | 3.5   | ARU co  | nfiguration registers overview                                 | 67   |

|   | 3.6   | ARU co  | nfiguration registers description                              | 67   |

|   |       | 3.6.1   | ARU Access register (ARU_ACCESS)                               | . 67 |

|   |       | 3.6.2   | ARU Data High register (ARU_DATA_H)                            | . 69 |

|   |       | 3.6.3   | ARU Data low register (ARU_DATA_L)                             | . 70 |

|   |       | 3.6.4   | ARU Debug Access 0 register (ARU_DBG_ACCESS0)                  | . 70 |

|   |       | 3.6.5   | ARU Debug Data0 High register (ARU_DBG_DATA0_H)                | . 71 |

|   |       | 3.6.6   | ARU Debug Data0 Low register (ARU_DBG_DATA0_L)                 | . 71 |

|   |       | 3.6.7   | ARU Debug Access 1 register (ARU_DBG_ACCESS1)                  | . 72 |

|   |       | 3.6.8   | ARU Debug Data1 High register (ARU_DBG_DATA1_H)                | . 72 |

|   |       | 3.6.9   | ARU Debug Data1 Low register (ARU_DBG_DATA1_L)                 | . 73 |

|   |       | 3.6.10  | ARU IRQ Notification register (ARU_IRQ_NOTIFY)                 |      |

|   |       | 3.6.11  | ARU IRQ Enable register (ARU_IRQ_EN)                           |      |

|   |       | 3.6.12  | ARU Force IRQ register (ARU_IRQ_FORCINT)                       |      |

|   |       | 3.6.13  | ARU IRQ Mode register (ARU_IRQ_MODE)                           | . 75 |

| 4 | Broad | dcast m | odule (BRC)                                                    | 77   |

|   | 4.1   | Overvie | w                                                              | 77   |

|   | 4.2   | BRC co  | nfiguration                                                    | 77   |

|   | 4.3   | BRC int | errupt signals                                                 | 79   |

|   | 4.4   | BRC co  | nfiguration registers overview                                 | 79   |

|   | 4.5   |         | nfiguration registers description                              |      |

|   |       | 4.5.1   | BRC Source x Address register, x:011 (BRC_SRC_[x]_ADDR)        |      |

|   |       | 4.5.2   | BRC Source x to Destination register, x:011 (BRC_SRC_[x]_DEST) |      |

|   |       |         |                                                                |      |

|   |        | 4.5.3     | BRC IRQ Notification register (BRC_IRQ_NOTIFY) | 82   |

|---|--------|-----------|------------------------------------------------|------|

|   |        | 4.5.4     | BRC IRQ Enable register (BRC_IRQ_EN)           | 82   |

|   |        | 4.5.5     | BRC Force IRQ register (BRC_IRQ_FORCINT)       | 83   |

|   |        | 4.5.6     | BRC IRQ Mode register (BRC_IRQ_MODE)           | 83   |

|   |        | 4.5.7     | BRC Error IRQ Enable register (BRC_EIRQ_EN)    | 84   |

|   |        | 4.5.8     | BRC Software Reset register (BRC_RST)          | 84   |

| 5 | First  | In First  | Out module (FIFO)                              | . 85 |

|   | 5.1    | Overvie   | w                                              | . 85 |

|   | 5.2    | Operation | on modes                                       | . 85 |

|   |        | 5.2.1     | Normal operation mode                          | 85   |

|   |        | 5.2.2     | Ring buffer operation mode                     | 86   |

|   | 5.3    | FIFO in   | terrupt signals                                | . 86 |

|   | 5.4    | FIFO co   | onfiguration registers overview                | . 86 |

|   | 5.5    | FIFO co   | onfiguration registers description             | . 87 |

|   |        | 5.5.1     | Register FIFO[i]_CH[x]_CTRL (x:07)             |      |

|   |        | 5.5.2     | Register FIFO[i]_CH[x]_END_ADDR (x:07)         | 88   |

|   |        | 5.5.3     | Register FIFO[i]_CH[x]_START_ADDR (x:07)       | 88   |

|   |        | 5.5.4     | Register FIFO[i]_CH[x]_UPPER_WM (x:07)         | 89   |

|   |        | 5.5.5     | Register FIFO[i]_CH[x]_LOWER_WM (x:07)         | 90   |

|   |        | 5.5.6     | Register FIFO[i]_CH[x]_STATUS (x:07)           | 90   |

|   |        | 5.5.7     | Register FIFO[i]_CH[x]_FILL_LEVEL (x:07)       | 91   |

|   |        | 5.5.8     | Register FIFO[i]_CH[x]_WR_PTR (x:07)           | 91   |

|   |        | 5.5.9     | Register FIFO[i]_CH[x]_RD_PTR (x:07)           | 92   |

|   |        | 5.5.10    | Register FIFO[i]_CH[x]_IRQ_NOTIFY (x:07)       | 92   |

|   |        | 5.5.11    | Register FIFO[i]_CH[x]_IRQ_EN (x:07)           | 93   |

|   |        | 5.5.12    | Register FIFO[i]_CH[x]_IRQ_FORCINT             | 93   |

|   |        | 5.5.13    | Register FIFO[i]_CH[x]_IRQ_MODE                | 94   |

|   |        | 5.5.14    | Register FIFO[i]_CH[x]_EIRQ_EN (x:07)          | 95   |

| 6 | AEI to | o FIFO d  | lata interface (AFD)                           | . 96 |

|   | 6.1    | Overvie   | w                                              | . 96 |

|   | 6.2    | AFD reg   | gister overview                                | . 96 |

|   | 6.3    | AFD reg   | gister description                             | . 96 |

|   |        | 6.3.1     | Register AFD[i]_CH[x]_BUF_ACC (x:07)           | 96   |

| FIFO  | to ARU unit (F2A)9                                                                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1   | Overview                                                                                                                      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2   | Transfer modes                                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.3   | F2A configuration registers overview                                                                                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.4   | F2A configuration registers description                                                                                       | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 7.4.1 Register F2A[i]_ENABLE                                                                                                  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 7.4.2 Register F2A[i]_CH[x]_ARU_RD_FIFO (x: 07)                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 7.4.3 Register F2A[i]_CH[x]_STR_CFG (x: 07)                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

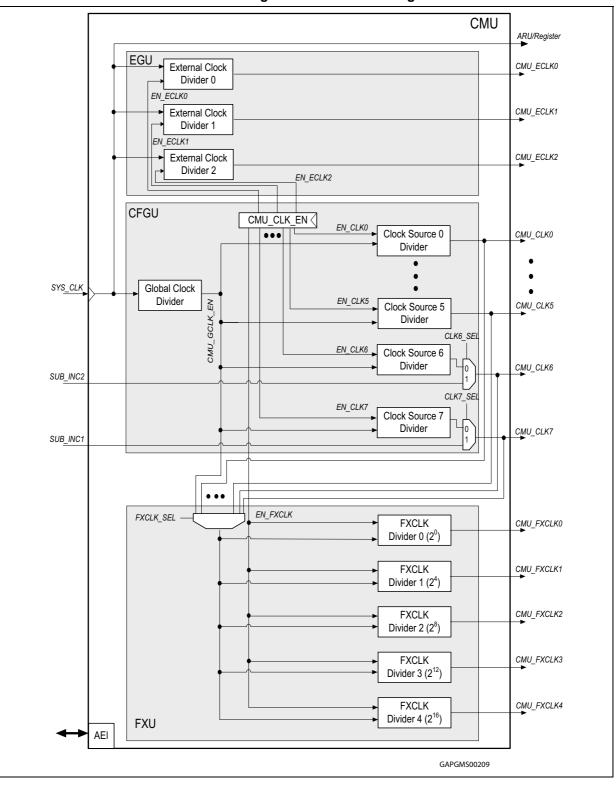

| Clock | Management Unit (CMU) 10                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.1   | Overview                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.1.1 CMU block diagram                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.2   | Global clock divider                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.3   | Configurable clock generation subunit (CFGU) 10                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

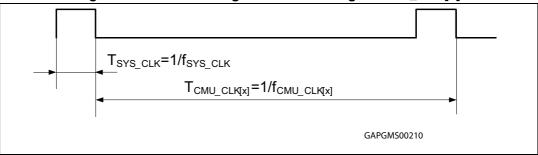

| 8.4   | Wave form of generated clock signal CMU_CLK[x] 10-                                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.5   | Fixed clock generation (FXU) 10                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.6   | External Generation Unit (EGU) 10                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.7   | CMU configuration registers overview 10                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8.8   | CMU configuration register description                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.8.1 Register CMU_CLK_EN                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.8.2 Register CMU_GCLK_NUM                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.8.3 Register CMU_GCLK_DEN                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.8.4 Register CMU_CLK_[x]_CTRL (x:05)                                                                                        | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 8.8.5 Register CMU_CLK_6_CTRL 10                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | 8.8.9 Register CMU_FXCLK_CTRL 11                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

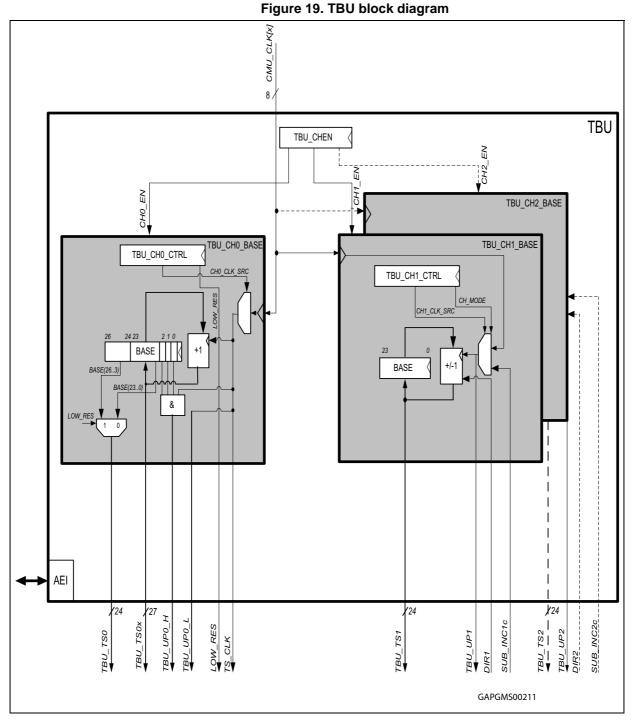

| Time  | Base Unit (TBU)                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9.1   | Overview                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 9.1.1 TBU block diagram                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9.2   | TBU time base channels                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 9.2.1 TBU channel modes                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9.3   | TBU configuration registers overview                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 7.1<br>7.2<br>7.3<br>7.4<br><b>Clock</b><br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br><b>Time</b><br>9.1<br>9.1 | 7.2       Transfer modes       9         7.3       F2A configuration registers overview       9         7.4       F2A configuration registers description       9         7.4.1       Register F2A[i]_ENABLE       9         7.4.2       Register F2A[i]_CH[x]_ARU_RD_FIFO (x: 07)       10         7.4.3       Register F2A[i]_CH[x]_STR_CFG (x: 07)       10         7.4.3       Register F2A[i]_CH[x]_STR_CFG (x: 07)       10         8.1       Overview       10         8.1.1       CMU block diagram       10         8.2       Global clock divider       10         8.3       Configurable clock generation subunit (CFGU)       10         8.4       Wave form of generated clock signal CMU_CLK[x]       10         8.5       Fixed clock generation (FXU)       10         8.6       External Generation Unit (EGU)       10         8.7       CMU configuration register description       10         8.8       CMU configuration register description       10         8.8.1       Register CMU_CLK_EN       10         8.8.2       Register CMU_GCLK_DEN       10         8.8.3       Register CMU_CLK_IZ_CTRL (x:05)       10         8.8.4       Register CMU_CLK_IZ_CTRL (x:05) |

|    | 9.4  | TBU reg   | gisters description1                           | 16  |

|----|------|-----------|------------------------------------------------|-----|

|    |      | 9.4.1     | Register TBU_CHEN 1                            | 116 |

|    |      | 9.4.2     | Register TBU_CH0_CTRL 1                        | 117 |

|    |      | 9.4.3     | Register TBU_CH0_BASE 1                        | 118 |

|    |      | 9.4.4     | Register TBU_CH[y]_CTRL (y:1, 2) 1             | 118 |

|    |      | 9.4.5     | Register TBU_CH[y]_BASE (y:1,2) 1              | 119 |

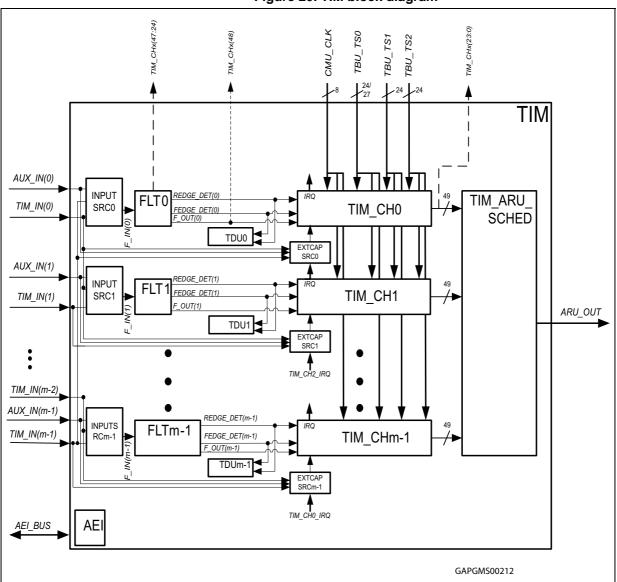

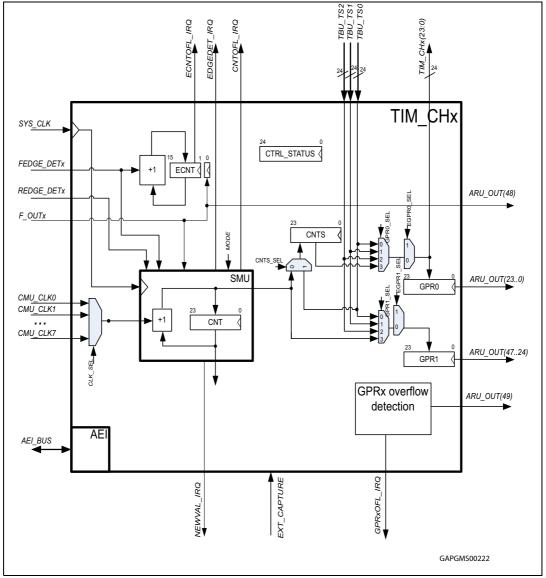

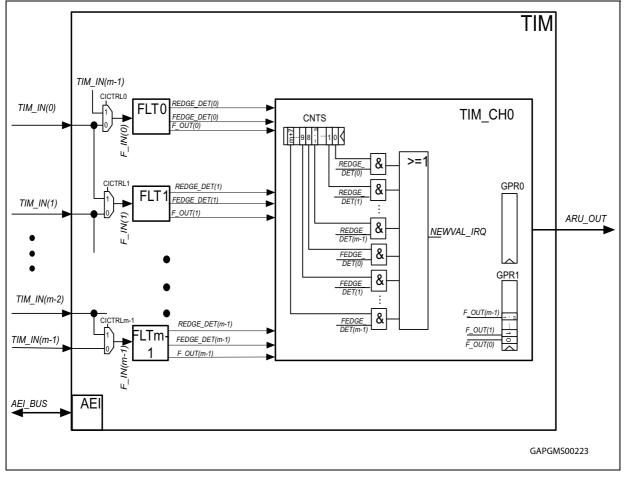

| 10 | Time | r Input I | Module (TIM)                                   | 20  |

|    | 10.1 | Overvie   | ew                                             | 20  |

|    |      | 10.1.1    | TIM block diagram 1                            | 121 |

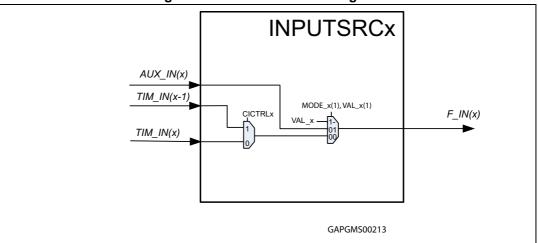

|    |      | 10.1.2    | Input source selection INPUTSRCx 1             | 122 |

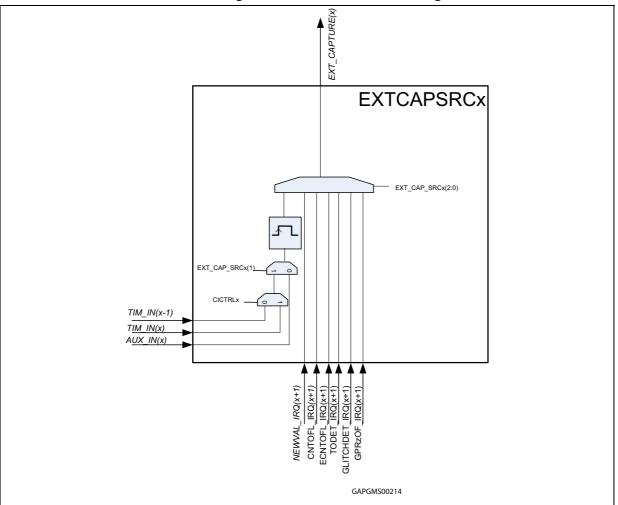

|    |      | 10.1.3    | External capture source selection EXTCAPSRCx 1 | 23  |

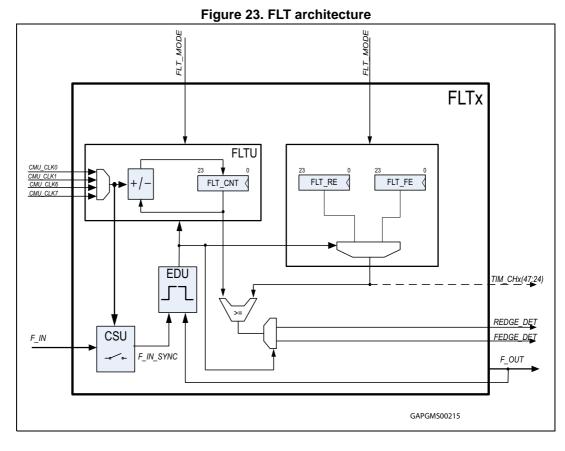

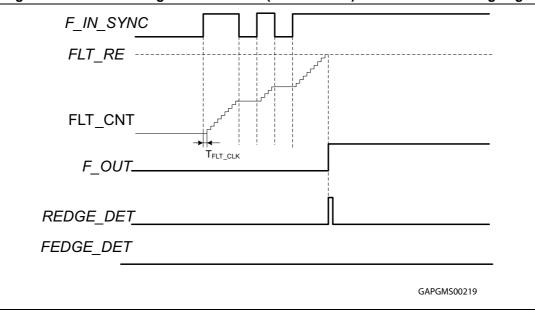

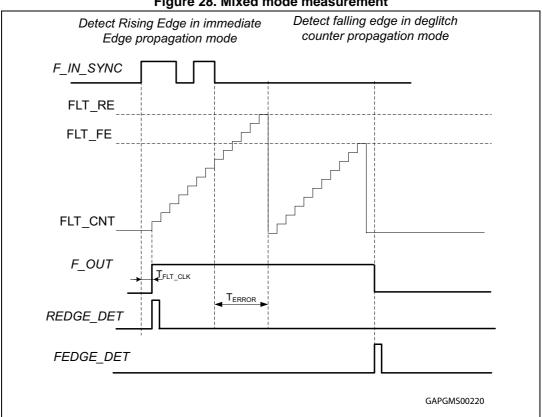

|    | 10.2 | TIM filte | er functionality (FLT) 1                       | 24  |

|    |      | 10.2.1    | Overview                                       | 124 |

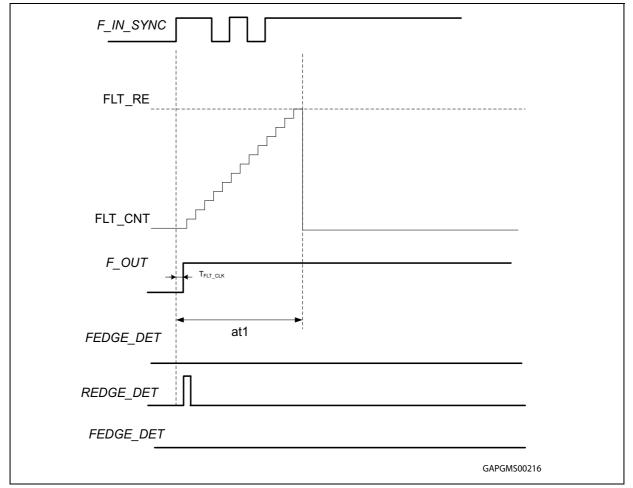

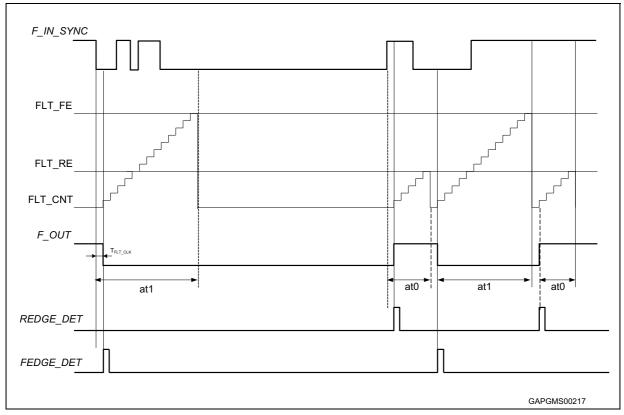

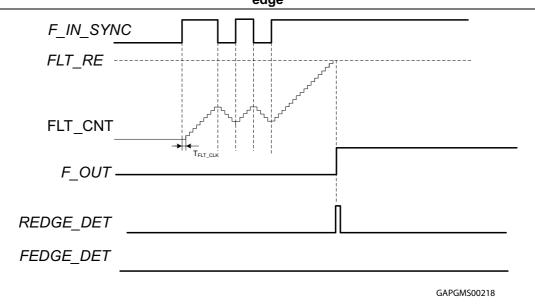

|    |      | 10.2.2    | TIM filter modes 1                             | 125 |

|    |      | 10.2.3    | TIM filter reconfiguration 1                   | 130 |

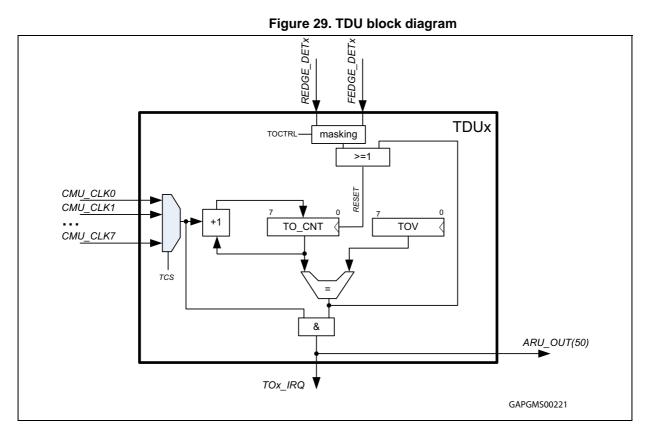

|    | 10.3 | Timeou    | t Detection Unit (TDU) 1                       | 30  |

|    | 10.4 | TIM cha   | annel architecture                             | 32  |

|    |      | 10.4.1    | Overview                                       | 132 |

|    |      | 10.4.2    | TIM channel modes 1                            | 134 |

|    | 10.5 | MAP su    | ubmodule interface                             | 44  |

|    | 10.6 | TIM inte  | errupt signals                                 | 44  |

|    | 10.7 | TIM cor   | nfiguration registers overview1                | 44  |

|    | 10.8 | TIM cor   | nfiguration registers description 1            | 45  |

|    |      | 10.8.1    | Register TIM[i]_CH[x]_CTRL (x:0m-1) (i=1n)     |     |

|    |      | 10.8.2    | Register TIM0_CH[x]_CTRL (x:0m-1)              |     |

|    |      | 10.8.3    | Register TIM[i]_CH[x]_FLT_RE (x:0m-1)          | 153 |

|    |      | 10.8.4    | Register TIM[i]_CH[x]_FLT_FE (x:0m-1)          | 153 |

|    |      | 10.8.5    | Register TIM[i]_CH[x]_TDU (x:0m-1)             | 54  |

|    |      | 10.8.6    | Register TIM[i]_CH[x]_GPR0 (x:0m-1)            | 154 |

|    |      | 10.8.7    | Register TIM[i]_CH[x]_GPR1 (x:0m-1)            | 154 |

|    |      | 10.8.8    | Register TIM[i]_CH[x]_CNT (x:0m-1)             | 155 |

|    |      | 10.8.9    | Register TIM[i]_CH[x]_CNTS (x:0m-1)            | 155 |

|    |      | 10.8.10   | Register TIM[i]_CH[x]_IRQ_NOTIFY (x:0m-1)      | 156 |

|    |      | 10.8.11   | Register TIM[i]_CH[x]_IRQ_EN (x:0m-1)1         | 57  |

|    |      | 10.8.12   | Register TIM[i]_CH[x]_IRQ_FORCINT (x:0m-1) 1   | 57  |

|    |      | 10.8.13 | Register TIM[i]_CH[x]_IRQ_MODE (x:0m-1)                                   |

|----|------|---------|---------------------------------------------------------------------------|

|    |      | 10.8.14 | Register TIM[i]_RST159                                                    |

|    |      | 10.8.15 | Register TIM[i]_IN_SRC159                                                 |

|    |      | 10.8.16 | Register TIM[i]_CH[x]_EIRQ_EN (x:0m-1)                                    |

|    |      | 10.8.17 | Register TIM[i]_CH[x]_TDUV (x:0m-1)                                       |

|    |      | 10.8.18 | Register TIM[i]_CH[x]_TDUC (x:0m-1)                                       |

|    |      | 10.8.19 | Register TIM[i]_CH[x]_ECNT (x:0m-1)                                       |

|    |      | 10.8.20 | Register TIM[i]_CH[x]_ECTRL (x:0m-1)                                      |

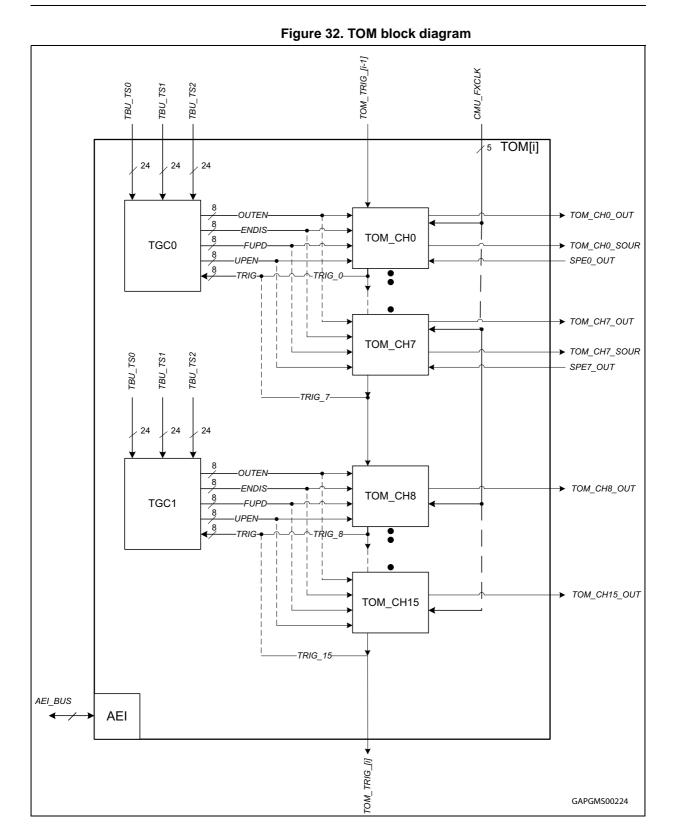

| 11 | Time | r Outpu | t Module (TOM)                                                            |

|    | 11.1 | Overvie | ew                                                                        |

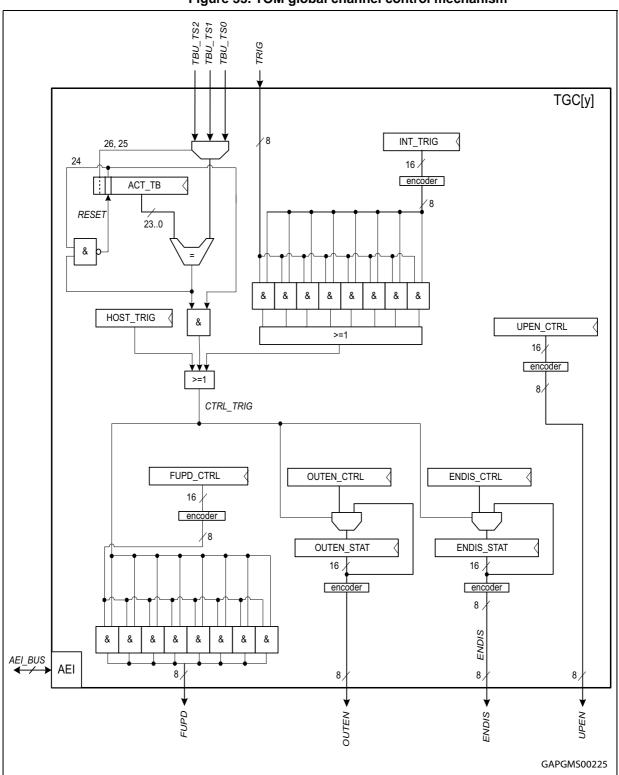

|    | 11.2 | TOM gl  | obal channel control (TGC0, TGC1)                                         |

|    |      | 11.2.1  | Overview                                                                  |

|    |      | 11.2.2  | TGC subunit                                                               |

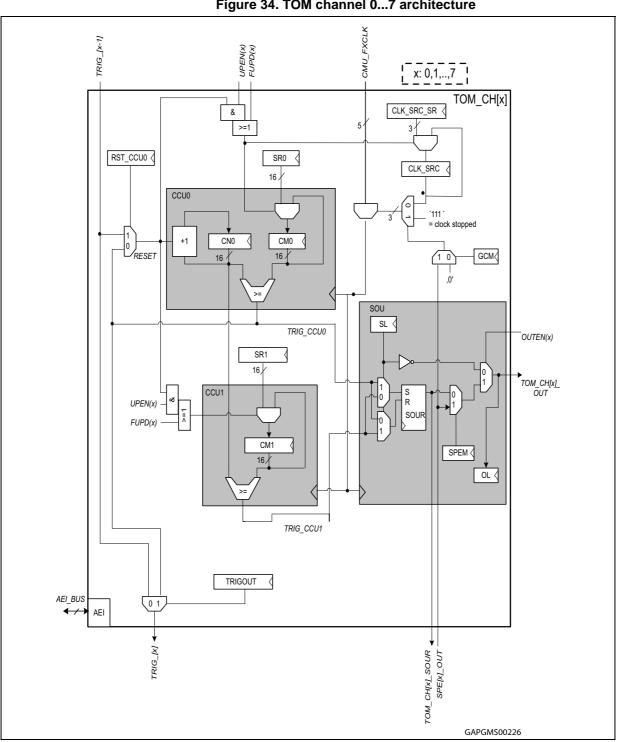

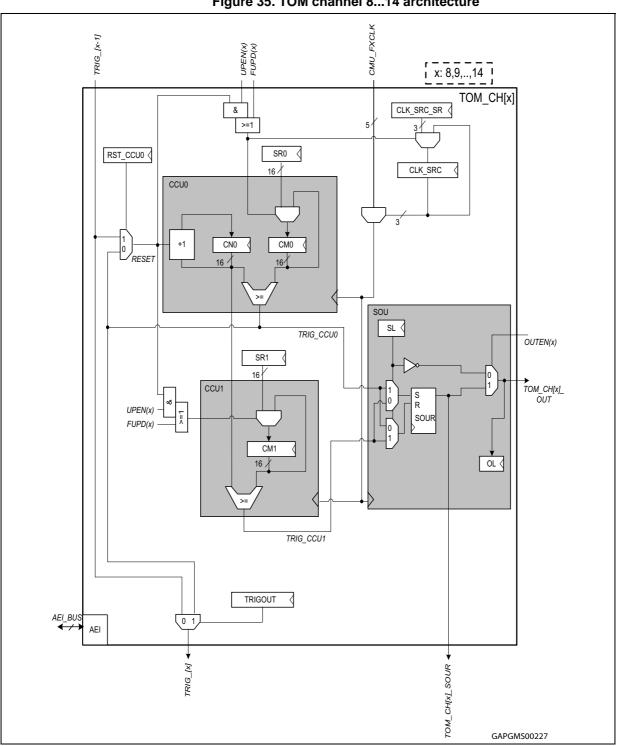

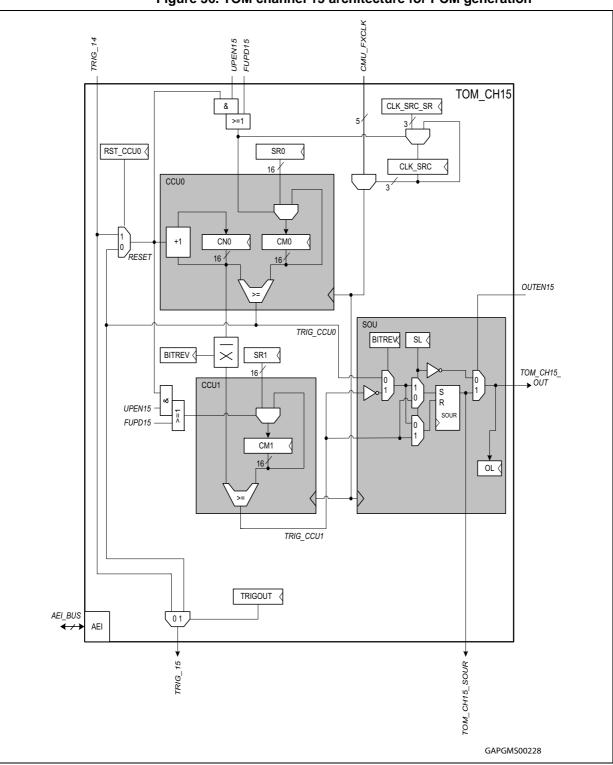

|    | 11.3 | TOM ch  | nannel (TOM_CH[x]) 169                                                    |

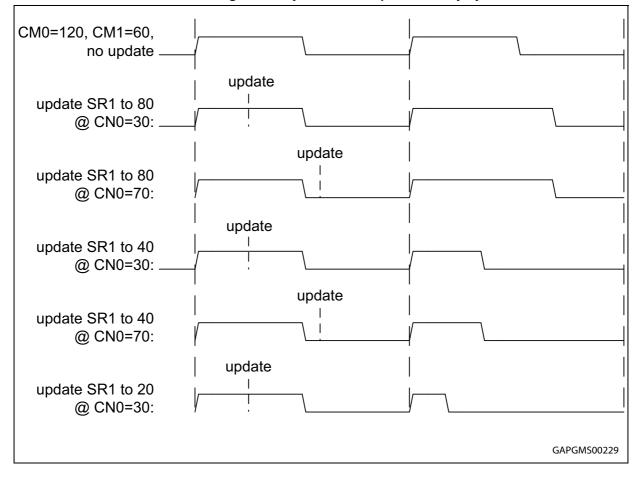

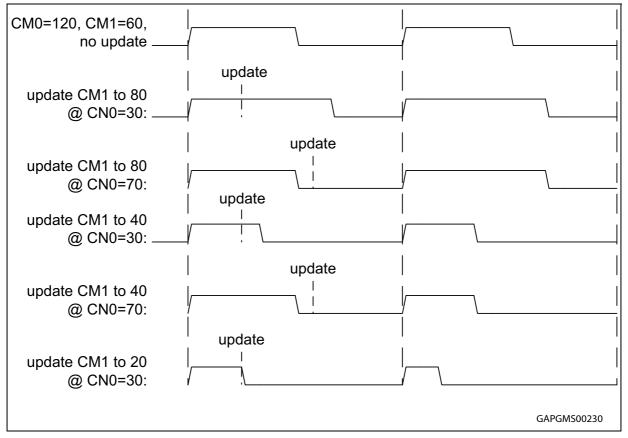

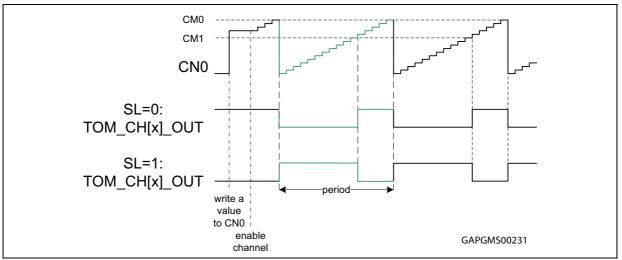

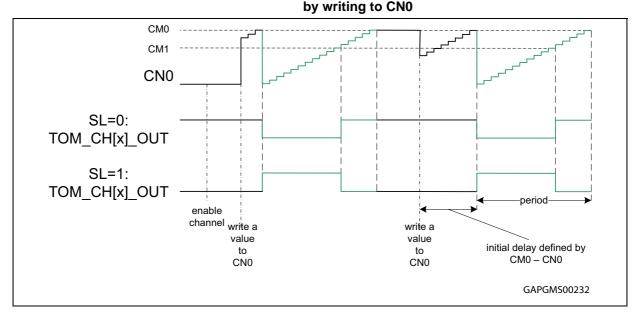

|    |      | 11.3.1  | Duty cycle, period and selected counter clock frequency update mechanisms |

|    |      | 11.3.2  | TOM continuous mode                                                       |

|    |      | 11.3.3  | TOM one shot mode                                                         |

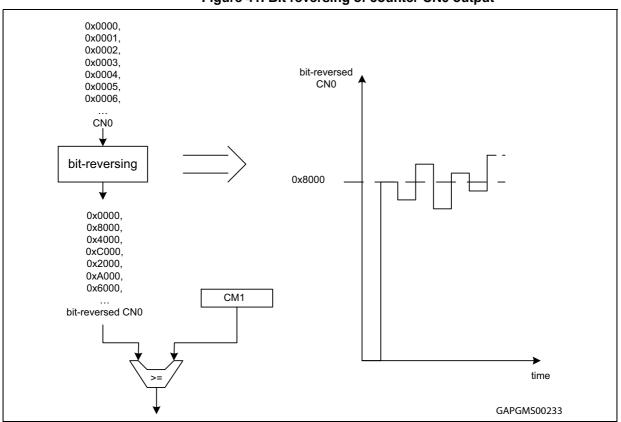

|    |      | 11.3.4  | Pulse count modulation                                                    |

|    | 11.4 | TOM BI  | LDC support                                                               |

|    | 11.5 | TOM ga  | ated counter mode 179                                                     |

|    | 11.6 | TOM in  | terrupt signals                                                           |

|    | 11.7 | TOM co  | onfiguration registers overview                                           |

|    | 11.8 | TOM co  | onfiguration registers description                                        |

|    |      | 11.8.1  | Register TOM[i]_TGC0_GLB_CTRL                                             |

|    |      | 11.8.2  | Register TOM[i]_TGC0_ENDIS_CTRL                                           |

|    |      | 11.8.3  | Register TOM[i]_TGC0_ENDIS_STAT                                           |

|    |      | 11.8.4  | Register TOM[i]_TGC0_ACT_TB                                               |

|    |      | 11.8.5  | Register TOM[i]_TGC0_OUTEN_CTRL                                           |

|    |      | 11.8.6  | Register TOM[i]_TGC0_OUTEN_STAT                                           |

|    |      | 11.8.7  | Register TOM[i]_TGC0_FUPD_CTRL                                            |

|    |      | 11.8.8  | Register TOM[i]_TGC0_INT_TRIG189                                          |

|    |      | 11.8.9  | Register TOM[i]_TGC1_GLB_CTRL                                             |

|    |      | 11.8.10 | Register TOM[i]_TGC1_ENDIS_CTRL                                           |

|    |      | 11.8.11 | Register TOM[i]_TGC1_ENDIS_STAT                                           |

|    |      | 11.8.12 | Register TOM[i]_TGC1_ACT_TB               | 190   |

|----|------|---------|-------------------------------------------|-------|

|    |      | 11.8.13 | Register TOM[i]_TGC1_OUTEN_CTRL           | 190   |

|    |      | 11.8.14 | Register TOM[i]_TGC1_OUTEN_STAT           | 190   |

|    |      | 11.8.15 | Register TOM[i]_TGC1_FUPD_CTRL            | 190   |

|    |      | 11.8.16 | Register TOM[i]_TGC1_INT_TRIG             | 190   |

|    |      | 11.8.17 | Register TOM[i]_CH[x]_CTRL (x:014)        | 191   |

|    |      | 11.8.18 | Register TOM[i]_CH15_CTRL                 | 192   |

|    |      | 11.8.19 | Register TOM[i]_CH[x]_CN0 (x:015)         | 194   |

|    |      | 11.8.20 | Register TOM[i]_CH[x]_CM0 (x:015)         | 194   |

|    |      | 11.8.21 | Register TOM[i]_CH[x]_SR0 (x:015)         | 194   |

|    |      | 11.8.22 | Register TOM[i]_CH[x]_CM1 (x:015)         | 195   |

|    |      | 11.8.23 | Register TOM[i]_CH[x]_SR1 (x:015)         | 195   |

|    |      | 11.8.24 | Register TOM[i]_CH[x]_STAT (x:015)        | 196   |

|    |      | 11.8.25 | Register TOM[i]_CH[x]_IRQ_NOTIFY (x:015)  | 196   |

|    |      | 11.8.26 | Register TOM[i]_CH[x]_IRQ_EN (x:015)      | 197   |

|    |      | 11.8.27 | Register TOM[i]_CH[x]_IRQ_FORCINT (x:015) | 197   |

|    |      | 11.8.28 | Register TOM[i]_CH[x]_IRQ_MODE (x:015)    | 198   |

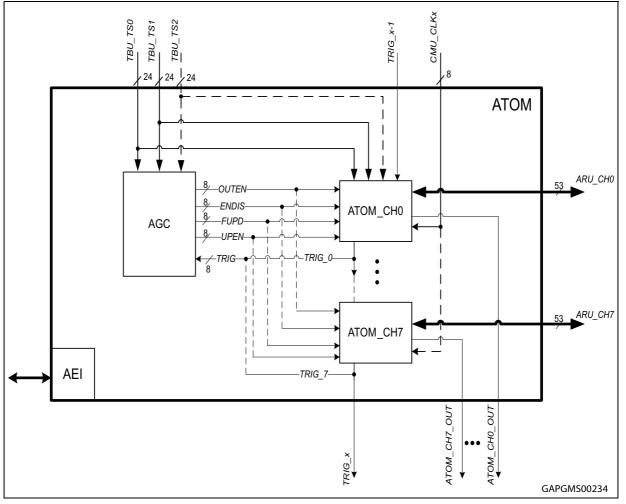

| 12 | ARU  | -connec | ted Timer Output Module (ATOM)            | . 199 |

|    | 12.1 |         | • • • • • • • • • • • • • • • • • • •     |       |

|    |      | 12.1.1  | ATOM Global Control (AGC)                 |       |

|    |      | 12.1.2  | ATOM channel mode overview                |       |

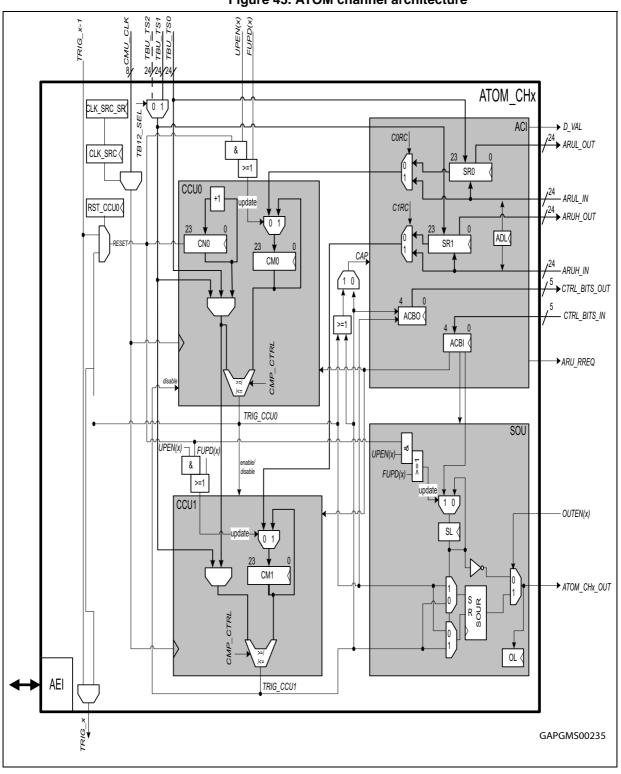

|    | 12.2 | ATOM    | channel architecture                      |       |

|    |      | 12.2.1  | ATOM channel architecture                 |       |

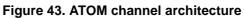

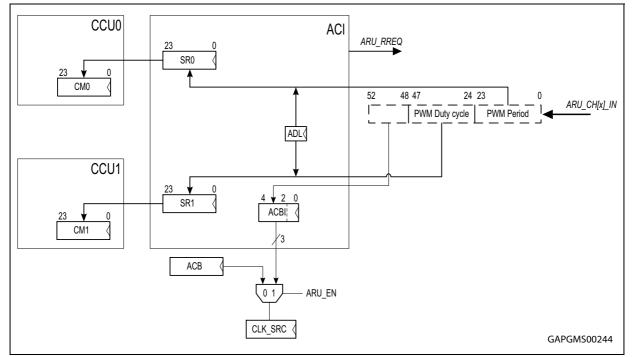

|    |      | 12.2.2  | ARU communication interface (ACI)         |       |

|    | 12.3 |         | channel modes                             |       |

|    |      | 12.3.1  | ATOM Signal Output Mode Immediate (SOMI)  | 205   |

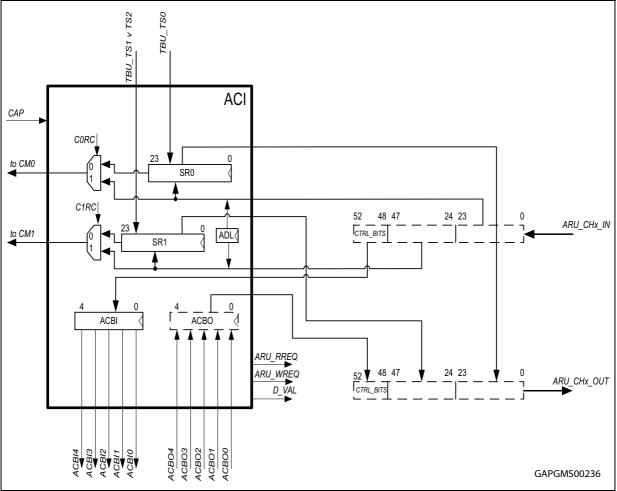

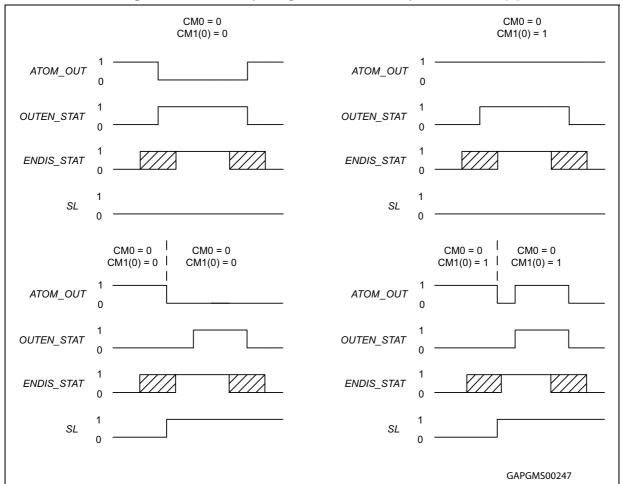

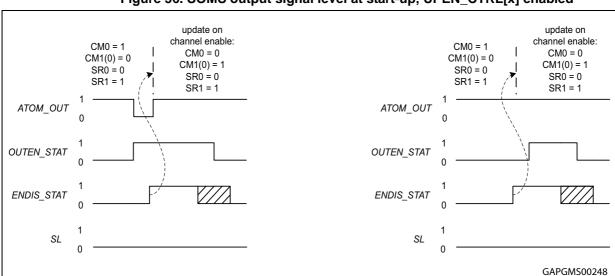

|    |      | 12.3.2  | ATOM Signal Output Mode Compare (SOMC)    | 207   |

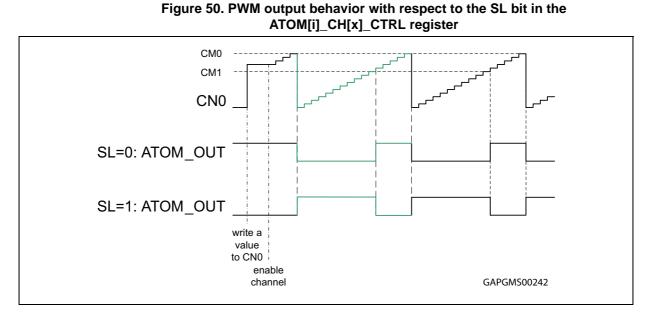

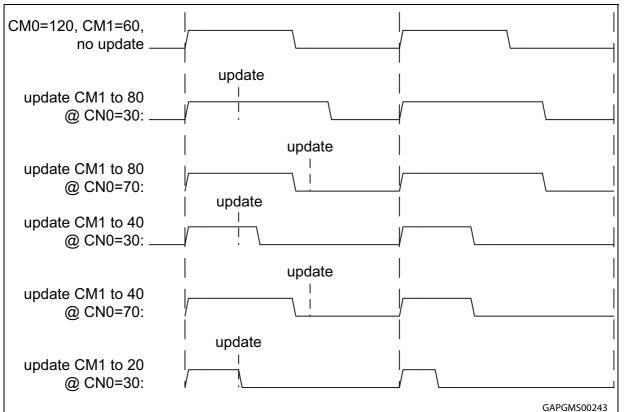

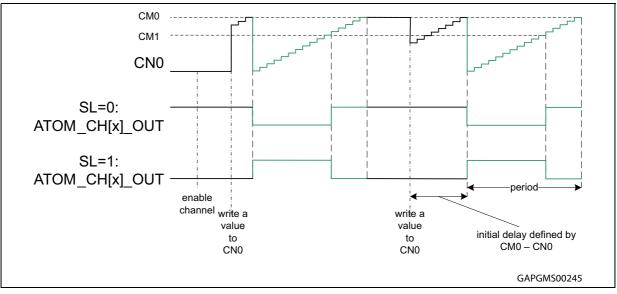

|    |      | 12.3.3  | ATOM Signal Output Mode PWM (SOMP)        | 224   |

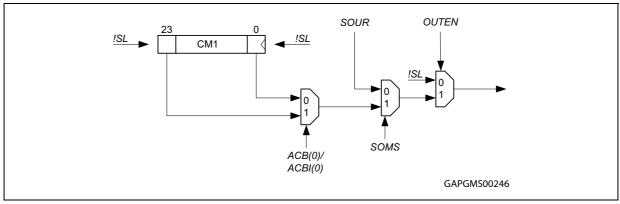

|    |      | 12.3.4  | ATOM Signal Output Mode Serial (SOMS)     | 231   |

|    | 12.4 | ATOM i  | interrupt signals                         | . 236 |

|    | 12.5 | ATOM    | register overview                         | . 236 |

|    | 12.6 | ATOM    | register description                      | . 238 |

|    |      | 12.6.1  | Register ATOM[i]_AGC_GLB_CTRL             | . 238 |

|    |      | 12.6.2  | ATOM[i]_AGC_ENDIS_CTRL                    | 239   |

|    |      | 12.6.3  | ATOM[i]_AGC_ENDIS_STAT                    | 240   |

|    |              | 12.6.4                                                                                                                                                     | ATOM[i]_AGC_ACT_TB                                                                                                                                                                                                                                                                                                                                                                                                                              | . 241                                                                                                                                    |

|----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|    |              | 12.6.5                                                                                                                                                     | ATOM[i]_AGC_OUTEN_CTRL                                                                                                                                                                                                                                                                                                                                                                                                                          | . 242                                                                                                                                    |

|    |              | 12.6.6                                                                                                                                                     | ATOM[i]_AGC_OUTEN_STAT                                                                                                                                                                                                                                                                                                                                                                                                                          | . 243                                                                                                                                    |

|    |              | 12.6.7                                                                                                                                                     | ATOM[i]_AGC_FUPD_CTRL                                                                                                                                                                                                                                                                                                                                                                                                                           | . 244                                                                                                                                    |

|    |              | 12.6.8                                                                                                                                                     | ATOM[i]_AGC_INT_TRIG                                                                                                                                                                                                                                                                                                                                                                                                                            | . 246                                                                                                                                    |

|    |              | 12.6.9                                                                                                                                                     | Register ATOM[i]_CH[x]_CTRL (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                             | . 247                                                                                                                                    |

|    |              | 12.6.10                                                                                                                                                    | Register ATOM[i]_CH[x]_STAT (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                             | . 250                                                                                                                                    |

|    |              | 12.6.11                                                                                                                                                    | Register ATOM[i]_CH[x]_RDADDR (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                           | . 251                                                                                                                                    |

|    |              | 12.6.12                                                                                                                                                    | Register ATOM[i]_CH[x]_CN0 (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                              | . 251                                                                                                                                    |

|    |              | 12.6.13                                                                                                                                                    | Register ATOM[i]_CH[x]_CM0 (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                              | . 252                                                                                                                                    |

|    |              | 12.6.14                                                                                                                                                    | Register ATOM[i]_CH[x]_SR0 (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                              | . 252                                                                                                                                    |

|    |              | 12.6.15                                                                                                                                                    | Register ATOM[i]_CH[x]_CM1 (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                              | . 252                                                                                                                                    |

|    |              | 12.6.16                                                                                                                                                    | Register ATOM[i]_CH[x]_SR1 (x: 07)                                                                                                                                                                                                                                                                                                                                                                                                              | . 253                                                                                                                                    |

|    |              | 12.6.17                                                                                                                                                    | Register ATOM[i]_CH[x]_IRQ_NOTIFY (x:07)                                                                                                                                                                                                                                                                                                                                                                                                        | . 253                                                                                                                                    |

|    |              | 12.6.18                                                                                                                                                    | Register ATOM[i]_CH[x]_IRQ_EN (x:07)                                                                                                                                                                                                                                                                                                                                                                                                            | . 254                                                                                                                                    |

|    |              | 12.6.19                                                                                                                                                    | Register ATOM[i]_CH[x]_IRQ_FORCINT (x:07)                                                                                                                                                                                                                                                                                                                                                                                                       | . 255                                                                                                                                    |

|    |              | 12.6.20                                                                                                                                                    | Register ATOM[i]_CH[x]_IRQ_MODE (x:07)                                                                                                                                                                                                                                                                                                                                                                                                          | . 255                                                                                                                                    |

|    |              | _                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

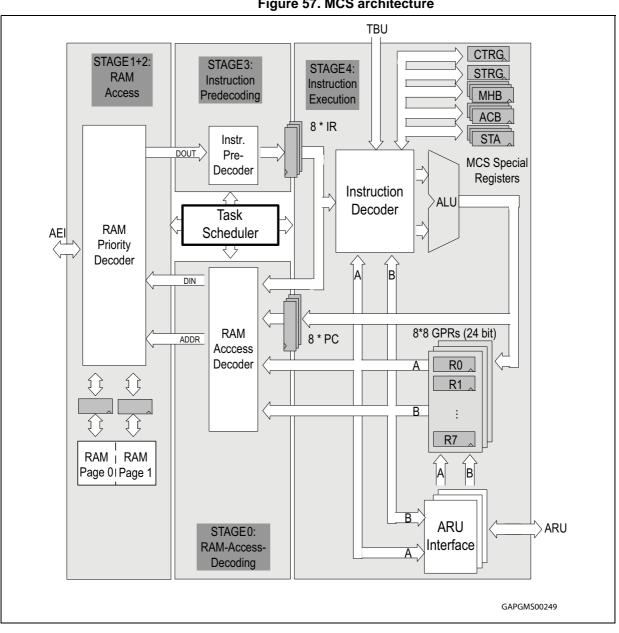

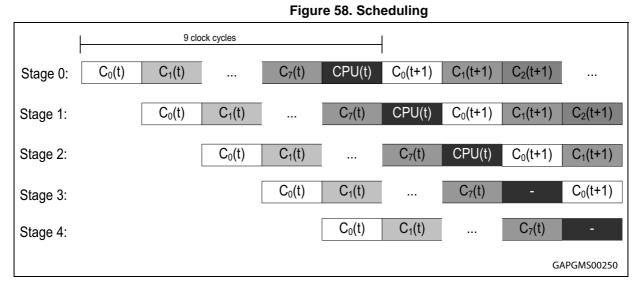

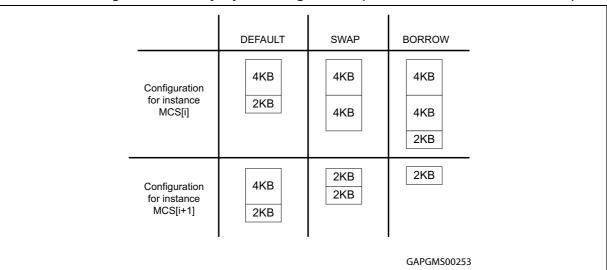

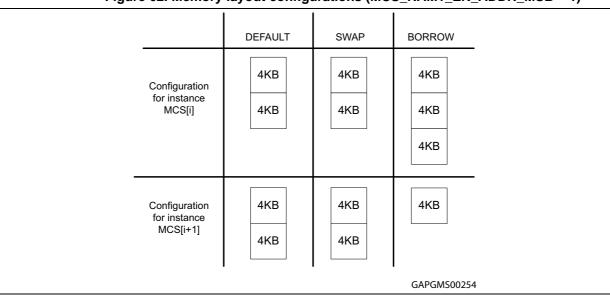

| 13 | Multi        |                                                                                                                                                            | el Sequencer (MCS)                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |