Consent Manager Tag v2.0 (for TCF 2.0) -->

Amplificateurs audio Classe D Une révolution silencieuse - PDF - Farnell Element 14

Amplificateurs audio Classe D Une révolution silencieuse - PDF - Farnell Element 14

Amplificateurs audio Classe D Une révolution silencieuse - PDF - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

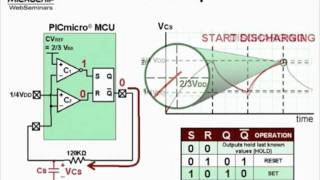

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Documents PDF :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 26-Mar-2014 18:02 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 10-Mar-2014 15:52 1.5M

A Premier Farnell Company

18

Amplificateurs audio Classe D

Une révolution silencieuse

Classe A

Lorsque l’efficacité n’est pas un critère primordial,

comme pour la plupart des petits amplificateurs

linéaires, la conception utilisée est de type classe A,

cela signifie que les étages de sortie sont toujours

dans la zone de conduction. Les amplificateurs classe

A sont en général plus linéaires et moins complexes

que d’autres modèles, mais peu efficaces. Ce type

d’amplificateur est le plus souvent utilisé pour les petits

signaux ou pour les applications à faible puissance

(comme des écouteurs).

Classe B

En classe B, il existe deux étages de sortie (ou

ensembles de circuits de sortie), chacun utilisant une

alternance d’une amplitude de 180° ou la moitié du

cycle du signal d’entrée.

Classe AB

Les amplificateurs de classe AB sont un compromis

entre classe A et B, améliorant la linéarité en sortie

pour les petits signaux, avec une modulation

d’amplitude allant de 180° à plus, selon la conception

de l’amplificateur. On les trouve généralement dans les

amplificateurs basse fréquence (audio et hi-fi) en raison

de leur rendement relativement élevé, ou dans d’autres

applications exigeant à la fois linéarité et rendement

(téléphones mobiles, transmetteurs TV, etc.).

Classe C

Appréciée pour les amplificateurs RF haute puissance,

la classe C se définit par une variation de phase du

signal d’entrée inférieure à 180°. La linéarité n’est

pas très bonne, mais cela n’a aucune importance pour

de simples amplificateurs de puissance. Le signal

reprend une forme presque sinusoïdale via un circuit

accordé et le rendement est très supérieur à celui des

amplificateurs de classes A, AB ou B.

Classe D

Les amplificateurs de classe D utilisent la commutation

pour obtenir un rendement énergétique élevé (plus

de 90% dans les modèles récents). En permettant

à chaque étages de sortie d’être totalement sous

ou hors tension, les pertes sont minimisées. Une

méthode simple, comme la modulation de largeur

d’impulsion, est parfois encore utilisée. Cependant,

les amplificateurs de commutation haute performance

utilisent des techniques numériques, comme la

modulation sigma-delta, pour obtenir de meilleures

performances. D’abord utilisés spécifiquement

avec les haut-parleurs de graves, pour leur bande

passante limitée et leur distorsion relativement

élevée, l’évolution des circuits semiconducteurs a

permis le développement d’une gamme complète

d’amplificateurs audio HIFI en classe D, avec un rapport

signal/bruit et des niveaux de distorsion similaires à

leurs homologues linéaires.

La classe D offre de gros avantages en termes

de gain d’espace, d’efficacité énergétique et de

dissipation thermique. Depuis qu’une gamme complète

d’amplificateurs classe D, offrant tous les niveaux de

puissance, est disponible chez Texas Instruments,

la haute fidélité et la fiabilité ne constituent plus un

problème comparé aux débuts de cette technologie.

Avant, les interférences EMI dans les amplificateurs

classe D étaient parfois considérées comme un facteur

critique pour certaines applications. Aujourd’hui,

on trouve ce type d’amplificateurs dans toutes les

applications dites « critiques », comme les combinés

portables, les systèmes automobile et les avions.

Egalement fondamental à l’évolution commerciale de

cette technologie, l’apparition de marchés émergents

comme les récepteurs AV multicanaux, les téléviseurs

LCD et Plasma, ainsi que tous les équipements

portables audio/vidéo fonctionnant sur batterie, les

téléphones mobiles, les systèmes de navigation par

satellite, les équipements médicaux tel que prothèses

auditives et enfin, et non des moindres, les systèmes

audio automobile haut de gamme. Tous ces marchés

nécessitent un petit facteur de forme pour être adaptés

dans des boîtiers miniatures mais élégants. Leur

rendement très efficace, permet une bonne gestion

thermique, d’avoir une alimentation par batterie et un

refroidissement pour les applications où la température

ambiante est élevée. Dans tous ces domaines, la classe

D bénéficie d’un avantage très évident sur les autres

solutions linéaires présentes sur le marché. Cette

technologie offre un rendement proche de 100% ce

qui constitue un atout de plus en plus recherché pour

les prochaines générations d’applications qui souhaite

répondre à la tendance mondiale d’économiser

l’énergie.

Texas Instruments (TI) est reconnu par l’industrie

comme un fabricant majeur de chipsets (ensembles de

circuits intégrés) classe D, qui propose des circuits avec

des niveaux de puissance variés et se spécialise dans

le secteur de l’électronique grand public (téléviseurs à

écran plat, périphériques informatiques, équipement

portable et systèmes audio Automobile et amplificateurs

Depuis près d’un siècle, les amplificateurs linéaires dominent le marché. Depuis l’apparition des amplis à tubes, puis

l’intégration des premiers transistors à la fin des années 1950, le principe de base de leur conception n’a pas beaucoup

changé et même de nos jours certains utilisateurs, essentiellement des musiciens, préfèrent encore la sonorité des bons

vieux amplis à tubes en raison de la qualité de leurs harmoniques et des spécificités de saturation douce. Néanmoins,

les limites de l’architecture d’un amplificateur linéaire traditionnel et sa technologie de base continuent à contribuer

au succès et à l’évolution des

amplificateurs.

Article présenté par

Texas Instruments

19

de puissance externes). Pour répondre à ces marchés,

TI a développé plusieurs familles d’amplificateurs

classe D avec des entrées analogiques et numériques.

Pour le marché des appareils portables, la famille

TPA2xxx, propose un amplificateur à entrée analogique

qui domine le secteur en termes de performance audio,

rendement, taille et coût de la solution. Des versions

mono et stéréo sont disponibles, avec des puissances

de 1W à 2,75W et une alimentation allant de 1,8V

à 5,5V. Au coeur du marché des téléviseurs à écran

plat, la famille TPA3xxx supporte tous les niveaux de

puissance (de 5W à 40W), options à entrée analogique

et numérique, terminaison simple et sortie « à charge

montée en pont » (BTL – bridge-tied load).

Pour le marché des récepteurs AV, TI offre une

technologie d’amplificateur audio à entrée PurePass

Digital™ exclusive, d’une puissance de 10 à 300W par

voie. Le TAS5261 monopuce offre en classe D le niveau

de puissance le plus élevé et délivre 110dB, un rapport

Signal/bruit pour une netteté acoustique ultime dans

les applications audio domestiques. Il envoie 300W

dans une enceinte de 4 Ohms (10% THD+N) et peut

restituer 125W en 8 Ohms, à moins de 0,09% THD+N

avec 95% de rendement. Membre de la famille des

amplificateurs de puissance PurePath Digital™ de

TI, il offre une capacité de gestion de puissance et de

courant incomparable.

Les nouveaux amplificateurs numériques pour

l’automobile de TI sont des amplificateurs audio

numériques de classe D, à 4 voies, ultra efficaces. Avec

des niveaux de puissance modérés, les amplificateurs

de classe A/B fournissent, au mieux, un rendement

de 40 à 50% (25% dans certains cas). Avec les

amplificateurs TAS54x4, TI offre 90% de rendement

énergétique à des niveaux d’écoute normaux pour

les systèmes audio sur le segment automobile.

Comparativement, deux amplificateurs TAS54x4

peuvent fournir huit voies tout en générant moins de

chaleur qu’un système basé sur 4 voies en classe A/B,

permettant une toute nouvelle catégorie de systèmes

audio 8 voies économiques, qui sont plus légers, plus

petits et moins gourmands en énergie que les systèmes

existants. De plus, les nouveaux amplificateurs

numériques de TI peuvent aussi être utilisés avec des

enceintes 2 Ohms pour offrir deux fois la puissance

de sortie qu’un amplificateur AB dans des enceintes

4 Ohms tout en générant moins de chaleur.

Electrometer/High Resistance Meter

Simplifies measuring high resistances and the resistivity of insulating materials

Simplifies measuring high resistances and the resistivity of insulating materials

LOW LEVEL MEASURE & SOURCE

A Greater Measure of Confidence

www.keithley.com

1.888.KEITHLEY (U.S. only)

6517B Electrometer/High Resistance Meter

produces a highly repeatable, accurate measurement

of resistance (or resistivity) by the seventh

reversal on most materials (i.e., by discarding the

first three readings). For example, a 1mm-thick

sample of 1014W-cm material can be measured

with 0.3% repeatability in the Model 8009 test

fixture, provided the background current changes

less than 200fA over a 15-second period.

Simple DMM-like Operation

The Model 6517B is designed for easy, DMM-like

operation via the front panel, with single-button

control of important

functions such as resistance

measurement. It can also be controlled via

a built-in IEEE-488 interface,

which makes it

possible to program all functions

over the bus

through a computer controller.

High Accuracy High Resistance

Measurements

The Model 6517B offers a number of features

and capabilities

that help ensure the accuracy of

high resistance measurement

applications. For

example, the built-in voltage

source simplifies

determining the relationship

between an insulator’s

resistivity and the level of source voltage

used. It is well suited

for capacitor leakage and

insulation resistance measurements,

tests of the

surface insulation

resistance

of printed circuit

boards, voltage coefficient testing

of resistors,

and diode leakage characterization.

Temperature and Humidity Stamping

Humidity and temperature can influence the

resistivity

values of materials significantly. To

help you make accurate

comparisons of readings

acquired under

varying conditions, the Model

6517B offers a built-in type K thermocouple

and

an optional Model 6517-RH Relative Humidity

Probe. A built-in data storage buffer

allows

recording and recalling readings

stamped with

the time, temperature,

and relative humidity at

which they were acquired.

Accessories Extend

Measurement Capabilities

A variety of optional accessories can be used

to extend the Model 6517B’s applications and

enhance its performance.

Scanner Cards. Two scanner

cards are available

to simplify scanning

multiple signals. Either

card can be easily inserted in the option slot of

the instrument’s

back panel. The Model 6521

Scanner

Card offers ten channels of low-level

current

scanning. The Model 6522 Scanner Card

provides

ten channels of high impedance voltage

switching or low current switching.

Test Fixture. The Model 8009 Resistivity

Chamber is a guarded

test fixture for measuring

volume

and surface

resistivities of sample

materials.

It has stainless-

steel electrodes

built

to ASTM standards.

The fixture’s electrode

dimensions are pre-programmed

into the Model

6517B, so there’s no need to calculate those

values then enter them manually.

This accessory

is designed to protect you from contact with

potentially hazardous voltages —opening the lid

of the chamber

automatically turns off the Model

6517B’s voltage

source.

Applications

The Model 6517B is well suited for low current

and high impedance voltage, resistance, and

charge measurements

in areas of research

such

as physics, optics, and materials

science. Its

extremely low voltage burden

makes it particularly

appropriate for use in solar cell applications,

and its built-in voltage source and low

current sensitivity make it an excellent solution

for high resistance measurements of nanomaterials

such as polymer based nanowires. Its high

speed and ease of use also make it an excellent

choice for quality control, product engineering,

and production test applications

involving leakage,

breakdown, and resistance testing. Volume

and surface

resistivity measurements on nonconductive

materials

are particularly enhanced

by the Model 6517B’s voltage reversal method.

The Model 6517B is also well suited for electrochemistry

applications such as ion selective electrode

and pH measurements, conductivity cells,

and potentiometry.

Model 6517B Enhancements

The Model 6517B is an updated version, replacing

the earlier Model 6517A, which was introduced

in 1996. Software applications created

for the Model 6517A using SCPI commands can

run without modifications on the Model 6517B.

However, the Model 6517B does offer some

useful enhancements to the earlier design. Its

internal battery-backed memory buffer can now

store up to 50,000 readings, allowing users to log

test results for longer periods and to store more

data associated with those readings. The new

model also provides faster reading rates to the

internal buffer (up to 425 readings/second)

and

to external memory via the IEEE bus (up to 400

readings/second).

Several connector modifications

have been incorporated to address modern

connectivity and safety requirements.

Ordering Information

6517B Electrometer/High

Resistance Meter

Accessories Supplied

237-AL G-2 Low Noise

Triax Cable, 3-slot Triax to

Alligator Clips, 2m (6.6 ft)

8607 Safety High Voltage

Dual Test Leads

6517-TP Thermocouple Bead Probe

CS-1305 Interlock Connector

ACCESSOR IES AVAILABL E

CABL ES

6517B-ILC-3 Interlock Cable

7007-1 Shielded IEEE-488 Cable, 1m (3.2 ft)

7007-2 Shielded IEEE-488 Cable, 2m (6.5 ft)

7009-5 RS-232 Cable

7078-TRX-3 Low Noise Triax Cable, 3-Slot Triax Connectors,

0.9m (3 ft)

7078-TRX-10 Low Noise Triax Cable, 3-Slot Triax Connectors,

3m (10 ft)

7078-TRX-20 Low Noise Triax Cable, 3-Slot Triax Connectors,

6m (20 ft)

8501-1 Trigger Link Cable, 1m (3.3 ft)

8501-2 Trigger Link Cable, 2m (6.6 ft)

8503 Trigger Link Cable to 2 male BNCs, 1m (3.3 ft)

8607 1kV Source Banana Cables

PROBES

6517-RH Humidity Probe with Extension Cable

6517-TP Temperature Bead Probe (included with 6517B)

TEST FIXTUR E

8009 Resistivity Test Fixture

Othe r

CS-1305 Interlock Connector

ADAPTERS

237-BNC-TRX Male BNC to 3-Lug Female Triax Adapter

237-TRX-NG Triax Male-Female Adapter with Guard

Disconnected

237-TRX-T 3-Slot Male Triax to Dual 3-Lug Female Triax

Tee Adapter

237-TRX-TBC 3-Lug Female Triax Bulkhead Connector

(1.1kV rated)

7078-TRX-BNC 3-Slot Male Triax to BNC Adapter

7078-TRX-GND 3-Slot Male Triax to BNC Adapter with guard

removed

7078-TRX-TBC 3-Lug Female Triax Bulkhead Connector

with Cap

RA CK MOUNT KITS

4288-1 Single Fixed Rack Mounting Kit

4288-2 Dual Fixed Rack Mounting Kit

Sc anne r Cards

6521 Low Current Scanner Card

6522 Voltage/Low Current Scanner Card

GPIB Interfaces

KPCI-488LPA IEEE-488 Interface/Controller for the PCI Bus

KUSB-488B IEEE-488 USB-to-GPIB Interface Adapter

Simplifies measuring high resistances and the resistivity of insulating materials

LOW LEVEL MEASURE & SOURCE

www.keithley.com

1.888.KEITHLEY (U.S. only)

A Greater Measure of Confidence

6517B Electrometer/High Resistance Meter

VOL TS Acc uracy Tempe rature

(1 Year)1 Coefficient

5½-Digit 18°–28°C 0°–18°C & 28°–50°C

Range Re soluti on ±(%rdg+counts) ±(%rdg+counts)/°C

2 V 10 μV 0.025 + 4 0.003 + 2

20 V 100 μV 0.025 + 3 0.002 + 1

200 V 1 mV 0.06 + 3 0.002 + 1

NMRR: 2V and 20V ranges >60dB, 200V range >55dB. 50Hz or 60Hz2.

CMRR: >120dB at DC, 50Hz or 60Hz.

INPUT IMPEDANCE: >200TW in parallel with 20pF, <2pF guarded (1MW with

zero check on).

SMALL SIGNAL BANDWIDTH AT PREAMP OUTPUT: Typically 100kHz (–3dB).

Note s

1. When properly zeroed, 5½-digit, 1 PLC (power line cycle), median filter on, digital filter

= 10 readings.

2. Line sync on.

AMPS Acc uracy Tempe rature

(1 Year)1 Coefficient

5½-Digit 18°–28°C 0°–18°C & 28°–50°C

Range Re soluti on ±(%rdg+counts) ±(%rdg+counts)/°C

20 pA 100 aA 2 1 + 30 0.1 + 5

200 pA 1 fA 2 1 + 5 0.1 + 1

2 nA 10 fA 0.2 + 30 0.1 + 2

20 nA 100 fA 0.2 + 5 0.03 + 1

200 nA 1 pA 0.2 + 5 0.03 + 1

2 μA 10 pA 0.1 + 10 0.005 + 2

20 μA 100 pA 0.1 + 5 0.005 + 1

200 μA 1 nA 0.1 + 5 0.005 + 1

2 mA 10 nA 0.1 + 10 0.008 + 2

20 mA 100 nA 0.1 + 5 0.008 + 1

INPUT BIAS CURRENT: <3fA at Tcal . Temperature coefficient = 0.5fA/°C,

20pA range.

INPUT BIAS CURRENT NOISE: <750aA p-p (capped input), 0.1Hz to 10Hz bandwidth,

damping on. Digital filter = 40 readings, 20pA range.

INPUT VOLTAGE BURDEN at Tcal ±1°C:

<20μV on 20pA, 2nA, 20nA, 2μA, and 20μA ranges.

<100μV on 200pA, 200nA, and 200μA ranges.

<2mV on 2mA range. <5mV on 20mA range.

TEMPERATURE COEFFICIENT OF INPUT VOLTAGE BURDEN: <10μV/°C on pA,

nA, and μA ranges.

PREAMP SETTLING TIME (to 10% of final value) Typical: 0.5sec (damping off)

2.0 sec (damping on) on pA ranges. 15msec on nA ranges damping off, 1msec on

μA ranges damping off. 500μsec on mA ranges damping off.

NMRR: >60dB on all ranges at 50Hz or 60Hz3.

Note s

1. When properly zeroed, 5½-digit, 1PLC (power line cycle), median filter on,

digital filter = 10 readings.

2. aA = 10–18A, fA = 10–15A.

3. Line sync on.

OHMS (Normal Method)

Tempe rature Acc uracy 1 Coefficient

(10–100% Range) (10–100% Range)

5½-Digit 18°–28°C (1 Year) 0°–18°C & 28°–50°C Auto Amp s

Range Re soluti on ±(% rdg+counts) ±(% rdg+counts) V Source R ange

2 MW 10 W 0.125 + 1 0.01 + 1 40 V 200 μA

20 MW 100 W 0.125 + 1 0.01 + 1 40 V 20 μA

200 MW 1 kW 0.15 + 1 0.015 + 1 40 V 2 μA

2 GW 10 kW 0.225 + 1 0.035 + 1 40 V 200 nA

20 GW 100 kW 0.225 + 1 0.035 + 1 40 V 20 nA

200 GW 1 MW 0.35 + 1 0.110 + 1 40 V 2 nA

2 TW 10 MW 0.35 + 1 0.110 + 1 400 V 2 nA

20 TW 100 MW 1.025 + 1 0.105 + 1 400 V 200 pA

200 TW 1 GW 1.15 + 1 0.125 + 1 400 V 20 pA

Note s

1. Specifications are for auto V-source ohms, when properly zeroed, 5½-digit, 1PLC, median filter on, digital filter = 10 readings. If

user selectable voltage is required, use manual mode. Manual mode displays resistance (up to 1018W) calculated from measured

current. Accuracy is equal to accuracy of V-source plus accuracy of selected Amps range. PREAMP SETTLING TIME: Add voltage source settling time to preamp settling time in Amps specification.

Ranges over 20GW require additional settling based on the characteristics of the load.

OHMS (Alte rnating Polarity Meth od)

The alternating polarity sequence compensates for the background (offset) currents of the material or device

under test. Maximum tolerable offset up to full scale of the current range used.

Using Keithley 8009 fixture

repeatabilit y: DIBG × R/VALT + 0.1% (1σ) (instrument temperature constant ±1°C).

ACCURACY: (VSRCErr + IMEASErr × R)/VALT

where: DIBG is a measured, typical background current noise from the sample and fixture.

VALT is the alternating polarity voltage used.

VSRCErr is the accuracy (in volts) of the voltage source using VALT as the setting.

IMEASErr is the accuracy (in amps) of the ammeter using VALT /R as the reading.

VOL TAGE SOUR CE Tempe rature

Acc uracy (1 Year) Coefficient

5½-Digit 18°–28°C 0°–18°C & 28°–50°C

Range Re soluti on ±(% setting + offset) ±(% setting+offset)/°C

100 V 5 mV 0.15 + 10 mV 0.005 + 1 mV

1000 V 50 mV 0.15 + 100 mV 0.005 + 10 mV

MAXIMUM OUTPUT CURRENT:

100V Range: ±10mA, hardware short circuit protection at <14mA.

1000V Range: ±1mA, hardware short circuit protection at <1.4mA.

SETTLING TIME:

100V Range: <8ms to rated accuracy.

1000V Range: <50ms to rated accuracy.

NOISE (typical):

100V Range: <2.6mV rms.

1000V Range: <2.9mV rms.

Model 6517B specifications

Model 6517B specifications

LOW LEVEL MEASURE & SOURCE

A Greater Measure of Confidence

www.keithley.com

1.888.KEITHLEY (U.S. only)

6517B Electrometer/High Resistance Meter

IEEE-488 BUS IMPLEMENTATION

IMPLEMENTATION: SCPI (IEEE-488.2, SCPI-1999.0).

TRIGGER TO READING DONE: 150ms typical, with external trigger.

RS-232 IMPLEMENTATION: Supports: SCPI 1991.0. Baud Rates: 300, 600, 1200, 2400,

4800, 9600, 19.2k, 38.4k, 57.6k, and 115.2k.

Flow Control : None, Xon/Xoff.

Connector : DB-9 TXD/RXD/GND.

GENERAL

Overrange Indication : Display reads “OVERFLOW” for readings >105% of range. The

display reads “OUT OF LIMIT” for excesive overrange conditions.

RANGING: Automatic or manual.

CONVERSION TIME: Selectable 0.01PLC to 10PLC.

MAXIMUM INPUT: 250V peak, DC to 60Hz sine wave; 10sec per minute maximum on

mA ranges.

MAXIMUM COMMON MODE VOLTAGE (DC to 60Hz sine wave): Electrometer, 500V peak;

V Source, 750V peak.

ISOLATION (Meter COMMON to chassis): >1010W, <500pF.

INPUT CONNECTOR: Three lug triaxial on rear panel.

2V ANALOG OUTPUT: 2V for full range input. Non-inverting in Volts mode, inverting when

measuring Amps, Ohms, or Coulombs. Output impedance 10kW.

PREAMP OUTPUT: Provides a guard output for Volts measurements. Can be used as an

inverting output or with external feedback in Amps and Coulombs modes.

EXTERNAL TRIGGER: TTL compatible External Trigger and Electrometer

Complete.

GUARD: Switchable voltage guard available.

DIGITAL I/O AND TRIGGER LINE: Available, see manual for usage.

EMC: Conforms to European Union Directive 89/336/EEC, EN 61326-1.

Safet y: Conforms to European Union Directive 73/23/EEC, EN 61010-1.

READING STORAGE: 50,000.

READING RATEs:

To Internal Buffer: 425 readings/second1.

To IEEE-488 Bus: 400 readings/second1, 2.

Bus Transfer: 3300 readings/second2.

1. 0.01PLC, digital filters off, front panel off, temperature + RH off, Line Sync off.

2. Binary transfer mode.

DIGITAL FILTER: Median and averaging.

ENVIRONMENT: Operating: 0°–50°C; relative humidity 70% non-condensing, up to 35°C.

Storage: –25° to +65°C.

Altitude : Maximum 2000 meters above sea level per EN 61010-1.

WARM-UP: 1 hour to rated accuracy (see manual for recommended procedure).

POWER: User selectable 100, 120, 220, 240VAC ±10%; 50/60Hz, 100VA max.

PHYSICAL: Case Dimensions: 90mm high × 214mm wide × 369mm deep (3½ in. × 8½ in.

× 14½ in.).

Working Dimensions: From front of case to rear including power cord and IEEE-488 connector:

15.5 inches.

Net Weight: 5.4kg (11.8 lbs.).

Shipping Weight: 6.9kg (15.11 lbs.).

COULO MBS

Acc uracy Tempe rature

(1 Year)1, 2 Coefficient

5½-Digit 18°–28°C 0°–18°C & 28°–50°C

Range Re soluti on ±(%rdg+counts) ±(%rdg+counts)/°C

2 nC 10 fC 0.4 + 5 0.04 + 3

20 nC 100 fC 0.4 + 5 0.04 + 1

200 nC 1 pC 0.4 + 5 0.04 + 1

2 μC 10 pC 0.4 + 5 0.04 + 1

Note s

1. Specifications apply immediately after charge acquisition. Add

|QAV|

(4fA + _____ ) TA

RC

where TA = period of time in seconds between the coulombs zero and measurement

and

QAV = average charge measured over TA, and RC = 300,000 typical.

2. When properly zeroed, 5½-digit, 1PLC (power line cycle), median filter on, digital filter = 10 readings.

INPUT BIAS CURRENT: <4fA at Tcal . Temperature coefficient = 0.5fA/°C, 2nC range.

TEMPERA TUR E (Thermocouple)

Acc uracy (1 Year)1

The rmocouple 18°–28°C

Type R ange ±(% rdg + °C)

K –25°C to 150°C ±(0.3% + 1.5°C)

Note s

1. Excluding probe errors, Tcal ± 5°C, 1 PLC integration time.

HUMIDITY

Acc uracy (1 Year)1

Range 18°–28°C, ±(% rdg + % RH)

0–100% ±(0.3% +0.5)

Note s

1. Humidity probe accuracy must be added. This is ±3% RH for Model 6517-RH, up to 65°C probe environment,

not to exceed 85°C.

Service s Av ailable

6517B-3Y-EW 1-year factory warranty extended to 3 years from date of shipment

C/6517B-3Y-ISO 3 (ISO-17025 accredited) calibrations within 3 years of purchase*

*Not available in all countries

SMBJ

Transil™

Features

■ Peak pulse power:

– 600 W (10/1000 μs)

– 4 kW (8/20 μs)

■ Stand off voltage range: from 5 V to 188 V

■ Unidirectional and bidirectional types

■ Low leakage current:

– 0.2 μA at 25 °C

– 1 μA at 85 °C

■ Operating Tj max: 150 °C

■ High power capability at Tj max:

– 515 W (10/1000 μs)

■ JEDEC registered package outline

Complies with the following standards

■ IEC 61000-4-2 level 4:

– 15 kV (air discharge)

– 8 kV (contact discharge)

■ IEC 61000-4-5

■ MIL STD 883G, method 3015-7 Class 3B:

– 25 kV HBM (human body model)

■ Resin meets UL 94, V0

■ MIL-STD-750, method 2026 soldererability

■ EIA STD RS-481 and IEC 60286-3 packing

■ IPC 7531 footprint

Description

The SMBJ Transil series has been designed to

protect sensitive equipment against electrostatic

discharges according to IEC 61000-4-2, and

MIL STD 883, method 3015, and electrical over

stress according to IEC 61000-4-4 and 5. These

devices are more generally used against surges

below 600 W (10/1000 μs).

Planar technology makes these devices suitable

for high-end equipment and SMPS where low

leakage current and high junction temperature are

required to provide reliability and stability over

time.

SMBJ are packaged in SMB (SMB footprint in

accordance with IPC 7531 standard).

TM: Transil is a trademark of STMicroelectronics

K

A

Unidirectional Bidirectional

SMB

(JEDEC DO-214AA)

www.st.com

Characteristics SMBJ

2/10 Doc ID 5616 Rev 10

1 Characteristics

Figure 1. Electrical characteristics - definitions

Figure 2. Pulse definition for electrical characteristics

Table 1. Absolute maximum ratings (Tamb = 25 °C)

Symbol Parameter Value Unit

PPP Peak pulse power dissipation (1) Tj initial = Tamb 600 W

Tstg Storage temperature range -65 to +150 °C

Tj Operating junction temperature range -55 to +150 °C

TL Maximum lead temperature for soldering during 10 s. 260 °C

1. For a surge greater than the maximum values, the diode will fail in short-circuit.

Table 2. Thermal resistances

Symbol Parameter Value Unit

Rth(j-l) Junction to leads 20 °C/W

Rth(j-a) Junction to ambient on recommended pad layout 100 °C/W

VCLVBR VRM

IRM

IR

IPP

V

I

IRM

IR

IPP

VRMVBR VCL

V CLVBR VRM

IRM

IR

IPP

V

I

IF

VF

Unidirectional

Bidirectional

Symbol Parameter

V Stand-off voltage

V Breakdown voltage

V Clamping voltage

I Leakage current @ V

I Peak pulse current

T Voltage temperature coefficient

V Forward voltage drop

R Dynamic resistance

RM

BR

CL

RM RM

PP

F

D

α

Repetitive pulse current

tr = rise time (μs)

tp = pulse duration time (μs)

tp

t

tr

% Ipp

100

50

0

SMBJ Characteristics

Doc ID 5616 Rev 10 3/10

Table 3. Electrical characteristics - parameter values (Tamb = 25 °C)

Order code

IRM max@VRM VBR @IR (1) VCL @IPP

10/1000 μs

RD (2)

10/1000 μs

VCL @IPP

8/20 μs

RD (2)

8/20 μs αT (3)

25 °C 85 °C min typ max max max

μA V V mA V A(4) Ω V A(4) Ω 10-4/ °C

SMBJ5.0A/CA 20 50 5.0 6.4 6.74 10 9.2 68 0.031 13.4 298 0.021 5.7

SMBJ6.0A/CA 20 50 6.0 6.7 7.05 10 10.3 61 0.048 13.7 290 0.022 5.9

SMBJ6.5A/CA 20 50 6.5 7.2 7.58 10 11.2 56 0.058 14.5 276 0.024 6.1

SMBJ8.5A/CA 20 50 8.5 9.4 9.9 1 14.4 41.7 0.096 19.5 205 0.044 7.3

SMBJ10A/CA 0.2 1 10 11.1 11.7 1 17 37 0.127 21.7 184 0.051 7.8

SMBJ12A/CA 0.2 1 12 13.3 14 1 19.9 31 0.168 25.3 157 0.068 8.3

SMBJ13A/CA 0.2 1 13 14.4 15.2 1 21.5 29 0.191 27.2 147 0.076 8.4

SMBJ15A/CA 0.2 1 15 16.7 17.6 1 24.4 25.1 0.236 32.5 123 0.114 8.8

SMBJ16A/CA 0.2 1 16 17.8 18.7 1 26 23.1 0.276 34.4 116 0.127 8.8

SMBJ18A/CA 0.2 1 18 20.0 21.1 1 29.2 21.5 0.328 39.3 102 0.168 9.2

SMBJ20A/CA 0.2 1 20 22.2 23.4 1 32.4 19.4 0.404 42.8 93 0.196 9.4

SMBJ22A/CA 0.2 1 22 24.4 25.7 1 35.5 17.7 0.481 48.3 83 0.257 9.6

SMBJ24A/CA 0.2 1 24 26.7 28.1 1 38.9 16 0.587 50 80 0.256 9.6

SMBJ26A/CA 0.2 1 26 28.9 30.4 1 42.1 14.9 0.683 53.5 75 0.288 9.7

SMBJ28A/CA 0.2 1 28 31.1 32.7 1 45.4 13.8 0.802 59 68 0.363 9.8

SMBJ30A/CA 0.2 1 30 33.3 35.1 1 48.4 13 0.888 64.3 62 0.443 9.9

SMBJ33A/CA 0.2 1 33 36.7 38.6 1 53.3 11.8 1.08 69.7 57 0.512 10.0

SMBJ36A/CA 0.2 1 36 40.0 42.1 1 58.1 10.3 1.35 76 52 0.611 10.0

SMBJ40A/CA 0.2 1 40 44.4 46.7 1 64.5 9.7 1.59 84 48 0.728 10.1

SMBJ48A/CA 0.2 1 48 53.3 56.1 1 77.4 8.1 2.28 100 40 1.03 10.3

SMBJ58A/CA 0.2 1 58 64.4 67.8 1 93.6 6.7 3.34 121 33 1.51 10.4

SMBJ70A/CA 0.2 1 70 77.8 81.9 1 113 5.5 4.91 146 27 2.22 10.5

SMBJ85A/CA 0.2 1 85 94 99 1 137 4.6 7.18 178 22.5 3.29 10.6

SMBJ100A/CA 0.2 1 100 111 117 1 162 3.8 10.3 212 19 4.69 10.7

SMBJ130A/CA 0.2 1 130 144 152 1 209 3 16.5 265 15 7.03 10.8

SMBJ154A/CA 0.2 1 154 171 180 1 246 2.4 23.8 317 12.6 10.2 10.8

SMBJ170A/CA 0.2 1 170 189 199 1 275 2.2 30.0 353 11.3 12.7 10.8

SMBJ188A/CA 0.2 1 188 209 220 1 328 2 48.5 388 10.3 15.2 10.8

1. Pulse test : tp < 50 ms

2. To calculate maximum clamping voltage at other surge level,use the following formula: VCLmax = VCL - RD x (IPP - IPPappli)

where IPPappli is the surge current in the application

3. To calculate VBR or VCL versus junction temperature, use the following formulas:

VBR @ TJ = VBR @ 25°C x (1 + αT x (TJ – 25))

VCL @ TJ = VCL @ 25°C x (1 + αT x (TJ – 25))

4. Surge capability given for both directions for unidirectional and bidirectional types.

Characteristics SMBJ

4/10 Doc ID 5616 Rev 10

Figure 5. Clamping voltage versus peak pulse current (exponential waveform, maximum values)

Figure 3. Peak pulse power dissipation

versus initial junction temperature

Figure 4. Peak pulse power versus

exponential pulse duration

(Tj initial = 25 °C)

0

100

200

300

400

500

600

700

0 25 50 75 100 125 150 175

Ppp (W)

Tj(°C)

0.1

1.0

10.0

100.0

1.0E-03 1.0E-02 1.0E-01 1.0E+00 1.0E+01

PPP(kW)

Tj initial = 25 °C

tP(ms)

IPP(A)

0.1

1.0

10.0

100.0

1000.0

1 10 100 1000

10/1000 μs

Tj initial=25 °C

8/20 μs

10 ms

SMBJ5.0A

SMBJ188A

SMBJ12A

SMBJ24A

SMBJ40A

SMBJ85A

VCL(V)

SMBJ Characteristics

Doc ID 5616 Rev 10 5/10

Figure 6. Junction capacitance versus

reverse applied voltage for

unidirectional types (typical values)

Figure 7. Junction capacitance versus

reverse applied voltage for

bidirectional types (typical values)

10

100

1000

10000

1 10 100 1000

C(pF)

F=1 MHz

Vosc=30 mVRMS

Tj=25 °C

SMBJ5.0A

SMBJ12A

SMBJ24A

SMBJ40A

SMBJ85A

VR(V) SMBJ188A

10

100

1000

10000

1 10 100 1000

C(pF)

F=1 MHz

Vosc=30 mVRMS

Tj=25 °C

SMBJ5.0CA

SMBJ12CA

SMBJ24CA

SMBJ40CA

SMBJ85CA

SMBJ188CA

VR(V)

Figure 8. Peak forward voltage drop

versus peak forward current

(typical values)

Figure 9. Relative variation of thermal

impedance, junction to ambient,

versus pulse duration

Figure 10. Thermal resistance, junction to

ambient, versus copper surface

under each lead

Figure 11. Leakage current versus junction

temperature (typical values)

IFM(A)

1.0E-02

1.0E-01

1.0E+00

1.0E+01

1.0E+02

0.0 0.5 1.0 1.5 2.0 2.5 3.0

Tj =25 °C

Tj =125 °C

VFM(V)

0.01

0.10

1.00

1.0E-03 1.0E-02 1.0E-01 1.0E+00 1.0E+01 1.0E+02 1.0E+03

Zth(j-a) /Rth(j-a)

tP(s)

Recommended pad layout

PCB FR4, copper thickness = 35 μm

0

10

20

30

40

50

60

70

80

90

100

110

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

R (°C/W) th(J-A)

SCU(cm²)

PCB FR4, copper thickness = 35 μm

1.E-01

1.E+00

1.E+01

1.E+02

1.E+03

25 50 75 100 125 150

VR=VRM

VRM ≥ 10 V

VR=VRM

VRM< 10 V

Tj(°C)

IR (nA)

Ordering information scheme SMBJ

6/10 Doc ID 5616 Rev 10

2 Ordering information scheme

Figure 12. Ordering information scheme

SM B J 85 CA - TR

Surface mount

Peak pulse power

B = 600 WTransil in SMB

Stand off voltage

85 = 85 V

Type

A = Unidirectional

CA = Bidirectional

Delivery mode

TR = Tape and reel

SMBJ Package information

Doc ID 5616 Rev 10 7/10

3 Package information

● Case: JEDEC DO-214AA molded plastic over planar junction

● Terminals: solder plated - solderable per MIL-STD-750, Method 2026

● Polarity: for unidirectional types the band indicates cathode

● Flammability: epoxy is rated UL94V-0

● RoHS package

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

Table 4. SMB dimensions

Ref.

Dimensions

Millimeters Inches

Min. Max. Min. Max.

A1 1.90 2.45 0.075 0.096

A2 0.05 0.20 0.002 0.008

b 1.95 2.20 0.077 0.087

c 0.15 0.40 0.006 0.016

D 3.30 3.95 0.130 0.156

E 5.10 5.60 0.201 0.220

E1 4.05 4.60 0.159 0.181

L 0.75 1.50 0.030 0.059

Figure 13. Footprint dimensions

in mm (inches)

Figure 14. Marking layout(1)

1. Marking layout can vary according to assembly location.

E

C

L

E1

D

A1

A2

b

2.60

5.84

1.62

2.18

1.62

(0.064) (0.102)

(0.23)

(0.064)

(0.086)

y w w

e

z

x x x

e: ECOPACK compliance

XXX: Marking

Z: Manufacturing location

Y: Year

WW: week

Cathode bar ( unidirectional devices only )

Package information SMBJ

8/10 Doc ID 5616 Rev 10

Table 5. Marking

Order code Marking Order code Marking

SMBJ5.0A-TR BUZ SMBJ5.0CA-TR BBZ

SMBJ6.0A-TR BUA SMBJ6.0CA-TR BBA

SMBJ6.5A-TR BUB SMBJ6.5CA-TR BBB

SMBJ8.5A-TR BUC SMBJ8.5CA-TR BBC

SMBJ10A-TR BUD SMBJ10CA-TR BBD

SMBJ12A-TR BUE SMBJ12CA-TR BBE

SMBJ13A-TR BUF SMBJ13CA-TR BBF

SMBJ15A-TR BUG SMBJ15CA-TR BBG

SMBJ16A-TR CUG SMBJ16CA-TR CBG

SMBJ18A-TR BUH SMBJ18CA-TR BBH

SMBJ20A-TR BUI SMBJ20CA-TR BBI

SMBJ22A-TR BVA SMBJ22CA-TR CBH

SMBJ24A-TR BUJ SMBJ24CA-TR BBJ

SMBJ26A-TR BUK SMBJ26CA-TR BBK

SMBJ28A-TR BUL SMBJ28CA-TR BBL

SMBJ30A-TR BUM SMBJ30CA-TR BBM

SMBJ33A-TR BUN SMBJ33CA-TR BBN

SMBJ36A-TR CUN SMBJ36CA-TR CBN

SMBJ40A-TR CUJ SMBJ40CA-TR CBJ

SMBJ43A-TR CUW SMBJ43CA-TR CBW

SMBJ48A-TR BUW SMBJ48CA-TR BBW

SMBJ58A-TR BUO SMBJ58CA-TR BBO

SMBJ70A-TR CUM SMBJ70CA-TR CBM

SMBJ85A-TR BUQ SMBJ85CA-TR BBQ

SMBJ100A-TR CUQ SMBJ100CA-TR CBQ

SMBJ130A-TR BUS SMBJ130CA-TR BBS

SMBJ154A-TR BUT SMBJ154CA-TR BBT

SMBJ170A-TR BUU SMBJ170CA-TR BBU

SMBJ188A-TR BUV SMBJ188CA-TR BBV

SMBJ Ordering information

Doc ID 5616 Rev 10 9/10

4 Ordering information

5 Revision history

Table 6. Order codes

Order code Marking Package Weight Base qty Delivery mode

SMBJxxxA/CA-TR(1)

1. Where xxx is nominal value of VBR and A or CA indicates unidirectional or bidirectional version. See

Table 3 for list of available devices and their order codes

See Table 5 on page 8 SMB 0.11 g 2500 Tape and reel

Table 7. Document revision history

Date Revision Changes

Oct-2001 4 Previous issue

10-Feb-2005 5

Reformatted to current template. Added directional (uni and bi)

indications to graphics. Added ECOPACK statement.

16-Nov-2006 6 Add part numbers SMBJ36A-TR and SMBJ36CA-TR in Table 3.

14-May-2009 7

Reformatted to current standards. Updated ECOPACK

statement. Added part number SMBJ43CA/A

17-Sep-2009 8 Document updated for low leakage current.

09-Jul-2010 9 Changed timescale in Figure 9.

20-Oct-2010 10 Updated Figure 13.

SMBJ

10/10 Doc ID 5616 Rev 10

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

CC2430

CC2430 Data Sheet (rev. 2.1) SWRS036F Page 1 of 211

A True System-on-Chip solution for 2.4 GHz IEEE 802.15.4 / ZigBee®

Applications

• 2.4 GHz IEEE 802.15.4 systems

• ZigBee® systems

• Home/building automation

• Industrial Control and Monitoring

• Low power wireless sensor networks

• PC peripherals

• Set-top boxes and remote controls

• Consumer Electronics

Product Description

The CC2430 comes in three different flash

versions: CC2430F32/64/128, with 32/64/128

KB of flash memory respectively. The CC2430

is a true System-on-Chip (SoC) solution

specifically tailored for IEEE 802.15.4 and

ZigBee® applications. It enables ZigBee®

nodes to be built with very low total bill-ofmaterial

costs. The CC2430 combines the

excellent performance of the leading CC2420

RF transceiver with an industry-standard

enhanced 8051 MCU, 32/64/128 KB flash

memory, 8 KB RAM and many other powerful

features. Combined with the industry leading

ZigBee® protocol stack (Z-Stack™) from Texas

Instruments, the CC2430 provides the market’s

most competitive ZigBee® solution.

The CC2430 is highly suited for systems where

ultra low power consumption is required. This

is ensured by various operating modes. Short

transition times between operating modes

further ensure low power consumption.

Key Features

• RF/Layout

o 2.4 GHz IEEE 802.15.4 compliant RF

transceiver (industry leading CC2420 radio

core)

o Excellent receiver sensitivity and robustness to

interferers

o Very few external components

o Only a single crystal needed for mesh network

systems

o RoHS compliant 7x7mm QLP48 package

• Low Power

o Low current consumption (RX: 27 mA, TX: 27

mA, microcontroller running at 32 MHz)

o Only 0.5 μA current consumption in powerdown

mode, where external interrupts or the RTC

can wake up the system

o 0.3 μA current consumption in stand-by mode,

where external interrupts can wake up the

system

o Very fast transition times from low-power

modes to active mode enables ultra low

average power consumption in low dutycycle

systems

o Wide supply voltage range (2.0V - 3.6V)

• Microcontroller

o High performance and low power 8051

microcontroller core

o 32, 64 or 128 KB in-system programmable

flash

o 8 KB RAM, 4 KB with data retention in all

power modes

o Powerful DMA functionality

o Watchdog timer

o One IEEE 802.15.4 MAC timer, one general

16-bit timer and two 8-bit timers

o Hardware debug support

• Peripherals

o CSMA/CA hardware support.

o Digital RSSI / LQI support

o Battery monitor and temperature sensor

o 12-bit ADC with up to eight inputs and

configurable resolution

o AES security coprocessor

o Two powerful USARTs with support for several

serial protocols

o 21 general I/O pins, two with 20mA sink/source

capability

• Development tools

o Powerful and flexible development tools

available

Not Recommended for New Designs

CC2430

CC2430 Data Sheet (rev. 2.1) SWRS036F Page 2 of 211

Table Of Contents

1 ABBREVIATIONS................................................................................................................................ 5

2 REFERENCES....................................................................................................................................... 7

3 REGISTER CONVENTIONS .............................................................................................................. 8

4 FEATURES EMPHASIZED ................................................................................................................ 9

4.1 HIGH-PERFORMANCE AND LOW-POWER 8051-COMPATIBLE MICROCONTROLLER ............................... 9

4.2 UP TO 128 KB NON-VOLATILE PROGRAM MEMORY AND 2 X 4 KB DATA MEMORY ............................ 9

4.3 HARDWARE AES ENCRYPTION/DECRYPTION ....................................................................................... 9

4.4 PERIPHERAL FEATURES......................................................................................................................... 9

4.5 LOW POWER.......................................................................................................................................... 9

4.6 IEEE 802.15.4MAC HARDWARE SUPPORT........................................................................................... 9

4.7 INTEGRATED 2.4GHZ DSSS DIGITAL RADIO ........................................................................................ 9

5 ABSOLUTE MAXIMUM RATINGS ................................................................................................ 10

6 OPERATING CONDITIONS............................................................................................................. 10

7 ELECTRICAL SPECIFICATIONS .................................................................................................. 11

7.1 GENERAL CHARACTERISTICS .............................................................................................................. 12

7.2 RF RECEIVE SECTION ......................................................................................................................... 13

7.3 RF TRANSMIT SECTION....................................................................................................................... 13

7.4 32 MHZ CRYSTAL OSCILLATOR.......................................................................................................... 14

7.5 32.768 KHZ CRYSTAL OSCILLATOR.................................................................................................... 14

7.6 32 KHZ RC OSCILLATOR..................................................................................................................... 15

7.7 16 MHZ RC OSCILLATOR ................................................................................................................... 15

7.8 FREQUENCY SYNTHESIZER CHARACTERISTICS ................................................................................... 16

7.9 ANALOG TEMPERATURE SENSOR........................................................................................................ 16

7.10 ADC ................................................................................................................................................... 16

7.11 CONTROL AC CHARACTERISTICS........................................................................................................ 18

7.12 SPI AC CHARACTERISTICS ................................................................................................................. 19

7.13 DEBUG INTERFACE AC CHARACTERISTICS ......................................................................................... 20

7.14 PORT OUTPUTS AC CHARACTERISTICS............................................................................................... 21

7.15 TIMER INPUTS AC CHARACTERISTICS................................................................................................. 21

7.16 DC CHARACTERISTICS........................................................................................................................ 21

8 PIN AND I/O PORT CONFIGURATION ........................................................................................ 22

9 CIRCUIT DESCRIPTION ................................................................................................................. 24

9.1 CPU AND PERIPHERALS ...................................................................................................................... 25

9.2 RADIO ................................................................................................................................................. 26

10 APPLICATION CIRCUIT ................................................................................................................. 27

10.1 INPUT / OUTPUT MATCHING................................................................................................................. 27

10.2 BIAS RESISTORS .................................................................................................................................. 27

10.3 CRYSTAL............................................................................................................................................. 27

10.4 VOLTAGE REGULATORS ...................................................................................................................... 27

10.5 DEBUG INTERFACE.............................................................................................................................. 27

10.6 POWER SUPPLY DECOUPLING AND FILTERING...................................................................................... 28

11 8051 CPU .............................................................................................................................................. 30

11.1 8051 CPU INTRODUCTION .................................................................................................................. 30

11.2 MEMORY............................................................................................................................................. 30

11.3 CPU REGISTERS.................................................................................................................................. 42

11.4 INSTRUCTION SET SUMMARY.............................................................................................................. 44

11.5 INTERRUPTS ........................................................................................................................................ 49

12 DEBUG INTERFACE......................................................................................................................... 60

12.1 DEBUG MODE ..................................................................................................................................... 60

12.2 DEBUG COMMUNICATION ................................................................................................................... 60

12.3 DEBUG COMMANDS ............................................................................................................................ 60

12.4 DEBUG LOCK BIT................................................................................................................................ 60

12.5 DEBUG INTERFACE AND POWER MODES ............................................................................................. 64

13 PERIPHERALS................................................................................................................................... 65

Not Recommended for New Designs

CC2430

CC2430 Data Sheet (rev. 2.1) SWRS036F Page 3 of 211

13.1 POWER MANAGEMENT AND CLOCKS................................................................................................... 65

13.2 RESET ................................................................................................................................................. 71

13.3 FLASH CONTROLLER........................................................................................................................... 71

13.4 I/O PORTS............................................................................................................................................ 77

13.5 DMA CONTROLLER ............................................................................................................................ 88

13.6 16-BIT TIMER, TIMER1 ........................................................................................................................ 99

13.7 MAC TIMER (TIMER2)...................................................................................................................... 110

13.8 8-BIT TIMERS, TIMER 3 AND TIMER 4 ................................................................................................ 117

13.9 SLEEP TIMER..................................................................................................................................... 126

13.10 ADC ................................................................................................................................................. 128

13.11 RANDOM NUMBER GENERATOR ....................................................................................................... 134

13.12 AES COPROCESSOR .......................................................................................................................... 136

13.13 WATCHDOG TIMER ........................................................................................................................... 141

13.14 USART............................................................................................................................................. 143

14 RADIO................................................................................................................................................ 153

14.1 IEEE 802.15.4MODULATION FORMAT............................................................................................. 154

14.2 COMMAND STROBES ......................................................................................................................... 155

14.3 RF REGISTERS................................................................................................................................... 155

14.4 INTERRUPTS ...................................................................................................................................... 155

14.5 FIFO ACCESS .................................................................................................................................... 157

14.6 DMA ................................................................................................................................................ 157

14.7 RECEIVE MODE.................................................................................................................................. 158

14.8 RXFIFO OVERFLOW......................................................................................................................... 158

14.9 TRANSMIT MODE............................................................................................................................... 159

14.10 GENERAL CONTROL AND STATUS ...................................................................................................... 160

14.11 DEMODULATOR, SYMBOL SYNCHRONIZER AND DATA DECISION ..................................................... 160

14.12 FRAME FORMAT................................................................................................................................ 161

14.13 SYNCHRONIZATION HEADER ............................................................................................................. 161

14.14 LENGTH FIELD................................................................................................................................... 162

14.15 MAC PROTOCOL DATA UNIT ............................................................................................................. 162

14.16 FRAME CHECK SEQUENCE ................................................................................................................. 162

14.17 RF DATA BUFFERING........................................................................................................................ 163

14.18 ADDRESS RECOGNITION.................................................................................................................... 164

14.19 ACKNOWLEDGE FRAMES .................................................................................................................. 165

14.20 RADIO CONTROL STATE MACHINE ..................................................................................................... 166

14.21 MAC SECURITY OPERATIONS (ENCRYPTION AND AUTHENTICATION).............................................. 168

14.22 LINEAR IF AND AGC SETTINGS ........................................................................................................ 168

14.23 RSSI / ENERGY DETECTION.............................................................................................................. 168

14.24 LINK QUALITY INDICATION .............................................................................................................. 168

14.25 CLEAR CHANNEL ASSESSMENT......................................................................................................... 169

14.26 FREQUENCY AND CHANNEL PROGRAMMING..................................................................................... 169

14.27 VCO AND PLL SELF-CALIBRATION.................................................................................................. 169

14.28 OUTPUT POWER PROGRAMMING....................................................................................................... 170

14.29 INPUT / OUTPUT MATCHING.............................................................................................................. 170

14.30 TRANSMITTER TEST MODES ............................................................................................................. 171

14.31 SYSTEM CONSIDERATIONS AND GUIDELINES.................................................................................... 173

14.32 PCB LAYOUT RECOMMENDATION .................................................................................................... 175

14.33 ANTENNA CONSIDERATIONS............................................................................................................. 175

14.34 CSMA/CA STROBE PROCESSOR....................................................................................................... 176

14.35 RADIO REGISTERS............................................................................................................................. 183

15 VOLTAGE REGULATORS............................................................................................................. 202

15.1 VOLTAGE REGULATORS POWER-ON.................................................................................................. 202

16 EVALUATION SOFTWARE........................................................................................................... 202

17 REGISTER OVERVIEW................................................................................................................. 203

18 PACKAGE DESCRIPTION (QLP 48) ............................................................................................ 206

18.1 RECOMMENDED PCB LAYOUT FOR PACKAGE (QLP 48).................................................................... 207

18.2 PACKAGE THERMAL PROPERTIES....................................................................................................... 207

18.3 SOLDERING INFORMATION ................................................................................................................ 207

18.4 TRAY SPECIFICATION ........................................................................................................................ 207

Not Recommended for New Designs

CC2430

CC2430 Data Sheet (rev. 2.1) SWRS036F Page 4 of 211

18.5 CARRIER TAPE AND REEL SPECIFICATION.......................................................................................... 207

19 ORDERING INFORMATION......................................................................................................... 209

20 GENERAL INFORMATION........................................................................................................... 210

20.1 DOCUMENT HISTORY........................................................................................................................ 210

21 ADDRESS INFORMATION............................................................................................................ 210

22 TI WORLDWIDE TECHNICAL SUPPORT................................................................................. 210

Not Recommended for New Designs

CC2430

CC2430 Data Sheet (rev. 2.1) SWRS036F Page 5 of 211

1 Abbreviations

ADC Analog to Digital Converter

AES Advanced Encryption Standard

AGC Automatic Gain Control

ARIB Association of Radio Industries and

Businesses

BCD Binary Coded Decimal

BER Bit Error Rate

BOD Brown Out Detector

BOM Bill of Materials

CBC Cipher Block Chaining

CBC-MAC Cipher Block Chaining Message

Authentication Code

CCA Clear Channel Assessment

CCM Counter mode + CBC-MAC

CFB Cipher Feedback

CFR Code of Federal Regulations

CMOS Complementary Metal Oxide

Semiconductor

CMRR Common Mode Ratio Recjection

CPU Central Processing Unit

CRC Cyclic Redundancy Check

CSMA-CA Carrier Sense Multiple Access with

Collision Avoidance

CSP CSMA/CA Strobe Processor

CTR Counter mode (encryption)

CW Continuous Wave

DAC Digital to Analog Converter

DC Direct Current

DMA Direct Memory Access