Consent Manager Tag v2.0 (for TCF 2.0) -->

Farnell PDF

12mm Size Insulated Shaft Type Encoder Variety

EC12E Series - PDF - Farnell Element 14

12mm Size Insulated Shaft Type Encoder Variety

EC12E Series - PDF - Farnell Element 14

12mm Size Insulated Shaft Type Encoder Variety

EC12E Series - PDF - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 10-Mar-2014 15:52 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

Incremental

Type

Absolute

Type

186

Power

Push

Slide

Rotary

Encoders

Jog

Shuttle

Telephone

-hook

Detector

Vibration/

Tilt Sensors

Dual-in-line

Package Type

Multi Control

Devices

TACT

Insulated shaft type with a push-on switch and other features has a wide variety of applications.

A 12mm sized unit achieved high resolution,12- pulse /12-

detent and 24 -pulse / 24 -detent.

Used a new structure for the shaft and bushing, and achieved

a high precision, responsive system.

Also available with a 0.5mm push switch.

● Incremental type.

●

●

●

5mA 5V DC

Without detent

Other

15,000 cycles

30,000 cycles

Rating(max.)(Resistive load)

Items Specifications

Operating life

Features

Typical Specifications

Products Line

Controls for image and sound devices, including DVD

players, mini component stereos, CD players, portable audio

players and monitors.

● Controls for audio mixers and electronic instruments.

●

Applications

Products No. Drawing

No.

Minimum packing

unit(pcs.) Detent torque Resolution

Length of

operating section

(mm)

2

1,200

1

3

1

3

2

1

3

1

3

1

Vertical

Number

of detent

12

24

Without

Standard

3 to 20 mN・m

15

20

25

15

20

25

8.5

(Hollow shaft)

20

25

8.5

(Hollow shaft)

20

25

20

25 Lightest(jog)

3±2 mN・m

Standard

3 to 20 mN・m

Lightest(jog)

3±2 mN・m

Standard

25±15 mN・m

EC12E1220407

EC12E1220406

EC12E1220405

EC12E1240405

EC12E1240406

EC12E1220301

EC12E1240301

EC12E24204A2

EC12E24204A8

EC12E24204A9

EC12E2420301

EC12E24404A8

EC12E24404A6

EC12E2440301

EC12E2430404

EC12E2430401

With High Collar Type

Without ――

Push-on

switch

Travel of push-on

switch(mm)

Operating

direction

12

24

8.5

(Hollow shaft)

8.5

(Hollow shaft)

12mm Size Insulated Shaft Type Encoder Variety

EC12E Series

Lead FreeIncremental

Type

Absolute

Type

187

Power

Push

Slide

Rotary

Encoders

Jog

Shuttle

Telephone

-hook

Detector

Vibration/

Tilt Sensors

Dual-in-line

Package Type

Multi Control

Devices

TACT

5 7

3.5 15

2 3.5 surface

Mounting

ø6.6

(0.6)

(0.8)

12.4

(8.2)

14

(10.2)

13.2

4.5

ø6

3.5 LM1

5 (5) R1

(0.8)

2 3.5

ø6.8 4.5

ø6

Mounting surface

14

12.4

(8.2)

(10.2)

13.2

Products Line

With Switch Type

Products

No.

Drawing

No.

Number

of detent Resolution Length of operating

section (mm)

Vertical Without ―― 4

12

24

20

25

20

25

Standard

3 to 20 mN・m

Standard

25±15 mN・m

12

24

Without

EC12E1220801

EC12E2420802

EC12E2420801

EC12E2430804

EC12E2430803

Push-on

switch

Travel of push-on

switch(mm)

Operating

direction

Vertical 5

12

24

Standard

3 to 20 mN・m

Lightest(jog)

3±2 mN・m

Standard

3 to 20 mN・m

Lightest(jog)

3±2 mN・m

With 0.5

12

24

20

25

20

25

20

25

20

25

EC12E12244A3

EC12E12244A4

EC12E1244401

EC12E1244403

EC12E2424407

EC12E2424404

EC12E2444400

EC12E24444A3

Detent

torque

950

Minimum packing

unit (pcs.)

1,200

Minimum packing

unit (pcs.)

Products

No.

Drawing

No.

Number

of detent Resolution Length of operating

section (mm)

Push-on

switch

Travel of push-on

switch(mm) Operating

direction

Detent

torque

No nuts or washers attached. If necessary, contact us.

Note

For other products, check varieties on P.189

For other detailed specifications, see P.190

Dimensions

7.5

5

2.1

2 2

13.2

A C B

3-ø1 hole

13.2 2 2

7.5

2.1

5 A CB 3-ø1 hole

Model Style

Short shaft

No.

1

2

LM1 R1

20 7

25 12

PC board mounting hole

dimensions

(Viewed from mounting face)

Unit : mm

With Bushing Type

12mm Size Insulated Shaft Type Encoder Variety EC12E SeriesIncremental

Type

Absolute

Type

188

Power

Push

Slide

Rotary

Encoders

Jog

Shuttle

Telephone

-hook

Detector

Vibration/

Tilt Sensors

Dual-in-line

Package Type

Multi Control

Devices

TACT

Dimensions Unit : mm

LM1 R1

20 7

25 12

3.5 8.5

5

1.2 2.65

(0.6)

2

ø6

3.5

(0.8)

ø6.6

Mounting surface

14

12.4

(8.2)

ø3.1

5

(10.2)

5.2

13.2

2.1

13.2

2 2

7.5

2.1

5 A CB 3-ø1 hole

Model Style

Hollow shaft

No.

3

PC board mounting hole

dimensions

(Viewed from mounting face)

12.4

(8.2)

14

2

Mounting

surface 3.5 M9x0.75

7

3.5

5.5

LM1

4.5

ø6

(10.2)

13.2

8

1

R1

13.2

2

3-ø1

2

2.1

5

A C B

7.5

hole

With bushing

4

2.5

0.4

7

X X

Y

Locating lug detail

Y

LM1 R1

20 7

25 12

3.5 LM1

6 (5) R1

0.5

(0.8)

2

3.5

ø6.8

Switch

travel

Mounting surface

14

12.4

(8.2)

(10.2)

13.2

4.5

ø6

13.2 2 2

A C B

5

7 7.5

2.1

5-ø1 hole

With push-on switch

5

12mm Size Insulated Shaft Type Encoder Variety EC12E SeriesIncremental

Type

Absolute

Type

189

Power

Push

Slide

Rotary

Encoders

Jog

Shuttle

Telephone

-hook

Detector

Vibration/

Tilt Sensors

Dual-in-line

Package Type

Multi Control

Devices

TACT

Variety

Shaft Dimensions

Flat Type Unit : mm

With high collar type

LM1

R1

4.5

0.5

ø6

LM1 R1

17.5

20

22.5

25

5

7

7

12

30 12

3.5

4.5

ø6

1

3.5

2

5.5 LB

LM1

Mounting surface

R1

With bushing type

LM1 R1

20

25

30

35

LB

7

7

12

12

7

12

12

12

Vertical type

Detail dimensions

Except 12 detent.

Detail dimensions

12mm Size Insulated Shaft Encoders

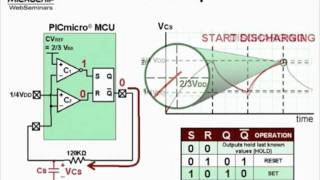

PIC24FJ256GB110 Family

Data Sheet

64/80/100-Pin,

16-Bit Flash Microcontrollers

with USB On-The-Go (OTG)

DS39897C-page 2 2009 Microchip Technology Inc.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

rfPIC and UNI/O are registered trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

MXDEV, MXLAB, SEEVAL and The Embedded Control

Solutions Company are registered trademarks of Microchip

Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified

logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, PIC32 logo, REAL ICE, rfLAB, Select Mode, Total

Endurance, TSHARC, UniWinDriver, WiperLock and ZENA

are trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2009, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2009 Microchip Technology Inc. DS39897C-page 3

PIC24FJ256GB110 FAMILY

Power Management:

• On-Chip 2.5V Voltage Regulator

• Switch between Clock Sources in Real Time

• Idle, Sleep and Doze modes with Fast Wake-up and

Two-Speed Start-up

• Run mode: 1 mA/MIPS, 2.0V Typical

• Sleep mode Current Down to 100 nA Typical

• Standby Current with 32 kHz Oscillator: 2.5 A,

2.0V typical

Universal Serial Bus Features:

• USB v2.0 On-The-Go (OTG) Compliant

• Dual Role Capable – can act as either Host or Peripheral

• Low-Speed (1.5 Mb/s) and Full-Speed (12 Mb/s) USB

Operation in Host mode

• Full-Speed USB Operation in Device mode

• High-Precision PLL for USB

• Internal Voltage Boost Assist for USB Bus Voltage

Generation

• Interface for Off-Chip Charge Pump for USB Bus

Voltage Generation

• Supports up to 32 Endpoints (16 bidirectional):

- USB Module can use any RAM location on the

device as USB endpoint buffers

• On-Chip USB Transceiver with On-Chip Voltage Regulator

• Interface for Off-Chip USB Transceiver

• Supports Control, Interrupt, Isochronous and Bulk Transfers

• On-Chip Pull-up and Pull-Down Resistors

High-Performance CPU:

• Modified Harvard Architecture

• Up to 16 MIPS Operation at 32 MHz

• 8 MHz Internal Oscillator

• 17-Bit x 17-Bit Single-Cycle Hardware Multiplier

• 32-Bit by 16-Bit Hardware Divider

• 16 x 16-Bit Working Register Array

• C Compiler Optimized Instruction Set Architecture with

Flexible Addressing modes

• Linear Program Memory Addressing, Up to 12 Mbytes

• Linear Data Memory Addressing, Up to 64 Kbytes

• Two Address Generation Units for Separate Read and

Write Addressing of Data Memory

Analog Features:

• 10-Bit, Up to 16-Channel Analog-to-Digital (A/D)

Converter at 500 ksps:

- Conversions available in Sleep mode

• Three Analog Comparators with Programmable Input/

Output Configuration

• Charge Time Measurement Unit (CTMU)

Device

Pins

Program

Memory (Bytes)

SRAM (Bytes)

Remappable Peripherals

I2C™

10-Bit A/D (ch)

Comparators

PMP/PSP

JTAG

CTMU

USBOTG

Remappable

Pins

Timers 16-Bit

Capture Input

Compare/

PWM Output

UART w/IrDA®

SPI

PIC24FJ64GB106 64 64K 16K 29 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ128GB106 64 128K 16K 29 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ192GB106 64 192K 16K 29 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ256GB106 64 256K 16K 29 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ64GB108 80 64K 16K 40 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ128GB108 80 128K 16K 40 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ192GB108 80 192K 16K 40 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ256GB108 80 256K 16K 40 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ64GB110 100 64K 16K 44 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ128GB110 100 128K 16K 44 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ192GB110 100 192K 16K 44 5 9 9 4 3 3 16 3 Y Y Y Y

PIC24FJ256GB110 100 256K 16K 44 5 9 9 4 3 3 16 3 Y Y Y Y

64/80/100-Pin, 16-Bit Flash Microcontrollers

with USB On-The-Go (OTG)

PIC24FJ256GB110 FAMILY

DS39897C-page 4 2009 Microchip Technology Inc.

Peripheral Features:

• Peripheral Pin Select (PPS):

- Allows independent I/O mapping of many

peripherals at run time

- Continuous hardware integrity checking and safety

interlocks prevent unintentional configuration

changes

- Up to 44 available pins (100-pin devices)

• Three 3-Wire/4-Wire SPI modules (supports

4 Frame modes) with 8-Level FIFO Buffer

• Three I2C™ modules support Multi-Master/Slave modes

and 7-Bit/10-Bit Addressing

• Four UART modules:

- Supports RS-485, RS-232, LIN/J2602 protocols

and IrDA®

- On-chip hardware encoder/decoder for IrDA

- Auto-wake-up and Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

• Five 16-Bit Timers/Counters with Programmable

Prescaler

• Nine 16-Bit Capture Inputs, each with a

Dedicated Time Base

• Nine 16-Bit Compare/PWM Outputs, each with a

Dedicated Time Base

• 8-Bit Parallel Master Port (PMP/PSP):

- Up to 16 address pins

- Programmable polarity on control lines

• Hardware Real-Time Clock/Calendar (RTCC):

- Provides clock, calendar and alarm functions

• Programmable Cyclic Redundancy Check (CRC)

Generator

• Up to 5 External Interrupt Sources

Special Microcontroller Features:

• Operating Voltage Range of 2.0V to 3.6V

• Self-Reprogrammable under Software Control

• 5.5V Tolerant Input (digital pins only)

• Configurable Open-Drain Outputs on Digital I/O

• High-Current Sink/Source (18 mA/18 mA) on all I/O

• Selectable Power Management modes:

- Sleep, Idle and Doze modes with fast wake-up

• Fail-Safe Clock Monitor Operation:

- Detects clock failure and switches to on-chip,

Low-Power RC Oscillator

• On-Chip LDO Regulator

• Power-on Reset (POR), Power-up Timer (PWRT),

Low-Voltage Detect (LVD) and Oscillator Start-up

Timer (OST)

• Flexible Watchdog Timer (WDT) with On-Chip.

Low-Power RC Oscillator for Reliable Operation

• In-Circuit Serial Programming™ (ICSP™) and

In-Circuit Debug (ICD) via 2 Pins

• JTAG Boundary Scan and Programming Support

• Brown-out Reset (BOR)

• Flash Program Memory:

- 10,000 erase/write cycle endurance (minimum)

- 20-year data retention minimum

- Selectable write protection boundary

- Write protection option for Flash Configuration

Words

2009 Microchip Technology Inc. DS39897C-page 5

PIC24FJ256GB110 FAMILY

Pin Diagram (64-Pin TQFP and QFN)

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

22

44

24

25

26

27

28

29

30

31

32

PIC24FJ64GB106

1

46

45

23

43

42

41

40

39

C3INB/CN15/RD6

RP20/PMRD/CN14/RD5

RP25/PMWR/CN13/RD4

RP22/PMBE/CN52/RD3

DPH/RP23/CN51/RD2

VCPCON/RP24/CN50/RD1

PMD4/CN62/RE4

PMD3/CN61/RE3

PMD2/CN60/RE2

PMD1/CN59/RE1

VBUSST/VCMPST1/CN68/RF0

VCAP/VDDCORE

SOSCI/C3IND/CN1/RC13

DMH/RP11/INT0/CN49/RD0

SCL1/RP3/PMCS2/CN55/RD10

DPLN/SDA1/RP4/CN54/RD9

RTCC/DMLN/RP2/CN53/RD8

RP12/PMCS1/CN56/RD11

OSCO/CLKO/CN22/RC15

OSCI/CLKI/CN23/RC12

VDD

D+/RG2

VUSB

VBUS

RP16/USBID/CN71/RF3

D-/RG3

SOSCO/T1CK/C3INC/RPI37/

AVDD

AN8/RP8/CN26/RB8

AN9/RP9/PMA7/CN27/RB9

TMS/CVREF/AN10/PMA13/CN28/RB10

TDO/AN11/PMA12/CN29/RB11

VDD

PGEC2/AN6/RP6/CN24/RB6

PGED2/AN7/RP7/RCV/CN25/RB7

SCL2/RP17/PMA8/CN18/RF5

SDA2/RP10/PMA9/CN17/RF4

PMD5/CN63/RE5

SCL3/PMD6/CN64/RE6

SDA3/PMD7/CN65/RE7

C1IND/RP21/PMA5/CN8/RG6

VDD

PGEC3/AN5/C1INA/VBUSON/RP18/CN7/RB5

PGED3/AN4/C1INB/USBOEN/RP28/CN6/RB4

AN3/C2INA/VPIO/CN5/RB3

AN2/C2INB/VMIO/RP13/CN4/RB2

C1INC/RP26/PMA4/CN9/RG7

C2IND/RP19/PMA3/CN10/RG8

PGEC1/AN1/VREF-/RP1/CN3/RB1

PGED1/AN0/VREF+/RP0/PMA6/CN2/RB0

RP27/PMA2/C2INC/CN11/RG9

MCLR

TCK/AN12/PMA11/CTED2/CN30/RB12

TDI/AN13/PMA10/CTED1/CN31/RB13

AN14/CTPLS/RP14/PMA1/CN32/RB14

AN15/RP29/REFO/PMA0/CN12/RB15

PMD0/CN58/RE0

VCMPST2/CN69/RF1

C3INA/CN16/RD7

VSS

VSS

VSS

ENVREG

63

62

61

59

60

58

57

56

54

55

53

52

51

49

50

38

37

34

36

35

33

17

19

20

21

18

AVSS

64

CN0/RC14

PIC24FJ128GB106

PIC24FJ192GB106

PIC24FJ256GB106

Legend: Shaded pins indicate pins tolerant to up to +5.5 VDC.

RPn represents remappable pins for the Peripheral Pin Select feature.

Note 1: For QFN devices, the backplane on the underside of the device must also be connected to VSS.

PIC24FJ256GB110 FAMILY

DS39897C-page 6 2009 Microchip Technology Inc.

Pin Diagram (80-Pin TQFP)

80

79

78

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

60

59

26

56

40

39

28

29

30

31

32

33

34

35

36

37

38

PIC24FJ64GB108

17

18

19

1

76

77

58

57

27

55

54

53

52

51

RP20/PMRD/CN14/RD5

RP25/PMWR/CN13/RD4

CN19/RD13

RPI42/CN57/RD12

RP22/PMBE/CN52/RD3

DPH/RP23/CN51/RD2

VCPCON/RP24/CN50/RD1

PMD2/CN60/RE2

PMD1/CN59/RE1

PMD0/CN58/RE0

CN77/RG0

PMD4/CN62/RE4

PMD3/CN61/RE3

VBUSST/VCMPST1/CN68/RF0

VCAP/VDDCORE

SOSCI/C3IND/CN1/RC13

DMH/RP11/INT0/CN49/RD0

SCL1/RP3/PMCS2/CN55/RD10

SDA1/DPLN/RP4/CN54/RD9

DMLN/RTCC/RP2/CN53/RD8

RP12/PMCS1/CN56/RD11

SDA2/RPI35/CN44/RA15

SCL2/RPI36/CN43/RA14

OSCO/CLKO/CN22/RC15

OSCI/CLKI/CN23/RC12

VDD

D+/RG2

VUSB

VBUS

RP15/CN74/RF8

D-/RG3

RP30/CN70/RF2

RP16/USBID/CN71/RF3

SOSCO/T1CK/C3INC/RPI37/CN0/RC14

VREF+/PMA6/CN42/RA10

VREF-/PMA7/CN41/RA9

AVDD

AN8/RP8/CN26/RB8

AN9/RP9/CN27/RB9

AN10/CVREF/PMA13/CN28/RB10

AN11/PMA12/CN29/RB11

VDD

RPI43/CN20/RD14

RP5/CN21/RD15

PGEC2/AN6/RP6/CN24/RB6

PGED2/AN7/RP7/RCV/CN25/RB7

RP17/PMA8/CN18/RF5

RP10/PMA9/CN17/RF4

PMD5/CN63/RE5

SCL3/PMD6/CN64/RE6

SDA3/PMD7/CN65/RE7

RPI38/CN45/RC1

RPI40/CN47/RC3

PMA5/RP21/C1IND/CN8/RG6

VDD

TMS/RPI33/CN66/RE8

TDO/RPI34/CN67/RE9

AN3/C2INA/VPIO/CN5/RB3

AN2/C2INB/VMIO/RP13/CN4/RB2

C1INC/RP26/PMA4/CN9/RG7

C2IND/RP19/PMA3/CN10/RG8

PGEC1/AN1/RP1/CN3/RB1

PGED1/AN0/RP0/CN2/RB0

C2INC/RP27/PMA2/CN11/RG9

MCLR

TCK/AN12/PMA11/CTED2/CN30/RB12

TDI/AN13/PMA10/CTED1/CN31/RB13

AN14/CTPLS/RP14/PMA1/CN32/RB14

AN15/REFO/RP29/PMA0/ACN12/RB15

CN78/RG1

VCMPST2/CN69/RF1

C3INA/CN16/RD7

C3INB/CN15/RD6

VSS

Vss

VSS

ENVREG

75

74

73

71

72

70

69

68

66

67

65

64

63

61

62

50

49

46

48

47

45

44

43

42

41

21

23

24

25

22

AVSS

PGEC3/AN5/C1INA/VBUSON/RP18/CN7/RB5

PGED3/AN4/C1INB/USBOEN/RP28/CN6/RB4

Legend: Shaded pins indicate pins tolerant to up to +5.5 VDC.

RPn represents remappable pins for the Peripheral Pin Select feature.

PIC24FJ128GB108

PIC24FJ192GB108

PIC24FJ256GB108

2009 Microchip Technology Inc. DS39897C-page 7

PIC24FJ256GB110 FAMILY

Pin Diagram (100-Pin TQFP)

92

94

93

91

90

89

88

87

86

85

84

83

82

81

80

79

78

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

65

64

63

62

61

60

59

26

56

45

44

43

42

41

40

39

28

29

30

31

32

33

34

35

36

37

38

PIC24FJ64GB110

17

18

19

21

22

95

1

76

77

72

71

70

69

68

67

66

75

74

73

58

57

24

23

25

96

98

97

99

27

46

47

48

49

50

55

54

53

52

51

100

RP20/PMRD/CN14/RD5

RP25/PMWR/CN13/RD4

CN19/RD13

RPI42/CN57/RD12

RP22/PMBE/CN52/RD3

DPH/RP23/CN51/RD2

VCPCON/RP24/CN50/RD1

CN40/RA7

CN39/RA6

PMD2/CN60/RE2

CN80/RG13

CN79/RG12

CN81/RG14

PMD1/CN59/RE1

PMD0/CN58/RE0

CN77/RG0

PMD4/CN62/RE4

PMD3/CN61/RE3

VBUSST/VCMPST1/CN68/RF0

VCAP/VDDCORE

SOSCI/C3IND/CN1/RC13

DMH/RP11/INT0/CN49/RD0

RP3/PMCS2/CN55/RD10

DPLN/RP4/CN54/RD9

DMLN/RTCC/RP2/CN53/RD8

RP12/PMCS1/CN56/RD11

SDA1/RPI35/CN44/RA15

SCL1/RPI36/CN43/RA14

OSCO/CLKO/CN22/RC15

OSCI/CLKI/CN23/RC12

VDD

D+/RG2

VUSB

VBUS

RP15/CN74/RF8

D-/RG3

RP30/CN70/RF2

RP16/USBID/CN71/RF3

VSS

SOSCO/T1CK/C3INC/RPI37/

VREF+/PMA6/CN42/RA10

VREF-/PMA7/CN41/RA9

AVDD

AVSS

AN8/RP8/CN26/RB8

AN9/RP9/CN27/RB9

AN10/CVREF/PMA13/CN28/RB10

AN11/PMA12/CN29/RB11

VDD

RPI32/CN75/RF12

RP31/CN76/RF13

VSS

VDD

RP5/CN21/RD15

RPI43/CN20/RD14

PGEC2/AN6/RP6/CN24/RB6

PGED2/AN7/RP7/RCV/CN25/RB7

RP17/PMA8/CN18/RF5

RP10/PMA9/CN17/RF4

PMD5/CN63/RE5

SCL3/PMD6/CN64/RE6

SDA3/PMD7/CN65/RE7

RPI38/CN45/RC1

RPI39/CN46/RC2

RPI40/CN47/RC3

RPI41/CN48/RC4

C1IND/RP21/PMA5/CN8/RG6

VDD

TMS/CN33/RA0

RPI33/CN66/RE8

RPI34/CN67/RE9

PGEC3/AN5/C1INA/VBUSON/RP18/CN7/RB5

AN3/C2INA/VPIO/CN5/RB3

AN2/C2INB/VMIO/RP13/CN4/RB2

C1INC/RP26/PMA4/CN9/RG7

C2IND/RP19/PMA3/CN10/RG8

PGEC1/AN1/RP1/CN3/RB1

PGED1/AN0/RP0/CN2/RB0

CN82/RG15

VDD

C2INC/RP27/PMA2/CN11/RG9

MCLR

AN12/PMA11/CTED2/CN30/RB12

AN13/PMA10/CTED1/CN31/RB13

AN14/CTPLS/RP14/PMA1/CN32/RB14

AN15/REFO/RP29/PMA0/CN12/RB15

CN78/RG1

VCMPST2/CN69/RF1

C3INA/CN16/RD7

C3INB/CN15/RD6

TDO/CN38/RA5

SDA2/CN36/RA3

SCL2/CN35/RA2

VSS

VSS

VSS

ENVREG

TDI/CN37/RA4

TCK/CN34/RA1

PGED3/AN4/C1INB/USBOEN/RP28/CN6/RB4

Legend: Shaded pins indicate pins tolerant to up to +5.5 VDC.

RPn and RPIn represent remappable pins for the Peripheral Pin Select features.

CN0/RC14

PIC24FJ128GB110

PIC24FJ192GB110

PIC24FJ256GB110

PIC24FJ256GB110 FAMILY

DS39897C-page 8 2009 Microchip Technology Inc.

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 11

2.0 Guidelines for Getting Started with 16-bit Microcontrollers ........................................................................................................ 27

3.0 CPU ........................................................................................................................................................................................... 33

4.0 Memory Organization ................................................................................................................................................................. 39

5.0 Flash Program Memory.............................................................................................................................................................. 63

6.0 Resets ........................................................................................................................................................................................ 71

7.0 Interrupt Controller ..................................................................................................................................................................... 77

8.0 Oscillator Configuration ............................................................................................................................................................ 121

9.0 Power-Saving Features............................................................................................................................................................ 131

10.0 I/O Ports ................................................................................................................................................................................... 133

11.0 Timer1 ...................................................................................................................................................................................... 161

12.0 Timer2/3 and Timer4/5 ............................................................................................................................................................ 163

13.0 Input Capture with Dedicated Timers ....................................................................................................................................... 169

14.0 Output Compare with Dedicated Timers .................................................................................................................................. 173

15.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 181

16.0 Inter-Integrated Circuit (I2C™) ................................................................................................................................................. 191

17.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 199

18.0 Universal Serial Bus with On-The-Go Support (USB OTG) ..................................................................................................... 207

19.0 Parallel Master Port (PMP)....................................................................................................................................................... 241

20.0 Real-Time Clock and Calendar (RTCC) .................................................................................................................................. 251

21.0 Programmable Cyclic Redundancy Check (CRC) Generator .................................................................................................. 263

22.0 10-Bit High-Speed A/D Converter ............................................................................................................................................ 267

23.0 Triple Comparator Module........................................................................................................................................................ 277

24.0 Comparator Voltage Reference................................................................................................................................................ 281

25.0 Charge Time Measurement Unit (CTMU) ................................................................................................................................ 283

26.0 Special Features ...................................................................................................................................................................... 287

27.0 Development Support............................................................................................................................................................... 299

28.0 Instruction Set Summary .......................................................................................................................................................... 303

29.0 Electrical Characteristics .......................................................................................................................................................... 311

30.0 Packaging Information.............................................................................................................................................................. 327

Appendix A: Revision History............................................................................................................................................................. 341

Index ................................................................................................................................................................................................. 343

The Microchip Web Site ..................................................................................................................................................................... 349

Customer Change Notification Service .............................................................................................................................................. 349

Customer Support .............................................................................................................................................................................. 349

Reader Response .............................................................................................................................................................................. 350

Product Identification System............................................................................................................................................................. 351

2009 Microchip Technology Inc. DS39897C-page 9

PIC24FJ256GB110 FAMILY

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

PIC24FJ256GB110 FAMILY

DS39897C-page 10 2009 Microchip Technology Inc.

NOTES:

2009 Microchip Technology Inc. DS39897C-page 11

PIC24FJ256GB110 FAMILY

1.0 DEVICE OVERVIEW

This document contains device-specific information for

the following devices:

This expands on the existing line of Microchip‘s 16-bit

microcontrollers, combining an expanded peripheral

feature set and enhanced computational performance

with a new connectivity option: USB On-The-Go. The

PIC24FJ256GB110 family provides a new platform for

high-performance USB applications, which may need

more than an 8-bit platform, but don’t require the power

of a digital signal processor.

1.1 Core Features

1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified

Harvard architecture, first introduced with Microchip’s

dsPIC® digital signal controllers. The PIC24F CPU core

offers a wide range of enhancements, such as:

• 16-bit data and 24-bit address paths with the

ability to move information between data and

memory spaces

• Linear addressing of up to 12 Mbytes (program

space) and 64 Kbytes (data)

• A 16-element working register array with built-in

software stack support

• A 17 x 17 hardware multiplier with support for

integer math

• Hardware support for 32 by 16-bit division

• An instruction set that supports multiple

addressing modes and is optimized for high-level

languages such as ‘C’

• Operational performance up to 16 MIPS

1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FJ256GB110 family

incorporate a range of features that can significantly

reduce power consumption during operation. Key

items include:

• On-the-Fly Clock Switching: The device clock

can be changed under software control to the

Timer1 source or the internal, Low-Power RC

Oscillator during operation, allowing the user to

incorporate power-saving ideas into their software

designs.

• Doze Mode Operation: When timing-sensitive

applications, such as serial communications,

require the uninterrupted operation of peripherals,

the CPU clock speed can be selectively reduced,

allowing incremental power savings without

missing a beat.

• Instruction-Based Power-Saving Modes: The

microcontroller can suspend all operations, or

selectively shut down its core while leaving its

peripherals active, with a single instruction in

software.

1.1.3 OSCILLATOR OPTIONS AND

FEATURES

All of the devices in the PIC24FJ256GB110 family offer

five different oscillator options, allowing users a range

of choices in developing application hardware. These

include:

• Two Crystal modes using crystals or ceramic

resonators.

• Two External Clock modes offering the option of a

divide-by-2 clock output.

• A Fast Internal Oscillator (FRC) with a nominal

8 MHz output, which can also be divided under

software control to provide clock speeds as low as

31 kHz.

• A Phase Lock Loop (PLL) frequency multiplier,

available to the external oscillator modes and the

FRC Oscillator, which allows clock speeds of up

to 32 MHz.

• A separate internal RC Oscillator (LPRC) with a

fixed 31 kHz output, which provides a low-power

option for timing-insensitive applications.

The internal oscillator block also provides a stable

reference source for the Fail-Safe Clock Monitor. This

option constantly monitors the main clock source

against a reference signal provided by the internal

oscillator and enables the controller to switch to the

internal oscillator, allowing for continued low-speed

operation or a safe application shutdown.

1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the

same rich set of peripherals, allowing for a smooth

migration path as applications grow and evolve. The

consistent pinout scheme used throughout the entire

family also aids in migrating from one device to the next

larger, or even in jumping from 64-pin to 100-pin

devices.

The PIC24F family is pin-compatible with devices in the

dsPIC33 family, and shares some compatibility with the

pinout schema for PIC18 and dsPIC30. This extends

the ability of applications to grow from the relatively

simple, to the powerful and complex, yet still selecting

a Microchip device.

• PIC24FJ64GB106 • PIC24FJ192GB108

• PIC24FJ128GB106 • PIC24FJ256GB108

• PIC24FJ192GB106 • PIC24FJ64GB110

• PIC24FJ256GB106 • PIC24FJ128GB110

• PIC24FJ64GB108 • PIC24FJ192GB110

• PIC24FJ128GB108 • PIC24FJ256GB110

PIC24FJ256GB110 FAMILY

DS39897C-page 12 2009 Microchip Technology Inc.

1.2 USB On-The-Go

With the PIC24FJ256GB110 family of devices,

Microchip introduces USB On-The-Go functionality on

a single chip to its product line. This new module

provides on-chip functionality as a target device compatible

with the USB 2.0 standard, as well as limited

stand-alone functionality as a USB embedded host. By

implementing USB Host Negotiation Protocol (HNP),

the module can also dynamically switch between

device and host operation, allowing for a much wider

range of versatile USB-enabled applications on a

microcontroller platform.

In addition to USB host functionality, PIC24FJ256GB110

family devices provide a true single-chip USB solution,

including an on-chip transceiver and voltage regulator,

and a voltage boost generator for sourcing bus power

during host operations.

1.3 Other Special Features

• Peripheral Pin Select: The Peripheral Pin Select

(PPS) feature allows most digital peripherals to be

mapped over a fixed set of digital I/O pins. Users

may independently map the input and/or output of

any one of the many digital peripherals to any one

of the I/O pins.

• Communications: The PIC24FJ256GB110 family

incorporates a range of serial communication

peripherals to handle a range of application

requirements. There are three independent I2C

modules that support both Master and Slave

modes of operation. Devices also have, through

the Peripheral Pin Select feature, four independent

UARTs with built-in IrDA encoder/decoders and

three SPI modules.

• Analog Features: All members of the

PIC24FJ256GB110 family include a 10-bit A/D

Converter module and a triple comparator

module. The A/D module incorporates programmable

acquisition time, allowing for a channel to

be selected and a conversion to be initiated

without waiting for a sampling period, as well as

faster sampling speeds. The comparator module

includes three analog comparators that are

configurable for a wide range of operations.

• CTMU Interface: In addition to their other analog

features, members of the PIC24FJ256GB110

family include the brand new CTMU interface

module. This provides a convenient method for

precision time measurement and pulse generation,

and can serve as an interface for capacitive

sensors.

• Parallel Master/Enhanced Parallel Slave Port:

One of the general purpose I/O ports can be

reconfigured for enhanced parallel data communications.

In this mode, the port can be configured

for both master and slave operations, and

supports 8-bit and 16-bit data transfers with up to

16 external address lines in Master modes.

• Real-Time Clock/Calendar: This module

implements a full-featured clock and calendar with

alarm functions in hardware, freeing up timer

resources and program memory space for use of

the core application.

1.4 Details on Individual Family

Members

Devices in the PIC24FJ256GB110 family are available

in 64-pin, 80-pin and 100-pin packages. The general

block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four

ways:

1. Flash program memory (64 Kbytes for

PIC24FJ64GB1 devices, 128 Kbytes for

PIC24FJ128GB1 devices, 192 Kbytes for

PIC24FJ192GB1 devices and 256 Kbytes for

PIC24FJ256GB1 devices).

2. Available I/O pins and ports (51 pins on 6 ports

for 64-pin devices, 65 pins on 7 ports for 80-pin

devices and 83 pins on 7 ports for 100-pin

devices).

3. Available Interrupt-on-Change Notification (ICN)

inputs (49 on 64-pin devices, 63 on 80-pin

devices and 81 on 100-pin devices).

4. Available remappable pins (29 pins on 64-pin

devices, 40 pins on 80-pin devices and 44 pins

on 100-pin devices)

All other features for devices in this family are identical.

These are summarized in Table 1-1.

A list of the pin features available on the

PIC24FJ256GB110 family devices, sorted by function,

is shown in Table 1-4. Note that this table shows the pin

location of individual peripheral features and not how

they are multiplexed on the same pin. This information

is provided in the pinout diagrams in the beginning of

the data sheet. Multiplexed features are sorted by the

priority given to a feature, with the highest priority

peripheral being listed first.

2009 Microchip Technology Inc. DS39897C-page 13

PIC24FJ256GB110 FAMILY

TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ256GB110 FAMILY: 64-PIN DEVICES

Features 64GB106 128GB106 192GB106 256GB106

Operating Frequency DC – 32 MHz

Program Memory (bytes) 64K 128K 192K 256K

Program Memory (instructions) 22,016 44,032 67,072 87,552

Data Memory (bytes) 16,384

Interrupt Sources (soft vectors/NMI traps) 66 (62/4)

I/O Ports Ports B, C, D, E, F, G

Total I/O Pins 51

Remappable Pins 29 (28 I/O, 1 Input only)

Timers:

Total Number (16-bit) 5(1)

32-Bit (from paired 16-bit timers) 2

Input Capture Channels 9(1)

Output Compare/PWM Channels 9(1)

Input Change Notification Interrupt 49

Serial Communications:

UART 4(1)

SPI (3-wire/4-wire) 3(1)

I2C™ 3

Parallel Communications (PMP/PSP) Yes

JTAG Boundary Scan/Programming Yes

10-Bit Analog-to-Digital Module

(input channels)

16

Analog Comparators 3

CTMU Interface Yes

Resets (and delays) POR, BOR, RESET Instruction, MCLR, WDT; Illegal Opcode,

REPEAT Instruction, Hardware Traps, Configuration Word Mismatch

(PWRT, OST, PLL Lock)

Instruction Set 76 Base Instructions, Multiple Addressing Mode Variations

Packages 64-Pin TQFP

Note 1: Peripherals are accessible through remappable pins.

PIC24FJ256GB110 FAMILY

DS39897C-page 14 2009 Microchip Technology Inc.

TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ256GB110 FAMILY: 80-PIN DEVICES

Features 64GB108 128GB108 192GB108 256GB108

Operating Frequency DC – 32 MHz

Program Memory (bytes) 64K 128K 192K 256K

Program Memory (instructions) 22,016 44,032 67,072 87,552

Data Memory (bytes) 16,384

Interrupt Sources (soft vectors/NMI traps) 66 (62/4)

I/O Ports Ports A, B, C, D, E, F, G

Total I/O Pins 65

Remappable Pins 40 (31 I/O, 9 Input only)

Timers:

Total Number (16-bit) 5(1)

32-Bit (from paired 16-bit timers) 2

Input Capture Channels 9(1)

Output Compare/PWM Channels 9(1)

Input Change Notification Interrupt 63

Serial Communications:

UART 4(1)

SPI (3-wire/4-wire) 3(1)

I2C™ 3

Parallel Communications (PMP/PSP) Yes

JTAG Boundary Scan/Programming Yes

10-Bit Analog-to-Digital Module

(input channels)

16

Analog Comparators 3

CTMU Interface Yes

Resets (and delays) POR, BOR, RESET Instruction, MCLR, WDT; Illegal Opcode,

REPEAT Instruction, Hardware Traps, Configuration Word Mismatch

(PWRT, OST, PLL Lock)

Instruction Set 76 Base Instructions, Multiple Addressing Mode Variations

Packages 80-Pin TQFP

Note 1: Peripherals are accessible through remappable pins.

2009 Microchip Technology Inc. DS39897C-page 15

PIC24FJ256GB110 FAMILY

TABLE 1-3: DEVICE FEATURES FOR THE PIC24FJ256GB110 FAMILY: 100-PIN DEVICES

Features 64GB110 128GB110 192GB110 256GB110

Operating Frequency DC – 32 MHz

Program Memory (bytes) 64K 128K 192K 256K

Program Memory (instructions) 22,016 44,032 67,072 87,552

Data Memory (bytes) 16,384

Interrupt Sources (soft vectors/NMI traps) 66 (62/4)

I/O Ports Ports A, B, C, D, E, F, G

Total I/O Pins 83

Remappable Pins 44 (32 I/O, 12 Input only)

Timers:

Total Number (16-bit) 5(1)

32-Bit (from paired 16-bit timers) 2

Input Capture Channels 9(1)

Output Compare/PWM Channels 9(1)

Input Change Notification Interrupt 81

Serial Communications:

UART 4(1)

SPI (3-wire/4-wire) 3(1)

I2C™ 3

Parallel Communications (PMP/PSP) Yes

JTAG Boundary Scan/Programming Yes

10-Bit Analog-to-Digital Module

(input channels)

16

Analog Comparators 3

CTMU Interface Yes

Resets (and delays) POR, BOR, RESET Instruction, MCLR, WDT; Illegal Opcode,

REPEAT Instruction, Hardware Traps, Configuration Word Mismatch

(PWRT, OST, PLL Lock)

Instruction Set 76 Base Instructions, Multiple Addressing Mode Variations

Packages 100-Pin TQFP

Note 1: Peripherals are accessible through remappable pins.

PIC24FJ256GB110 FAMILY

DS39897C-page 16 2009 Microchip Technology Inc.

FIGURE 1-1: PIC24FJ256GB110 FAMILY GENERAL BLOCK DIAGRAM

Instruction

Decode &

Control

16

PCH PCL

16

Program Counter

16-Bit ALU

23

24

Data Bus

Inst Register

16

Divide

Support

Inst Latch

16

EA MUX

Read AGU

Write AGU

16

16

8

Interrupt

Controller

PSV & Table

Data Access

Control Block

Stack

Control

Logic

Repeat

Control

Logic

Data Latch

Data RAM

Address

Latch

Address Latch

Program Memory

Data Latch

16

Address Bus

Literal Data

23

Control Signals

16

16

16 x 16

W Reg Array

Multiplier

OSCI/CLKI 17x17

OSCO/CLKO

VDD,

Timing

Generation

VSS MCLR

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

BOR and

Precision

Reference

Band Gap

FRC/LPRC

Oscillators

Regulator

Voltage

VDDCORE/VCAP

ENVREG

PORTA(1)

PORTC(1)

(13 I/O)

(8 I/O)

PORTB

(16 I/O)

Note 1: Not all I/O pins or features are implemented on all device pinout configurations. See Table 1-4 for specific implementations by pin count.

2: BOR functionality is provided when the on-board voltage regulator is enabled.

3: These peripheral I/Os are only accessible through remappable pins.

PORTD(1)

(16 I/O)

Timer1 Timer2/3(3) RTCC Comparators(3)

IC

ADC

10-Bit

PWM/OC SPI I2C

Timer4/5(3)

PMP/PSP

1-9(3) ICNs(1) UART

LVD(2)

REFO

PORTE(1)

PORTG(1)

(10 I/O)

(12 I/O)

PORTF(1)

(9 I/O)

1-9(3) 1/2/3(3) 1/2/3 1/2/3/4(3) CTMU

USB OTG

2009 Microchip Technology Inc. DS39897C-page 17

PIC24FJ256GB110 FAMILY

TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS

Function

Pin Number

I/O Input

64-Pin Buffer Description

TQFP, QFN

80-Pin

TQFP

100-Pin

TQFP

AN0 16 20 25 I ANA A/D Analog Inputs.

AN1 15 19 24 I ANA

AN2 14 18 23 I ANA

AN3 13 17 22 I ANA

AN4 12 16 21 I ANA

AN5 11 15 20 I ANA

AN6 17 21 26 I ANA

AN7 18 22 27 I ANA

AN8 21 27 32 I ANA

AN9 22 28 33 I ANA

AN10 23 29 34 I ANA

AN11 24 30 35 I ANA

AN12 27 33 41 I ANA

AN13 28 34 42 I ANA

AN14 29 35 43 I ANA

AN15 30 36 44 I ANA

AVDD 19 25 30 P — Positive Supply for Analog modules.

AVSS 20 26 31 P — Ground Reference for Analog modules.

C1INA 11 15 20 I ANA Comparator 1 Input A.

C1INB 12 16 21 I ANA Comparator 1 Input B.

C1INC 5 7 11 I ANA Comparator 1 Input C.

C1IND 4 6 10 I ANA Comparator 1 Input D.

C2INA 13 17 22 I ANA Comparator 2 Input A.

C2INB 14 18 23 I ANA Comparator 2 Input B.

C2INC 8 10 14 I ANA Comparator 2 Input C.

C2IND 6 8 12 I ANA Comparator 2 Input D.

C3INA 55 69 84 I ANA Comparator 3 Input A.

C3INB 54 68 83 I ANA Comparator 3 Input B.

C3INC 48 60 74 I ANA Comparator 3 Input C.

C3IND 47 59 73 I ANA Comparator 3 Input D.

CLKI 39 49 63 I ANA Main Clock Input Connection.

CLKO 40 50 64 O — System Clock Output.

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I2C™ = I2C/SMBus input buffer

PIC24FJ256GB110 FAMILY

DS39897C-page 18 2009 Microchip Technology Inc.

CN0 48 60 74 I ST Interrupt-on-Change Inputs.

CN1 47 59 73 I ST

CN2 16 20 25 I ST

CN3 15 19 24 I ST

CN4 14 18 23 I ST

CN5 13 17 22 I ST

CN6 12 16 21 I ST

CN7 11 15 20 I ST

CN8 4 6 10 I ST

CN9 5 7 11 I ST

CN10 6 8 12 I ST

CN11 8 10 14 I ST

CN12 30 36 44 I ST

CN13 52 66 81 I ST

CN14 53 67 82 I ST

CN15 54 68 83 I ST

CN16 55 69 84 I ST

CN17 31 39 49 I ST

CN18 32 40 50 I ST

CN19 — 65 80 I ST

CN20 — 37 47 I ST

CN21 — 38 48 I ST

CN22 40 50 64 I ST

CN23 39 49 63 I ST

CN24 17 21 26 I ST

CN25 18 22 27 I ST

CN26 21 27 32 I ST

CN27 22 28 33 I ST

CN28 23 29 34 I ST

CN29 24 30 35 I ST

CN30 27 33 41 I ST

CN31 28 34 42 I ST

CN32 29 35 43 I ST

CN33 — — 17 I ST

CN34 — — 38 I ST

CN35 — — 58 I ST

CN36 — — 59 I ST

CN37 — — 60 I ST

CN38 — — 61 I ST

CN39 — — 91 I ST

CN40 — — 92 I ST

CN41 — 23 28 I ST

CN42 — 24 29 I ST

TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

Pin Number

I/O Input

64-Pin Buffer Description

TQFP, QFN

80-Pin

TQFP

100-Pin

TQFP

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I2C™ = I2C/SMBus input buffer

2009 Microchip Technology Inc. DS39897C-page 19

PIC24FJ256GB110 FAMILY

CN43 — 52 66 I ST Interrupt-on-Change Inputs.

CN44 — 53 67 I ST

CN45 — 4 6 I ST

CN46 — — 7 I ST

CN47 — 5 8 I ST

CN48 — — 9 I ST

CN49 46 58 72 I ST

CN50 49 61 76 I ST

CN51 50 62 77 I ST

CN52 51 63 78 I ST

CN53 42 54 68 I ST

CN54 43 55 69 I ST

CN55 44 56 70 I ST

CN56 45 57 71 I ST

CN57 — 64 79 I ST

CN58 60 76 93 I ST

CN59 61 77 94 I ST

CN60 62 78 98 I ST

CN61 63 79 99 I ST

CN62 64 80 100 I ST

CN63 1 1 3 I ST

CN64 2 2 4 I ST

CN65 3 3 5 I ST

CN66 — 13 18 I ST

CN67 — 14 19 I ST

CN68 58 72 87 I ST

CN69 59 73 88 I ST

CN70 — 42 52 I ST

CN71 33 41 51 I ST

CN74 — 43 53 I ST

CN75 — — 40 I ST

CN76 — — 39 I ST

CN77 — 75 90 I ST

CN78 — 74 89 I ST

CN79 — — 96 I ST

CN80 — — 97 I ST

CN81 — — 95 I ST

CN82 — — 1 I ST

CTED1 28 34 42 I ANA CTMU External Edge Input 1.

CTED2 27 33 41 I ANA CTMU External Edge Input 2.

CTPLS 29 35 43 O — CTMU Pulse Output.

CVREF 23 29 34 O — Comparator Voltage Reference Output.

TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

Pin Number

I/O Input

64-Pin Buffer Description

TQFP, QFN

80-Pin

TQFP

100-Pin

TQFP

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I2C™ = I2C/SMBus input buffer

PIC24FJ256GB110 FAMILY

DS39897C-page 20 2009 Microchip Technology Inc.

D+ 37 47 57 I/O — USB Differential Plus line (internal transceiver).

D- 36 46 56 I/O — USB Differential Minus line (internal transceiver).

DMH 46 58 72 O — D- External Pull-up Control Output.

DMLN 42 54 68 O — D- External Pull-down Control Output.

DPH 50 62 77 O — D+ External Pull-up Control Output.

DPLN 43 55 69 O — D+ External Pull-down Control Output.

ENVREG 57 71 86 I ST Voltage Regulator Enable.

INT0 46 58 72 I ST External Interrupt Input.

MCLR 7 9 13 I ST Master Clear (device Reset) Input. This line is brought low

to cause a Reset.

OSCI 39 49 63 I ANA Main Oscillator Input Connection.

OSCO 40 50 64 O ANA Main Oscillator Output Connection.

PGEC1 15 19 24 I/O ST In-Circuit Debugger/Emulator/ICSP™ Programming Clock.

PGED1 16 20 25 I/O ST In-Circuit Debugger/Emulator/ICSP Programming Data.

PGEC2 17 21 26 I/O ST In-Circuit Debugger/Emulator/ICSP Programming Clock.

PGED2 18 22 27 I/O ST In-Circuit Debugger/Emulator/ICSP Programming Data.

PGEC3 11 15 20 I/O ST In-Circuit Debugger/Emulator/ICSP Programming Clock.

PGED3 12 16 21 I/O ST In-Circuit Debugger/Emulator/ICSP Programming Data.

PMA0 30 36 44 I/O ST Parallel Master Port Address Bit 0 Input (Buffered Slave

modes) and Output (Master modes).

PMA1 29 35 43 I/O ST Parallel Master Port Address Bit 1 Input (Buffered Slave

modes) and Output (Master modes).

PMA2 8 10 14 O — Parallel Master Port Address (Demultiplexed Master

PMA3 6 8 12 O — modes).

PMA4 5 7 11 O —

PMA5 4 6 10 O —

PMA6 16 24 29 O —

PMA7 22 23 28 O —

PMA8 32 40 50 O —

PMA9 31 39 49 O —

PMA10 28 34 42 O —

PMA11 27 33 41 O —

PMA12 24 30 35 O —

PMA13 23 29 34 O —

PMCS1 45 57 71 I/O ST/TTL Parallel Master Port Chip Select 1 Strobe/Address Bit 15.

PMCS2 44 56 70 O ST Parallel Master Port Chip Select 2 Strobe/Address Bit 14.

PMBE 51 63 78 O — Parallel Master Port Byte Enable Strobe.

TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

Pin Number

I/O Input

64-Pin Buffer Description

TQFP, QFN

80-Pin

TQFP

100-Pin

TQFP

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I2C™ = I2C/SMBus input buffer

2009 Microchip Technology Inc. DS39897C-page 21

PIC24FJ256GB110 FAMILY

PMD0 60 76 93 I/O ST/TTL Parallel Master Port Data (Demultiplexed Master mode) or

PMD1 61 77 94 I/O ST/TTL Address/Data (Multiplexed Master modes).

PMD2 62 78 98 I/O ST/TTL

PMD3 63 79 99 I/O ST/TTL

PMD4 64 80 100 I/O ST/TTL

PMD5 1 1 3 I/O ST/TTL

PMD6 2 2 4 I/O ST/TTL

PMD7 3 3 5 I/O ST/TTL

PMRD 53 67 82 O — Parallel Master Port Read Strobe.

PMWR 52 66 81 O — Parallel Master Port Write Strobe.

RA0 — — 17 I/O ST PORTA Digital I/O.

RA1 — — 38 I/O ST

RA2 — — 58 I/O ST

RA3 — — 59 I/O ST

RA4 — — 60 I/O ST

RA5 — — 61 I/O ST

RA6 — — 91 I/O ST

RA7 — — 92 I/O ST

RA9 — 23 28 I/O ST

RA10 — 24 29 I/O ST

RA14 — 52 66 I/O ST

RA15 — 53 67 I/O ST

RB0 16 20 25 I/O ST PORTB Digital I/O.

RB1 15 19 24 I/O ST

RB2 14 18 23 I/O ST

RB3 13 17 22 I/O ST

RB4 12 16 21 I/O ST

RB5 11 15 20 I/O ST

RB6 17 21 26 I/O ST

RB7 18 22 27 I/O ST

RB8 21 27 32 I/O ST

RB9 22 28 33 I/O ST

RB10 23 29 34 I/O ST

RB11 24 30 35 I/O ST

RB12 27 33 41 I/O ST

RB13 28 34 42 I/O ST

RB14 29 35 43 I/O ST

RB15 30 36 44 I/O ST

TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

Pin Number

I/O Input

64-Pin Buffer Description

TQFP, QFN

80-Pin

TQFP

100-Pin

TQFP

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I2C™ = I2C/SMBus input buffer