Consent Manager Tag v2.0 (for TCF 2.0) -->

Farnell PDF

AD9834 (Rev. D) - Analog Devices - Farnell Element 14

AD9834 (Rev. D) - Analog Devices - Farnell Element 14

AD9834 (Rev. D) - Analog Devices - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

Farnell-MSP430-Hardw..> 29-Jul-2014 10:36 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM324-Texas-..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM386-Low-Vo..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NE5532-Texas..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Hex-Inverter..> 29-Jul-2014 10:31 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT90USBKey-H..> 29-Jul-2014 10:31 902K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT89C5131-Ha..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP-EXP430F5..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Explorer-16-..> 29-Jul-2014 10:31 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMP006EVM-Us..> 29-Jul-2014 10:30 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Gertboard-Us..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMP91051-Use..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Thermometre-..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-user-manuel-..> 29-Jul-2014 10:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fx-3650P-fx-..> 29-Jul-2014 10:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2-GBPS-Diffe..> 28-Jul-2014 17:42 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMT88-2.4V-1..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Octal-Genera..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dual-MOSFET-..> 28-Jul-2014 17:41 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TLV320AIC325..> 28-Jul-2014 17:41 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54LV4053A-..> 28-Jul-2014 17:20 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TAS1020B-USB..> 28-Jul-2014 17:19 6.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TPS40060-Wid..> 28-Jul-2014 17:19 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TL082-Wide-B..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RF-short-tra..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-maxim-integr..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TSV6390-TSV6..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fast-Charge-..> 28-Jul-2014 17:12 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NVE-datashee..> 28-Jul-2014 17:12 6.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-REF102-10V-P..> 28-Jul-2014 17:09 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMS320F28055..> 28-Jul-2014 17:09 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MULTICOMP-Ra..> 22-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RASPBERRY-PI..> 22-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 22-Jul-2014 12:34 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F103x8-..> 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BD6xxx-PDF.htm 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L78S-STMicro..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RaspiCam-Doc..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB520-SB5100..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-iServer-Micr..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUMINARY-MIC..> 22-Jul-2014 12:31 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:31 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:30 4.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CLASS 1-or-2..> 22-Jul-2014 12:30 4.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:29 4.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Evaluating-t..> 22-Jul-2014 12:28 4.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM3S6952-Mic..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Keyboard-Mou..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-pmbta13_pmbt..> 15-Jul-2014 17:06 959K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EE-SPX303N-4..> 15-Jul-2014 17:06 969K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 15-Jul-2014 17:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MIDAS-un-tra..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SERIAL-TFT-M..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-series..> 15-Jul-2014 16:48 787K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-DC-Conver..> 15-Jul-2014 16:48 781K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:47 803K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMLM-Series-..> 15-Jul-2014 16:47 810K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEL-5-Series..> 15-Jul-2014 16:47 814K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TXL-series-t..> 15-Jul-2014 16:47 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEP-150WI-Se..> 15-Jul-2014 16:47 837K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AC-DC-Power-..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-Instruct..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TOS-tracopow..> 15-Jul-2014 16:47 852K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TCL-DC-traco..> 15-Jul-2014 16:46 858K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-series-t..> 15-Jul-2014 16:46 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-Series..> 15-Jul-2014 16:46 897K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-3-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEN-8-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:46 947K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HIP4081A-Int..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ISL6251-ISL6..> 07-Jul-2014 19:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DG411-DG412-..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3367-ARALDIT..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ICM7228-Inte..> 07-Jul-2014 19:46 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-K..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Silica-Gel-M..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TKC2-Dusters..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CRC-HANDCLEA..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-760G-French-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Decapant-KF-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1734-ARALDIT..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Araldite-Fus..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fiche-de-don..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-safety-data-..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-4-Hardener..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC-Debugger-..> 07-Jul-2014 19:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430-Hardw..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SmartRF06-Ev..> 07-Jul-2014 19:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2531-USB-H..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK889B-PONT-..> 07-Jul-2014 19:42 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-User-Guide-M..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mini-Fit-Jr-..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-43031-0002-M..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0433751001-D..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cube-3D-Prin..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-Compact-..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-3250-MTX..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 18-Jul-2014 17:00 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCP3421-Micr..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM19-Texas-I..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-S..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMH6518-Texa..> 18-Jul-2014 16:59 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7719-Low-V..> 18-Jul-2014 16:59 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DAC8143-Data..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BGA7124-400-..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SICK-OPTIC-E..> 18-Jul-2014 16:58 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT3757-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT1961-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2420-2..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DS3231-DS-PD..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RDS-80-PDF.htm 18-Jul-2014 16:57 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8300-Data-..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT6233-Linea..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX1365-MAX1..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPSAF5130-PD..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DP83846A-DsP..> 18-Jul-2014 16:55 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 18-Jul-2014 16:55 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 16-Jul-2014 09:04 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 16-Jul-2014 09:04 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-Full-N..> 16-Jul-2014 09:03 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S4011_402..> 16-Jul-2014 09:03 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC408x-7x 3..> 16-Jul-2014 09:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PCF8574-PCF8..> 16-Jul-2014 09:03 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-32-b..> 16-Jul-2014 09:02 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 16-Jul-2014 09:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC3220-30-4..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC11U3x-32-..> 16-Jul-2014 09:01 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3ICS1002-1..> 16-Jul-2014 09:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 08-Jul-2014 18:59 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-tesa®pack63..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Encodeur-USB..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2530ZDK-Us..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2020-Manuel-..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Synchronous-..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Arithmetic-L..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-4-Bit-Magnit..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM555-Timer-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293d-Texas-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC244-SN..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX232-MAX23..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-High-precisi..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMU-Instrume..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-900-Series-B..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BA-Series-Oh..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-270-Series-O..> 08-Jul-2014 18:49 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tiva-C-Serie..> 08-Jul-2014 18:49 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTO-Souriau-..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Clipper-Seri..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOURIAU-Cont..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-851-Series-P..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

Farnell-SL59830-Inte..> 06-Jul-2014 10:07 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 06-Jul-2014 10:06 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7171-16-Bi..> 06-Jul-2014 10:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-Noise-24..> 06-Jul-2014 10:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:05 938K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74LCX573-Fai..> 06-Jul-2014 10:05 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1N4148WS-Fai..> 06-Jul-2014 10:04 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FAN6756-Fair..> 06-Jul-2014 10:04 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 06-Jul-2014 10:04 861K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES1F-ES1J-fi..> 06-Jul-2014 10:04 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-QRE1113-Fair..> 06-Jul-2014 10:03 879K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N7002DW-Fai..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDC2512-Fair..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDV301N-Digi..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S1A-Fairchil..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAV99-Fairch..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74AC00-74ACT..> 06-Jul-2014 10:03 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NaPiOn-Panas..> 06-Jul-2014 10:02 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LQ-RELAYS-AL..> 06-Jul-2014 10:02 924K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ev-relays-ae..> 06-Jul-2014 10:02 926K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:02 931K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplifier-In..> 06-Jul-2014 10:02 940K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serial-File-..> 06-Jul-2014 10:02 941K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Both-the-Del..> 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Videk-PDF.htm 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

20 mW Power, 2.3 V to 5.5 V,

75 MHz Complete DDS

Data Sheet AD9834

FEATURES

Narrow-band SFDR >72 dB

2.3 V to 5.5 V power supply

Output frequency up to 37.5 MHz

Sine output/triangular output

On-board comparator

3-wire SPI® interface

Extended temperature range: −40°C to +105°C

Power-down option

20 mW power consumption at 3 V

20-lead TSSOP

APPLICATIONS

Frequency stimulus/waveform generation

Frequency phase tuning and modulation

Low power RF/communications systems

Liquid and gas flow measurement

Sensory applications: proximity, motion, and defect detection

Test and medical equipment

GENERAL DESCRIPTION

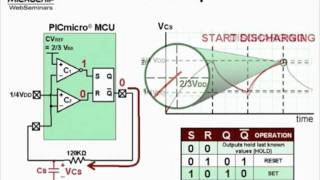

The AD9834 is a 75 MHz low power DDS device capable of producing high performance sine and triangular outputs. It also has an on-board comparator that allows a square wave to be produced for clock generation. Consuming only 20 mW of power at 3 V makes the AD9834 an ideal candidate for power-sensitive applications.Capability for phase modulation and frequency modulation is provided. The frequency registers are 28 bits; with a 75 MHz clock rate, resolution of 0.28 Hz can be achieved. Similarly, with a 1 MHz clock rate, the AD9834 can be tuned to 0.004 Hz resolution. Frequency and phase modulation are affected by loading registers through the serial interface and toggling the registers using software or the FSELECT pin and PSELECT pin, respectively.

The AD9834 is written to using a 3-wire serial interface. This serial interface operates at clock rates up to 40 MHz and is compatible with DSP and microcontroller standards.

The device operates with a power supply from 2.3 V to 5.5 V. The analog and digital sections are independent and can be run from different power supplies, for example, AVDD can equal 5 V with DVDD equal to 3 V.

The AD9834 has a power-down pin (SLEEP) that allows external control of the power-down mode. Sections of the device that are not being used can be powered down to minimize the current consumption. For example, the DAC can be powered down when a clock output is being generated.

The part is available in a 20-lead TSSOP.

FUNCTIONAL BLOCK DIAGRAM

12ΣMUXMUXCOMPARATORMSBCAP/2.5VDVDDAGNDAVDDMCLKAD9834FSYNCSCLKSDATACOMPIOUTIOUTBDGNDREGULATORREFOUTFS ADJUSTVINFSELECT12-BIT PHASE0 REG12-BIT PHASE1 REGSLEEPRESETPSELECTMUXMUXMUXSIGN BIT OUTVCC2.5VON-BOARDREFERENCE16-BIT CONTROLREGISTERFULL-SCALECONTROL10-BITDACDIVIDEDBY 2SINROMPHASEACCUMULATOR(28-BIT)28-BIT FREQ0REG28-BIT FREQ1REGSERIAL INTERFACEANDCONTROL LOGIC02705-001

Figure 1. Rev. D Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2003–2014 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

AD9834 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 3

Specifications ..................................................................................... 4

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings ............................................................ 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Typical Performance Characteristics ........................................... 10

Terminology .................................................................................... 14

Theory of Operation ...................................................................... 15

Circuit Description ......................................................................... 16

Numerically Controlled Oscillator Plus Phase Modulator ... 16

SIN ROM ..................................................................................... 16

Digital-to-Analog Converter (DAC) ....................................... 16

Comparator ................................................................................. 16

Regulator ...................................................................................... 17

Output Voltage Compliance ...................................................... 17

Functional Description .................................................................. 18

Serial Interface ............................................................................ 18

Powering Up the AD9834 ......................................................... 18

Latency ......................................................................................... 18

Control Register ......................................................................... 18

Frequency and Phase Registers ................................................ 20

Writing to a Frequency Register ............................................... 21

Writing to a Phase Register ....................................................... 21

RESET Function ......................................................................... 21

SLEEP Function .......................................................................... 21

SIGN BIT OUT Pin .................................................................... 22

The IOUT and IOUTB Pins ...................................................... 22

Applications Information .............................................................. 23

Grounding and Layout .................................................................. 26

Interfacing to Microprocessors ..................................................... 27

AD9834 to ADSP-21xx Interface ............................................. 27

AD9834 to 68HC11/68L11 Interface ....................................... 27

AD9834 to 80C51/80L51 Interface .......................................... 28

AD9834 to DSP56002 Interface ............................................... 28

Outline Dimensions ....................................................................... 29

Ordering Guide .......................................................................... 29

Rev. D | Page 2 of 32

Data Sheet AD9834

REVISION HISTORY

3/14—Rev. C to Rev. D

Changes to Table 3 ............................................................................ 7

Deleted Evaluation Board Section ................................................ 29

Changes to Ordering Guide ........................................................... 35

2/11—Rev. B to Rev. C Changes to IDD Parameter, Table 1 .................................................. 5 Changes to FS ADJUST Description, Table 4 ................................ 8 Added Output Voltage Compliance Section................................ 17 Changes to Figure 31 ...................................................................... 23 Changes to Figure 32 ...................................................................... 24 Deleted Using the AD9834 Evaluation Board Section and the Prototyping Area Section ............................................................... 28 Added System Development Platform Section, AD9834 to SPORT Interface Section, Figure 39, and Figure 40; Renumbered Sequentially .............................................................. 29 Changes to XO vs. External Clock Section and Power Supply Section .............................................................................................. 29 Deleted Bill of Materials, Table 19; Renumbered Sequentially .............................................................. 30 Added Evaluation Board Schematics Section and Figure 41 .... 30 Added Figure 42 .............................................................................. 31 Added Evaluation Board Layout Section and Figure 43 ............ 32 Added Figure 44 .............................................................................. 33 Added Figure 45 .............................................................................. 34 Changes to Ordering Guide ........................................................... 35

4/10—Rev. A to Rev. B Changes to Comparator Section ................................................... 15 Added Figure 28 .............................................................................. 16 Changes to Serial Interface Section .............................................. 17

8/06—Rev. 0 to Rev. A Updated Format ................................................................. Universal Changed to 75 MHz Complete DDS ............................... Universal Changes to Features Section ............................................................ 1 Changes to Table 1 ............................................................................ 4 Changes to Table 2 ............................................................................ 6 Changes to Table 3 ............................................................................ 8 Added Figure 10, Figures Renumbered Sequentially ................... 9 Added Figure 16 and Figure 17, Figures Renumbered Sequentially ...................................................................................... 10 Changes to Table 6 .......................................................................... 19 Changes to Writing a Frequency Register Section ..................... 20 Changes to Figure 29 ...................................................................... 21 Changes to Table 19 ........................................................................ 30 Changes to Figure 38 ...................................................................... 28

2/03—Revision 0: Initial Version

Rev. D | Page 3 of 32

AD9834 Data Sheet

SPECIFICATIONS

VDD = 2.3 V to 5.5 V, AGND = DGND = 0 V, TA = TMIN to TMAX, RSET = 6.8 kΩ, RLOAD = 200 Ω for IOUT and IOUTB, unless otherwise noted.

Table 1.

Grade B, Grade C1

Parameter2

Min

Typ

Max

Unit

Test Conditions/Comments

SIGNAL DAC SPECIFICATIONS

Resolution

10

Bits

Update Rate

75

MSPS

IOUT Full Scale3

3.0

mA

VOUT Max

0.6

V

VOUT Min

30

mV

Output Compliance4

0.8

V

DC Accuracy

Integral Nonlinearity

±1

LSB

Differential Nonlinearity

±0.5

LSB

DDS SPECIFICATIONS

Dynamic Specifications

Signal-to-Noise Ratio

55

60

dB

fMCLK = 75 MHz, fOUT = fMCLK/4096

Total Harmonic Distortion

−66

−56

dBc

fMCLK = 75 MHz, fOUT = fMCLK/4096

Spurious-Free Dynamic Range (SFDR)

Wideband (0 to Nyquist)

−60

−56

dBc

fMCLK = 75 MHz, fOUT = fMCLK/75

Narrow Band (±200 kHz)

B Grade

−78

−67

dBc

fMCLK = 50 MHz, fOUT = fMCLK/50

C Grade

−74

−65

dBc

fMCLK = 75 MHz, fOUT = fMCLK/75

Clock Feedthrough

−50

dBc

Wake-Up Time

1

ms

COMPARATOR

Input Voltage Range

1

V p-p

AC-coupled internally

Input Capacitance

10

pF

Input High-Pass Cutoff Frequency

4

MHz

Input DC Resistance

5

MΩ

Input Leakage Current

10

μA

OUTPUT BUFFER

Output Rise/Fall Time

12

ns

Using a 15 pF load

Output Jitter

120

ps rms

3 MHz sine wave, 0.6 V p-p

VOLTAGE REFERENCE

Internal Reference

1.12

1.18

1.24

V

REFOUT Output Impedance5

1

kΩ

Reference Temperature Coefficient

100

ppm/°C

LOGIC INPUTS

Input High Voltage, VINH

1.7

V

2.3 V to 2.7 V power supply

2.0

V

2.7 V to 3.6 V power supply

2.8

V

4.5 V to 5.5 V power supply

Input Low Voltage, VINL

0.6

V

2.3 V to 2.7 V power supply

0.7

V

2.7 V to 3.6 V power supply

0.8

V

4.5 V to 5.5 V power supply

Input Current, IINH/IINL

10

μA

Input Capacitance, CIN

3

pF

Rev. D | Page 4 of 32

Data Sheet AD9834

Grade B, Grade C1

Parameter2

Min

Typ

Max

Unit

Test Conditions/Comments

POWER SUPPLIES

AVDD

2.3

5.5

V

fMCLK = 75 MHz, fOUT = fMCLK/4096

DVDD

2.3

5.5

V

IAA6

3.8

5

mA

IDD6

B Grade

2.0

3

mA

IDD code dependent (see Figure 8)

C Grade

2.7

3.7

mA

IDD code dependent (see Figure 8)

IAA + IDD6

B Grade

5.8

8

mA

C Grade

6.5

8.7

mA

Low Power Sleep Mode

B Grade

0.5

mA

DAC powered down, MCLK running

C Grade

0.6

mA

DAC powered down, MCLK running

1 B grade: MCLK = 50 MHz; C grade: MCLK = 75 MHz. For specifications that do not specify a grade, the value applies to both grades.

2 Operating temperature range is as follows: B, C versions: −40°C to +105°C, typical specifications are at 25°C.

3 For compliance, with specified load of 200 Ω, IOUT full scale should not exceed 4 mA.

4 Guaranteed by design.

5 Applies when REFOUT is sourcing current. The impedance is higher when REFOUT is sinking current.

6 Measured with the digital inputs static and equal to 0 V or DVDD.

RSET6.8kΩIOUT1210-BIT DAC20pFFS ADJUSTAD9834REGULATOR100nFCAP/2.5V10nFREFOUTCOMP10nFAVDDSINROMRLOAD200ΩON-BOARDREFERENCEFULL-SCALECONTROL02705-002

Figure 2. Test Circuit Used to Test the Specifications Rev. D | Page 5 of 32

AD9834 Data Sheet

TIMING CHARACTERISTICS

DVDD = 2.3 V to 5.5 V, AGND = DGND = 0 V, unless otherwise noted.

Table 2.

Parameter1

Limit at TMIN to TMAX

Unit

Test Conditions/Comments

t1

20/13.33

ns min

MCLK period: 50 MHz/75 MHz

t2

8/6

ns min

MCLK high duration: 50 MHz/75 MHz

t3

8/6

ns min

MCLK low duration: 50 MHz/75 MHz

t4

25

ns min

SCLK period

t5

10

ns min

SCLK high duration

t6

10

ns min

SCLK low duration

t7

5

ns min

FSYNC-to-SCLK falling edge setup time

t8 MIN

10

ns min

FSYNC-to-SCLK hold time

t8 MAX

t4 − 5

ns max

t9

5

ns min

Data setup time

t10

3

ns min

Data hold time

t11

8

ns min

FSELECT, PSELECT setup time before MCLK rising edge

t11A

8

ns min

FSELECT, PSELECT setup time after MCLK rising edge

t12

5

ns min

SCLK high to FSYNC falling edge setup time

1 Guaranteed by design, not production tested.

Timing Diagrams

MCLKt1t3t202705-003

Figure 3. Master Clock

FSELECT,PSELECTVALID DATAVALID DATAVALID DATAMCLKt11At1102705-004

Figure 4. Control Timing

D0SCLKFSYNCSDATAD15D14D2D1D15D14t12t7t6t8t5t4t9t1002705-005

Figure 5. Serial Timing Rev. D | Page 6 of 32

Data Sheet AD9834

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter

Ratings

AVDD to AGND

−0.3 V to +6 V

DVDD to DGND

−0.3 V to +6 V

AGND to DGND

−0.3 V to +0.3 V

CAP/2.5V

2.75 V

Digital I/O Voltage to DGND

−0.3 V to DVDD + 0.3 V

Analog I/O Voltage to AGND

−0.3 V to AVDD + 0.3 V

Operating Temperature Range

Industrial (B Version)

−40°C to +105°C

Storage Temperature Range

−65°C to +150°C

Maximum Junction Temperature

150°C

TSSOP Package

θJA Thermal Impedance

143°C/W

θJC Thermal Impedance

45°C/W

Lead Temperature, Soldering (10 sec)

300°C

IR Reflow, Peak Temperature

220°C

Reflow Soldering (Pb-Free)

Peak Temperature

260°C (+0/–5)

Time at Peak Temperature

10 sec to 40 sec

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ESD CAUTION

Rev. D | Page 7 of 32

AD9834 Data Sheet

Rev. D | Page 8 of 32

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

REFOUT

COMP

AVDD

DGND

CAP/2.5V

DVDD

FS ADJUST

IOUT

AGND

VIN

SCLK

FSYNC

SIGN BIT OUT

PSELECT

FSELECT

MCLK

RESET

SLEEP

SDATA

IOUTB

AD9834

TOP VIEW

(Not to Scale)

02705-006

Figure 6. Pin Configuration Table 4. Pin Function Descriptions Pin No. Mnemonic Description

ANALOG SIGNAL AND REFERENCE

1 FS ADJUST Full-Scale Adjust Control. A resistor (RSET) is connected between this pin and AGND. This determines the magnitude

of the full-scale DAC current. The relationship between RSET and the full-scale current is as follows:

IOUT FULL SCALE = 18 × FSADJUST/RSET FSADJUST = 1.15 V nominal, RSET = 6.8 kΩ typical. 2 REFOUT Voltage Reference Output. The AD9834 has an internal 1.20 V reference that is made available at this pin. 3 COMP DAC Bias Pin. This pin is used for decoupling the DAC bias voltage.

17 VIN Input to Comparator. The comparator can be used to generate a square wave from the sinusoidal DAC output. The

DAC output should be filtered appropriately before being applied to the comparator to improve jitter. When Bit

OPBITEN and Bit SIGN/PIB in the control register are set to 1, the comparator input is connected to VIN. 19, 20 IOUT,

IOUTB

Current Output. This is a high impedance current source. A load resistor of nominally 200 Ω should be connected between IOUT and AGND. IOUTB should preferably be tied through an external load resistor of 200 Ω to AGND, but

it can be tied directly to AGND. A 20 pF capacitor to AGND is also recommended to prevent clock feedthrough.

POWER SUPPLY 4 AVDD Positive Power Supply for the Analog Section. AVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling

capacitor should be connected between AVDD and AGND.

5 DVDD Positive Power Supply for the Digital Section. DVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling

capacitor should be connected between DVDD and DGND. 6 CAP/2.5V The digital circuitry operates from a 2.5 V power supply. This 2.5 V is generated from DVDD using an on-board regulator (when DVDD exceeds 2.7 V). The regulator requires a decoupling capacitor of typically 100 nF that is

connected from CAP/2.5 V to DGND. If DVDD is equal to or less than 2.7 V, CAP/2.5 V should be shorted to DVDD.

7 DGND Digital Ground. 18 AGND Analog Ground. DIGITAL INTERFACE AND CONTROL

8 MCLK Digital Clock Input. DDS output frequencies are expressed as a binary fraction of the frequency of MCLK. The

output frequency accuracy and phase noise are determined by this clock. 9 FSELECT Frequency Select Input. FSELECT controls which frequency register, FREQ0 or FREQ1, is used in the phase

accumulator. The frequency register to be used can be selected using Pin FSELECT or Bit FSEL. When Bit FSEL is

used to select the frequency register, the FSELECT pin should be tied to CMOS high or low.

10 PSELECT Phase Select Input. PSELECT controls which phase register, PHASE0 or PHASE1, is added to the phase accumulator output. The phase register to be used can be selected using Pin PSELECT or Bit PSEL. When the phase registers are

being controlled by Bit PSEL, the PSELECT pin should be tied to CMOS high or low. 11 RESET Active High Digital Input. RESET resets appropriate internal registers to zero; this corresponds to an analog output

of midscale. RESET does not affect any of the addressable registers. 12 SLEEP Active High Digital Input. When this pin is high, the DAC is powered down. This pin has the same function as

Control Bit SLEEP12.

Data Sheet AD9834

Pin No.

Mnemonic

Description

13

SDATA

Serial Data Input. The 16-bit serial data-word is applied to this input.

14

SCLK

Serial Clock Input. Data is clocked into the AD9834 on each falling SCLK edge.

15

FSYNC

Active Low Control Input. This is the frame synchronization signal for the input data. When FSYNC is taken low, the internal logic is informed that a new word is being loaded into the device.

16

SIGN BIT OUT

Logic Output. The comparator output is available on this pin or, alternatively, the MSB from the NCO can be output on this pin. Setting Bit OPBITEN in the control register to 1 enables this output pin. Bit SIGN/PIB determines whether the comparator output or the MSB from the NCO is output on the pin.

Rev. D | Page 9 of 32

AD9834 Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

MCLK FREQUENCY (MHz)4.000755V3VTA = 25°CIDD (

mA)3.53.02.52.01.51.00.51530456002705-007

Figure 7. Typical Current Consumption (IDD) vs. MCLK Frequency

4.000.51.01.52.02.53.03.5fOUT (Hz)IDD (mA)TA = 25°C5V3V1001k10k100k1M10M100M02705-008

Figure 8. Typical IDD vs. fOUT for fMCLK = 50 MHz

MCLK FREQUENCY (MHz)SFDR (dBc)–65–60–90–70–75–80–85AVDD = DVDD = 3VTA = 25°CSFDR dB MCLK/50SFDR dB MCLK/70153045607502705-009

Figure 9. Narrow-Band SFDR vs. MCLK Frequency

0–10–20–30–40–50–60–70–80MCLK FREQUENCY (MHz)SFDR (dBc)010203040506070fOUT = 1MHzSFDR dB MCLK/7AVDD = DVDD = 3VTA = 25°C02705-010

Figure 10. Wideband SFDR vs. MCLK Frequency

SFDR (dBc)0–40–80–50–60–70–10–20–3050MHz CLOCK30MHz CLOCKAVDD = DVDD = 3VTA = 25°CfOUT/fMCLK0.0010.010.11.01010002705-011

Figure 11. Wideband SFDR vs. fOUT/fMCLK for Various MCLK Frequencies

MCLK FREQUENCY (MHz)SNR (dB)–60–65–70–50–55–40–451.05.010.012.525.050.0TA = 25°CAVDD = DVDD = 3VfOUT = MCLK/409602705-012

Figure 12. SNR vs. MCLK Frequency Rev. D | Page 10 of 32

Data Sheet AD9834

50010007006506005508507508009009505.5V2.3VTEMPERATURE (°C)–4025105WAKE-UP TIME (

μs)02705-013

Figure 13. Wake-Up Time vs. Temperature

1.1501.1251.1001.1751.2001.2501.225TEMPERATURE (°C)V(REFOUT) (V)LOWER RANGEUPPER RANGE–402510502705-014

Figure 14. VREFOUT vs. Temperature

FREQUENCY (Hz)(dBc/Hz)–150–110–100–120–130–140–160AVDD = DVDD = 5VTA = 25°C1001k10k100k200k02705-015

Figure 15. Output Phase Noise, fOUT = 2 MHz, MCLK = 50 MHz

0.200–40–2002040608010002705-037TEMPERATURE(°C)DVDD (V)0.180.160.140.120.100.080.060.040.02DVDD=3.3VDVDD=5.5VDVDD=2.3V

Figure 16. SIGN BIT OUT Low Level, ISINK = 1 mA

5.51.5–40–2002040608010002705-038TEMPERATURE(°C)DVDD (

V)5.04.54.03.53.02.52.0DVDD=2.3VDVDD=2.7VDVDD=3.3VDVDD=4.5VDVDD=5.5V

Figure 17. SIGN BIT OUT High Level, ISINK = 1 mA

FREQUENCY (Hz)(dB)0–20–50–90–100–80–70–60–40–30–10RWB 100ST 100 SECVWB 300100k02705-016

Figure 18. fMCLK = 10 MHz; fOUT = 2.4 kHz, Frequency Word = 000FBA9 Rev. D | Page 11 of 32

AD9834 Data Sheet

FREQUENCY (Hz)(dB)0–20–50–90–100–80–70–60–40–30–1005MRWB 1kST 50 SECVWB 30002705-017

Figure 19. fMCLK = 10 MHz; fOUT = 1.43 MHz = fMCLK/7, Frequency Word = 2492492

FREQUENCY (Hz)0–20–50–90–100–80–70–60–40–30–1005MRWB 1kST 50 SECVWB 300(dB)02705-018

Figure 20. fMCLK = 10 MHz; fOUT = 3.33 MHz = fMCLK/3, Frequency Word = 5555555

FREQUENCY (Hz)0–20–50–90–100–80–70–60–40–30–100160kRWB 100ST 200 SECVWB 30(dB)02705-019

Figure 21. fMCLK = 50 MHz; fOUT = 12 kHz, Frequency Word = 000FBA9

FREQUENCY (Hz)0–20–50–90–100–80–70–60–40–30–1001.6MRWB 100ST 200 SECVWB 300(dB)02705-020

Figure 22. fMCLK = 50 MHz; fOUT = 120 kHz, Frequency Word = 009D496

FREQUENCY (Hz)0–20–50–90–100–80–70–60–40–30–10025MRWB 1kST 200 SECVWB 300(dB)02705-021

Figure 23. fMCLK = 50 MHz; fOUT = 1.2 MHz, Frequency Word = 0624DD3

FREQUENCY (Hz)(dB)0–20–50–90–100–80–70–60–40–30–10025MRWB 1kST 200 SECVWB 30002705-022

Figure 24. fMCLK = 50 MHz; fOUT = 4.8 MHz, Frequency Word = 189374C Rev. D | Page 12 of 32

Data Sheet AD9834

FREQUENCY (Hz)(dB)0–20–50–90–100–80–70–60–40–30–10025MRWB 1kST 200 SECVWB 30002705-023

Figure 25. fMCLK = 50 MHz; fOUT = 7.143 MHz = fMCLK/7, Frequency Word = 2492492

FREQUENCY (Hz)(dB)0–20–50–90–100–80–70–60–40–30–10025MRWB 1kST 200 SECVWB 30002705-024

Figure 26. fMCLK = 50 MHz; fOUT = 16.667 MHz = fMCLK/3, Frequency Word = 5555555

Rev. D | Page 13 of 32

AD9834 Data Sheet

Rev. D | Page 14 of 32

TERMINOLOGY

Integral Nonlinearity (INL) INL is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale, a point 0.5 LSB

below the first code transition (000 . . . 00 to 000 . . . 01), and full scale, a point 0.5 LSB above the last code transition (111 . . . 10 to 111 . . . 11). The error is expressed in LSBs. Differential Nonlinearity (DNL) DNL is the difference between the measured and ideal 1 LSB

change between two adjacent codes in the DAC. A specified

DNL of ±1 LSB maximum ensures monotonicity.

Output Compliance

The output compliance refers to the maximum voltage that can

be generated at the output of the DAC to meet the specifications. When voltages greater than that specified for the output com-

pliance are generated, the AD9834 may not meet the specifications listed in the data sheet. Spurious-Free Dynamic Range (SFDR)

Along with the frequency of interest, harmonics of the fundamental frequency and images of these frequencies are

present at the output of a DDS device. The SFDR refers to the largest spur or harmonic present in the band of interest. The wideband SFDR gives the magnitude of the largest harmonic or spur relative to the magnitude of the fundamental frequency in the 0 to Nyquist bandwidth. The narrow-band SFDR gives the

attenuation of the largest spur or harmonic in a bandwidth of ±200 kHz about the fundamental frequency. Total Harmonic Distortion (THD) THD is the ratio of the rms sum of harmonics to the rms value of the fundamental. For the AD9834, THD is defined as 1

2 3456

V

V VVVV

THD

2 2222

log 20

where V1 is the rms amplitude of the fundamental and V2, V3,

V4, V5, and V6 are the rms amplitudes of the second harmonic

through the sixth harmonic. Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency. The value for SNR is expressed in decibels. Clock Feedthrough There is feedthrough from the MCLK input to the analog

output. Clock feedthrough refers to the magnitude of the MCLK signal relative to the fundamental frequency in the

output spectrum of the AD9834.

Data Sheet AD9834

THEORY OF OPERATION

Sine waves are typically thought of in terms of their magnitude form a(t) = sin (ωt). However, these are nonlinear and not easy to generate except through piecewise construction. On the other hand, the angular information is linear in nature, that is, the phase angle rotates through a fixed angle for each unit of time. The angular rate depends on the frequency of the signal by the traditional rate of ω = 2πf.

MAGNITUDEPHASE+10–12p02π4π6π2π4π6π02705-025

Figure 27. Sine Wave